2022年是晶体管发明75周年。1947年,肖克利、巴丁和布拉坦在贝尔实验室完成了这项重大发明,开创了一个巨大的半导体电子产业,已经影响到我们生活的方方面面。我记得,作为一名年轻的工程师,当我进入新泽西州默里山的贝尔实验室大楼工作时,看到墙上的第一个晶体管,我受到了启迪。

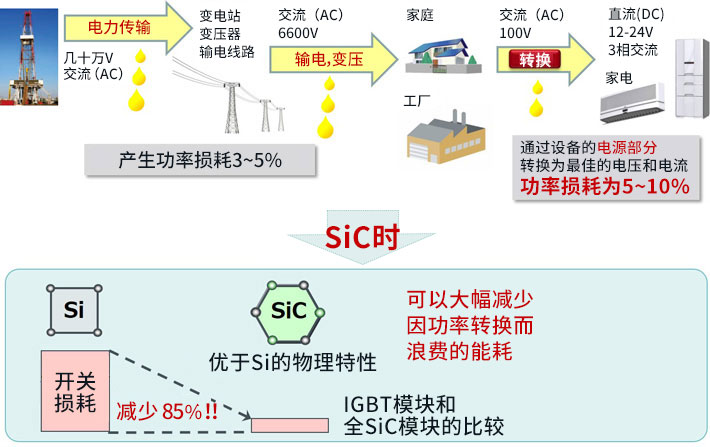

早期的晶体管是用锗制成的,但在1960年左右,硅成为首选的半导体材料,因为其更大的带隙可以降低漏电流。对于高电压和高电流条件下的高功率应用,硅功率MOSFET和IGBT被开发、优化并应用到更多的系统中。事实上,由于硅功率器件的低成本批量生产、优异的起始材料质量、易于制造以及经验证的可靠性和耐用性,硅功率器件如今已在电力电子领域根深蒂固。尽管硅功率器件享有器件/电路设计传统和大量精简的制造基础设施,但它们正在接近硅的工作极限。硅相对较低的带隙和临界电场导致高传导和开关损耗,并危及高温性能。因此,其它有前途的材料系统已被探索用于高效的高功率应用。

碳化硅是一种IV–IV宽带隙化合物材料,Si和C原子之间具有强化学键,具有高硬度、化学惰性和高导热性。在SiC中,宽的n型和p型注入掺杂范围以及相对薄的SiO2是可能的。相对于硅,SiC表现出高3倍的宽带隙、7倍至9倍临界电场强度和2.5倍的导热率。这些有利的材料特性,使高效的功率器件具有更小的形状因数和简化的冷却,表征了优于Si的性能演变。这一点很早就得到了认可,并导致了对SiC的重大投资,最终于2001年推出了第一个商用SiC肖特基势垒二极管。2010年业界推出了首个商用SiC MOSFET,并于2018年开始在电动汽车中采用商用SiC MOSFET。

鉴于SiC在高功率应用中的显著优势,自20世纪80年代以来,业界一直致力于开发SiC材料和器件技术。在新型半导体材料上制造的功率器件商业化的重要先决条件包括大直径、低缺陷衬底和高质量外延层生长的可用性,利用现有的、可扩展的硅晶圆厂基础设施的制造工艺,器件优越性的展示和可与现有半导体器件媲美的可靠性、耐用性。

纯SiC晶体是通过Lely升华技术生长的。晶体主要是6H-SiC,但包括其它多型体。1978年,Tairov和Tsvetkov发明了一种可复制的SiC晶块生长方法;该方法涉及将6H-SiC籽晶插入升华生长炉中并控制从SiC源到籽晶的质量传输。这种生长方法被称为改进的Lely法或种子升华法,由几个小组改进并进一步发展,以获得具有大直径和降低缺陷密度的SiC晶块。今天,150mm SiC衬底主要用于生产并扩展到200mm,但规模较小。通过积极处理基底面位错(最后一个主要的灾难性缺陷),杀手级缺陷密度已大幅降低。

1987年,Kuroda等人在1500˚C至1650˚C的相对较低生长温度下,在离轴衬底上展示了高质量SiC CVD同质外延生长。这是4H-SiC衬底上的标准外延技术,由于其在垂直方向上具有较高的电子迁移率、较低的本征载流子浓度和较低的掺杂剂电离能,因此对于功率器件来说是优选的。水平热壁(Kordina等人,1993)和行星热壁反应器是非常成功的SiC外延生产平台。SiC晶片具有硅面和碳面。由于更好的栅极氧化物质量,器件通常在硅面上制作。目前,SiC晶片占SiC器件总成本的45%至65%,这是其独特复杂制造工艺的结果。因此,业界正在探索几种颠覆性的SiC晶片技术,包括工程衬底和更有效的晶锭利用。

许多成熟的硅工艺已经成功地转移到SiC上。然而,SiC材料的特性需要优化特定工艺,包括晶片减薄、干蚀刻、热注入和退火、低电阻率欧姆接触形成、高质量栅极氧化物界面、透明晶片的计量、检查以及相对缺乏平坦度的晶片处理。SiC器件制造商已经开发了几种高产量制造工艺IP,与硅不同,它们在设计和加工方面都有竞争。如今,SiC制造业已经成熟,其晶圆厂基础设施与Si的基础设施相当。集成SiC器件制造商与代工制造厂和无晶圆厂共存,设计公司提供可获得许可的专有技术和知识产权,以加速进入市场。

从历史角度来看,Matus等人和Urushidani等人分别于1991年和1993年发布了1kV p-n和肖特基势垒二极管。对于晶体管,Palmour等人于1993年展示了第一个垂直沟槽MOSFET,普渡大学库珀教授团队于1997年展示了首个平面双注入功率MOSFET。

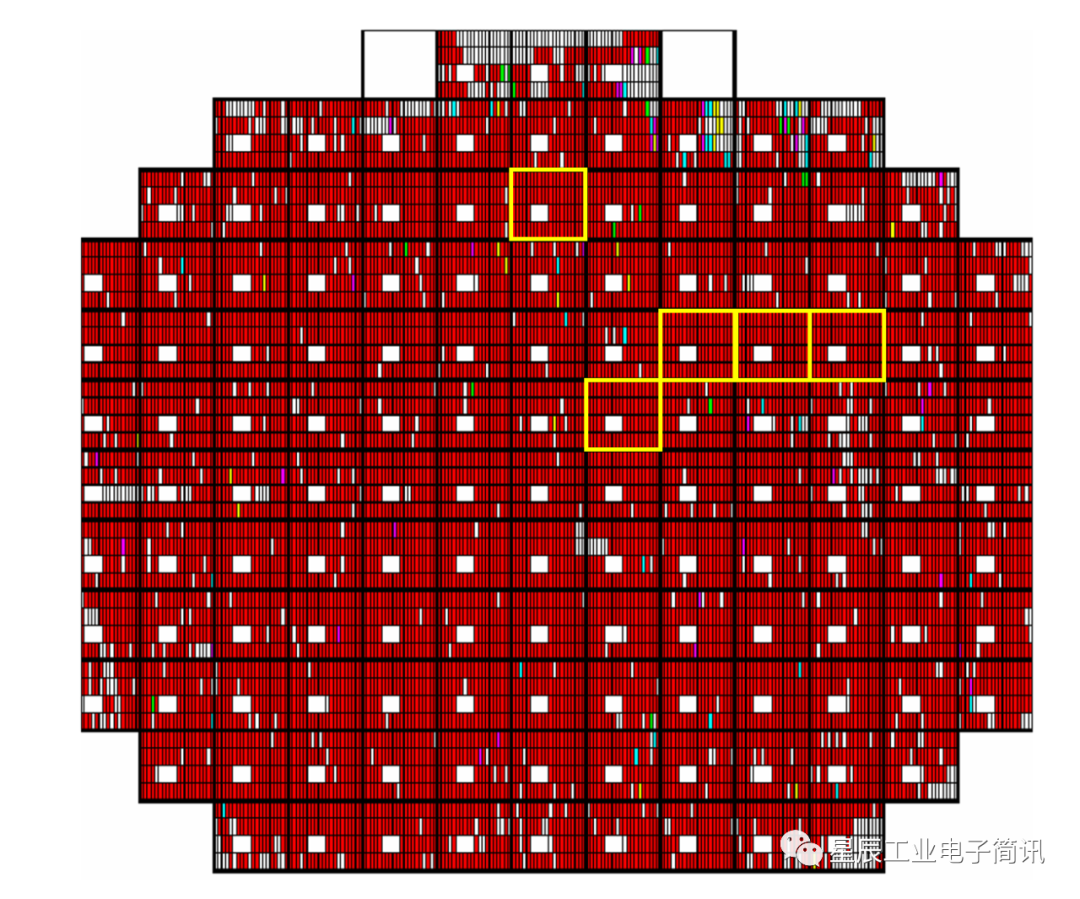

我的SiC之旅始于2000年代初,当时我正在为RF雷达功率放大器制造SiC JFET。他们的器件面积为1.2×10–3 cm2,包括位于晶片边缘的JFET,良率达到92%(图1)。小的RF器件面积减轻了缺陷对成品率的不利影响。当时的晶圆直径为3英寸,我的设计由134个掩模版组成。制造用于功率应用的0.27cm2尺寸器件将需要整个掩模版。在图1的晶片图中所示的134个掩模版中,只有黄色所示的五个掩模版没有失效器件,因此0.27cm2器件的良率为3.7%,今天依然如此。随着SiC器件的面积增加,加工缺陷对良率具有不成比例的灾难性影响。

图1: JFET栅极到源极击穿电压的晶片图,显示92%的良率,这包括位于晶片边缘JFET的贡献。好的器件显示为红色;故障器件显示为灰色。每个掩模版中的大的、均匀分布的白色正方形包含在自动探针测试中未测量的实验器件和表征结构。只有五个方框(用黄色轮廓表示)内不包含故障器件。

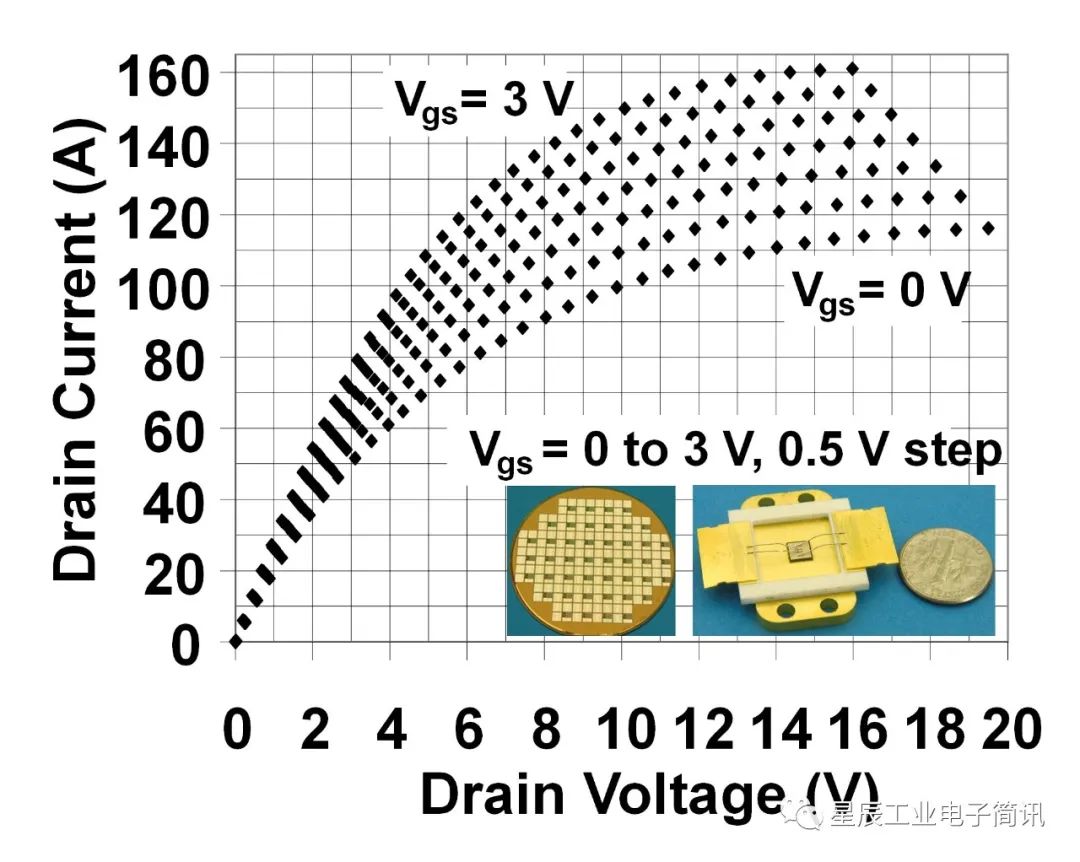

早在2006年,我就制造了1200V 0.19-cm2 JFET,能够在2V的正向压降和2.5V的栅极偏置下输出54A电流(图2)。这促使我继续致力于SiC的商业化。事实上,我的0.19平方厘米JFET在日本大津举行的2007年SiC及相关材料国际会议上获得了“器件新纪录”。

图2:2006年在3英寸晶圆上制造的0.19-cm2 4H-SiC JFET的代表性正向电流特性。该器件在2V的正向压降和2.5V的栅极偏置下输出54A的电流。它能够阻挡1270V的电压。

当引入一种有前途的技术时,需要一种合适的大规模应用来实现成本削减。对于SiC而言,混合动力汽车和电动汽车构成了大规模商业化应用,推动了我们目前正在经历的SiC爆炸式增长。根据Yole Group的预测,到2027年,功率SiC器件将成为63亿美元的市场,其中汽车占50亿美元。总体而言,预计到2027年,SiC将占据功率器件市场的20%以上。

在未来五年中,复杂和劳动/时间密集型SiC衬底的生长将继续推动垂直集成、“飘移”式创新(每晶块产生更多衬底)以及工程衬底的进步。在200毫米晶圆接近每平方厘米的成本和缺陷密度标杆之前,150毫米晶圆将占据超过50%的市场份额。

非CMOS兼容工艺,如欧姆接触形成、热注入和退火、衬底薄化和金属化将接近标准化。晶片平整度将提高,便于制造。栅极氧化物优化将增加迁移率并降低阈值电压不稳定性。由于其更高的复杂性,沟槽MOSFET结构对于额定电压低于1700V的器件更有意义,因此不会成为SiC制造的公司的选择。由于工艺IP使SiC制造复杂化,IDM将继续主导生产。在成熟、完全折旧的硅晶圆厂中制造SiC已成为一种经济高效的模式,并将继续向前发展。缺陷密度降低将使得更大的SiC器件电流额定值更接近Si的额定值。650至1700V SiC MOSFET的价格将比硅器件高1.5至2倍。然而,在汽车和光伏等主要应用中,系统级成本节约将超过采购SiC器件的成本增加。

编辑:黄飞

-

电动汽车

+关注

关注

156文章

12067浏览量

231100 -

混合动力汽车

+关注

关注

3文章

189浏览量

26570 -

晶体管

+关注

关注

77文章

9682浏览量

138079 -

SiC

+关注

关注

29文章

2804浏览量

62605 -

碳化硅

+关注

关注

25文章

2748浏览量

49017

原文标题:从硅传统器件到高效SiC功率器件的演进

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高效SiC功率器件的演进

高效SiC功率器件的演进

评论