在前面我们讨论了,第一种使用隔离电阻来补偿容性负载的方法。虽然Riso电路设计和使用都较简单,但它在精密电路里有一大缺点,Riso上的压降与输出电流或输出负载有关,并且Riso造成的压降可能影响输出信号的准确度,如右图所示对于一个10mV的输出信号由于250Ω的输出负载,而产生超过3mV的压降也就是会带来30%的误差。

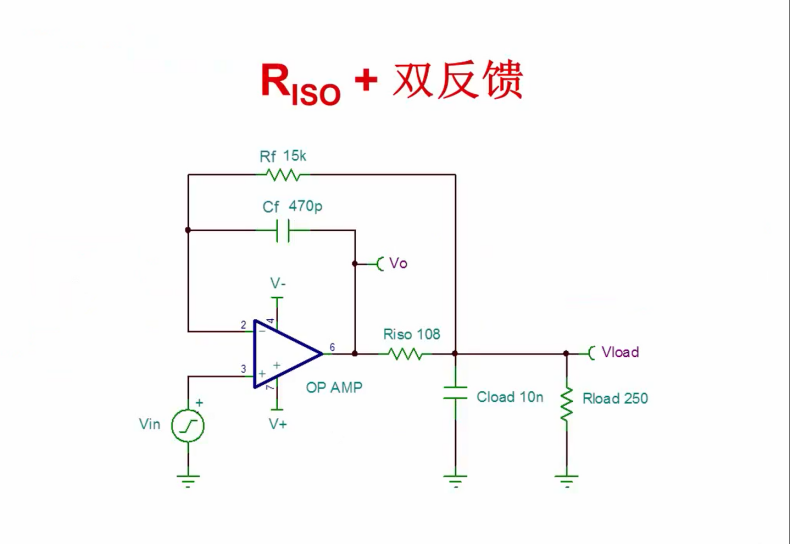

为了解決Riso产生压降的问题,我们可以使用这里所展示的Riso+双反馈的电路。

Riso+双反馈的工作原理,可以用DC和AC等效电路来分析。在DC时,反馈电容Cf是开路的,并且Rf闭合了包含Riso的反馈环路。因为现在Riso是在运放的反馈环路里面的,运放输出会增大来补偿Riso的压降,所以负载电压Vload会等于Vin。

在AC频率时Cf是短路的,当这个发生时Rf可以被认为是开路的,因为Cf的阻抗Zcf会远远小于Rf的阻抗,因此在AC时,这个电路看起来会和标准的Riso电路一样。

这个电路的第一个设计步骤,是选择Riso,选择方法与我们之前所说的方法1,Riso中选择Riso的方法相同。使得Aol曲线上等于20dB的频率点上产生一个零点。然后Rf可以选择为任意一个大于100*Riso的值,以防止其与Riso相互作用。最后一步是在图片左下方所示的,范围内选择Cf的值,使用这个范围内的值,可以保证两个反馈路径Rf和Cf永远不会产生谐振而导致不稳定。更小的Cf值会有更快的建立时间settlingtime,但以一定负载范围内的过冲为代价。

从结果可见,运放输出和负载电压到达稳定值,而没有过大的过冲与振铃,说明这是一个稳定的系统,为克服Riso压降而增大的Vo在这里也可以清楚地看到。

当Riso+双反馈电路解决Riso电路DC精度问题的同时,它也带来一些缺点。如这里所示,一个Riso电路在合理的大范围容性负载的瞬态响应变化下,通常会保持稳定。Riso+双反馈电路对输出电容的变化容忍度没有那么大,电路易受到容性负载的变化而变得不稳定。因此Riso+双反馈电路适用于输出电容确定,并且不会显著变化的场合。Riso+双反馈方法通常会导致建立时间比Riso电路更慢。

当Riso+双反馈电路解决Riso电路DC精度问题的同时,它也带来一些缺点。如这里所示,一个Riso电路在合理的大范围容性负载的瞬态响应变化下,通常会保持稳定。Riso+双反馈电路对输出电容的变化容忍度没有那么大,电路易受到容性负载的变化而变得不稳定。因此Riso+双反馈电路适用于输出电容确定,并且不会显著变化的场合。Riso+双反馈方法通常会导致建立时间比Riso电路更慢。

原文标题:运放电路双反馈Riso稳定性补偿方法

文章出处:【微信公众号:硬件三人行】欢迎添加关注!文章转载请注明出处。

-

硬件

+关注

关注

13文章

3666浏览量

69225

原文标题:运放电路双反馈Riso稳定性补偿方法

文章出处:【微信号:yingjiansanrenxing,微信公众号:硬件三人行】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

国巨电阻长期稳定性对工业控制影响?

三星电容温度系数如何影响电路稳定性?选型方法?

运放电路电容自举反馈的时间问题

解析ADA4610-1 JFET运放:高性能与稳定性的完美结合

探秘ADA4522-2运放:高精度与稳定性的完美结合

三星电容的温度特性对电路稳定性有何影响?

Neway微波的稳定性优势

如何保证合金电阻的稳定性与精度?

有哪些方法可以验证电能质量在线监测装置的稳定性?

运放电路双反馈Riso稳定性补偿方法

运放电路双反馈Riso稳定性补偿方法

评论