芯行纪科技有限公司(以下简称“芯行纪”)资深业务总监陶然受邀出席中国集成电路设计业2022年会暨厦门集成电路产业创新发展高峰论坛(ICCAD 2022)并发表演讲,着重分享了在EDA领域用机器学习技术能够带来的变革性进展,以及详细的相关技术创新点和在实际应用中的精彩表现。

演讲实录(内容为节选)

芯行纪在今年8月份推出了自主研发的首款智能化的EDA软件AmazeFP。在大家看来可能它就是一个做自动floorplan的工具,但是实际上它内部包含的技术远远不只是floorplan这么简单。

首先它是一个machine-learning-driven的工具,具备AI的预测功能。另外,它除了完成floorplan的功能性以外,还包含了global placement的引擎和global routing的引擎,所以它可以更好地预测timing、power和congestion。通过这样的软件,用户可以非常容易的自动化地得到类似于有经验的工程师手动摆放出来的floorplan结果。

大家都知道floorplan其实是整个数字后端流程的第一步,也是非常重要的一步,因为floorplan的质量会影响到我们芯片的PPA最终能够达到的高度。因此数字芯片设计公司往往都会用它最有经验的人来做floorplan工作。而现在我们将可以通过AmazeFP自动完成这一工作。如果芯片设计公司没有那么多有经验的工程师,那它完全就可以通过AmazeFP自动产生得到比拟甚至超过有经验工程师摆放出来的floorplan。如果设计公司已经有一些非常资深的工程师,AmazeFP也可以把他们从繁琐的手动调整、探索的工作中解放出来,让他们把精力花在更有明确性的选择方案和其他更多有创造性的工作上,AmazeFP工具的一大意义就在于此。

另外,图形界面是我们产品的一个亮点,所有见过这个图形界面的客户都跟我们反馈说,这个界面和现在主流的工具比较起来要漂亮非常多,这也说明我们的研发不光是想在内核上做一个引领者,我们也是“外貌协会”的,在外观上也要做一个引领者。这个外观除了好看以外,还具备好用(easy-of-use)的特性,这样才能做到内外兼修。

接下来再给大家分享AmazeFP在实际应用中的一些成绩。

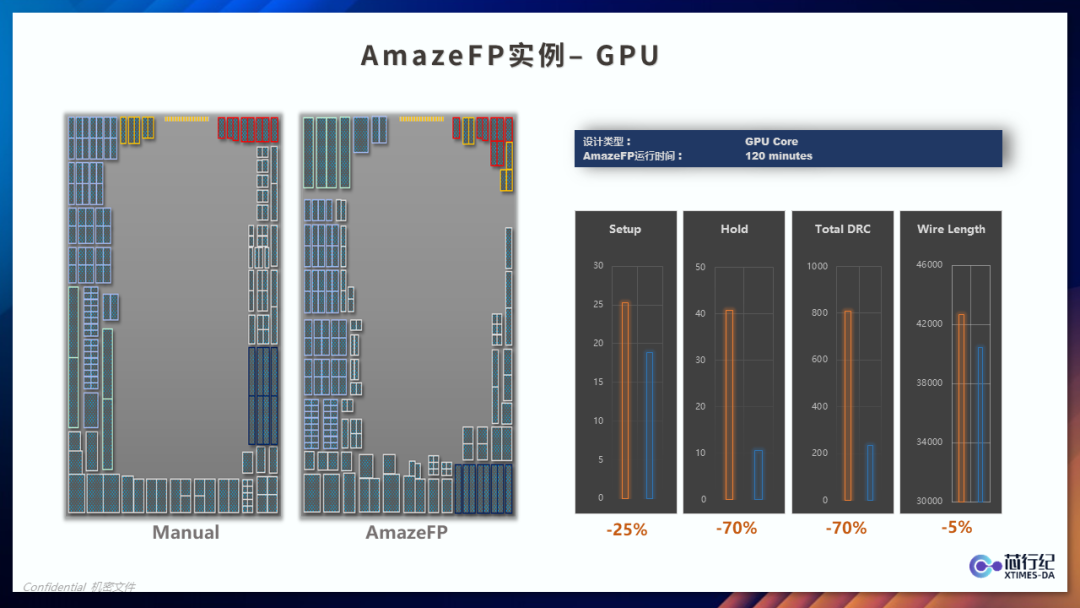

首先大家可以看一下这个例子,这是一个GPU的design。大家可以看到左边的这幅图是有经验的工程师手动摆放出来的floorplan,右边这幅图是AmazeFP自动摆放出来的。做过后端设计的人应该都很清楚,像这样的floorplan,基本上需要一个有经验的工程师花费一周左右的时间,而AmazeFP只需要两个小时就能完成,这大幅度提高了工作效率。

另外很有意思的一点,是工程师和AmazeFP工具的一些选择其实在有些地方是非常相似的,比如说大家看到的红色的这些block,不管是工程师还是AmazeFP,都倾向于把它放在右上角,深蓝色的部分都倾向于放在右下角,所以说工具和工程师其实对某些地方的认知是非常一致的,但在其他一些地方工具采取的解决方案跟我们工程师不一样。

大家都知道一个GPU的设计,一般来说它的时序比较容易满足,而因为它规模比较大,runtime比较长,另外绕线资源会比较紧张,所以它最大的问题应该是congestion。从AmazeFP通过machine learning预测自动摆放的floorplan来看,绕线后的total DRC会有非常大的减少。

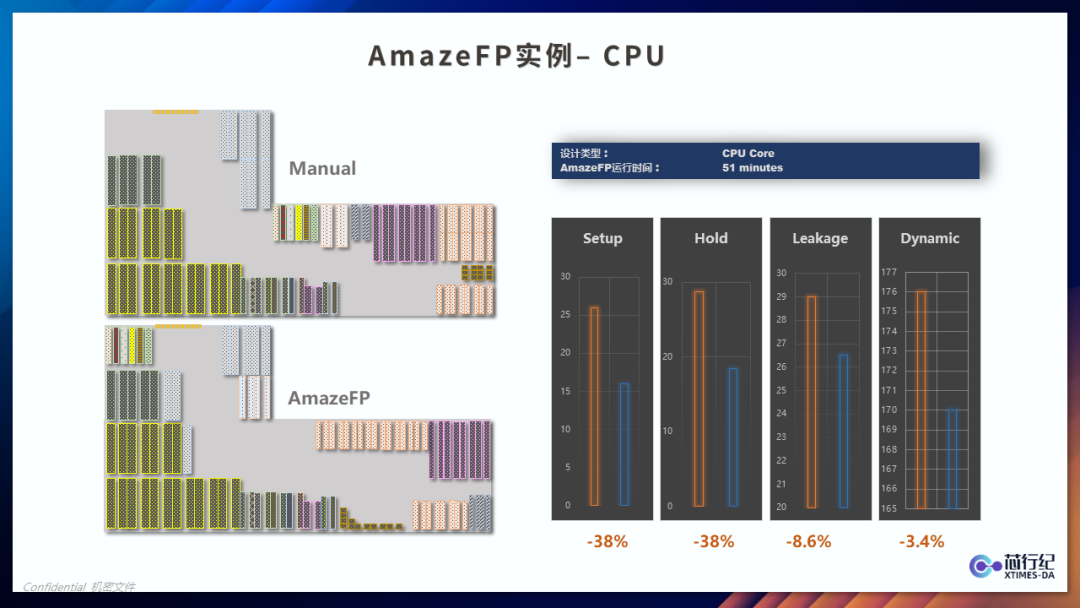

接下来是一个CPU的例子。大家对CPU所追求的就是更好的PPA,消费类电子的公司会把CPU的PPA看成是非常重要的一个指标,因为它可能直接关系到产品面市时候的市场定位和定价,所以大家都会把资源重用在CPU core的hardening上。

我们可以看到这个实例中,左边上面是有经验的工程师手动摆放出来的floorplan,一般有经验的工程师可能需要1~2周时间,经过大约十几二十轮的迭代,才可以最终定下来这样的floorplan。而AmazeFP自动摆放花费的时间大概在50分钟左右,就可以实现同样的PPA效果,甚至更好。

大家可以感受一下我们工程师和工具自动摆放 floorplan的差异性在哪里。对比看一下上下两个floorplan,两个floorplan里靠左边的绿色和黄色的block,工程师和AmazeFP选择是类似的,但是有些地方很明显不同。大家可以看到上面这个floorplan右上角的位置,一看就是我们人为手动的选择,为什么?因为这一组block肯定是相同类型的,通过我们的直觉,肯定是把它们放在一起,因为它的连接关系、timing path肯定强相关,放在一起肯定是没错,这样摆放也符合人的审美。但是这样做会不会是最好的选择呢?不见得。

我们可以看一下AmazeFP的选择是怎样的。工具把这一组同一类型的block拆成了左右的两个分布,很明显这个是机器的选择,因为它不在乎人类审美的要求,它完全是从数学上去寻找一个最优解。从最终的结果我们可以看到,工具的选择对PPA会更好,我们基于工具自动摆放出来的floorplan,可以得到更好的timing和power。

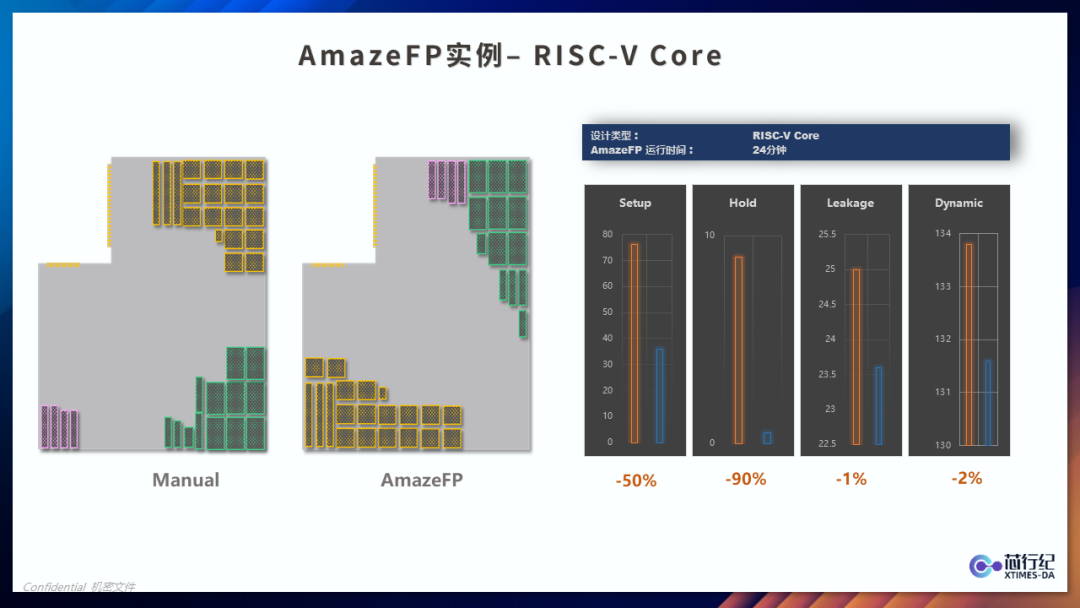

接下来这个design也是CPU core,是RISC-V的。这个相对来说简单一点,通过有经验的工程师摆放差不多要一周多的时间,AmazeFP二十几分钟就可以完成。

从分组上看,工程师和AmazeFP的分组几乎一样,但是摆放的位置差不多旋转了180度。基于这样的调整之后,我们可以看到auto floorplan出来的结果在timing和power上面也都有明显的改善。

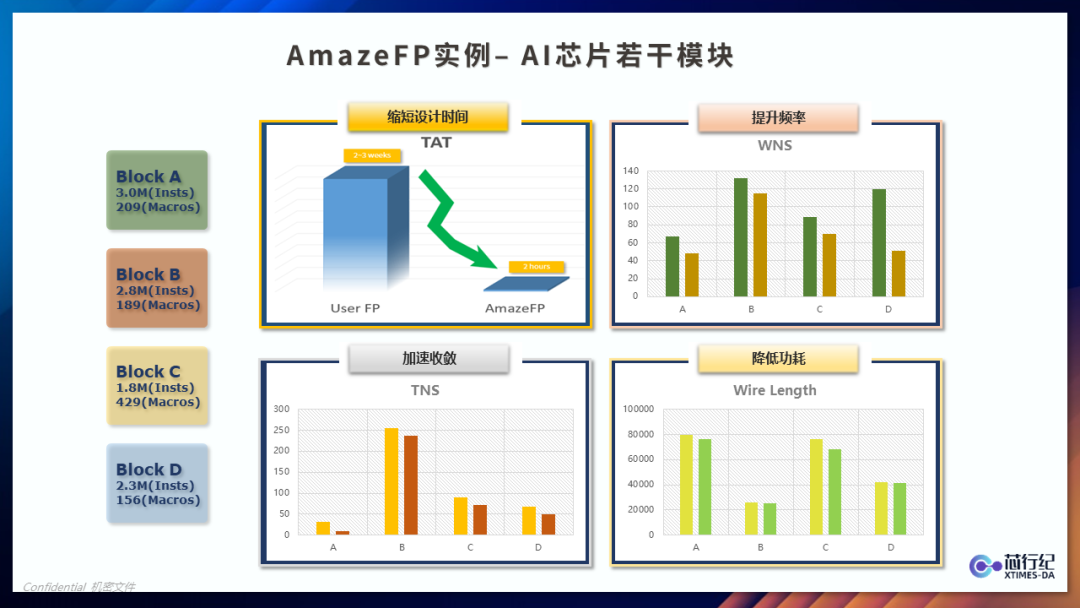

除了刚才提到的这些high performance core之外,我们其实在一些其它类型的block上也进行了尝试,大家可以看到无一例外的PPA都会有明显的改善,并且在设计时间上会有大幅度的节省。

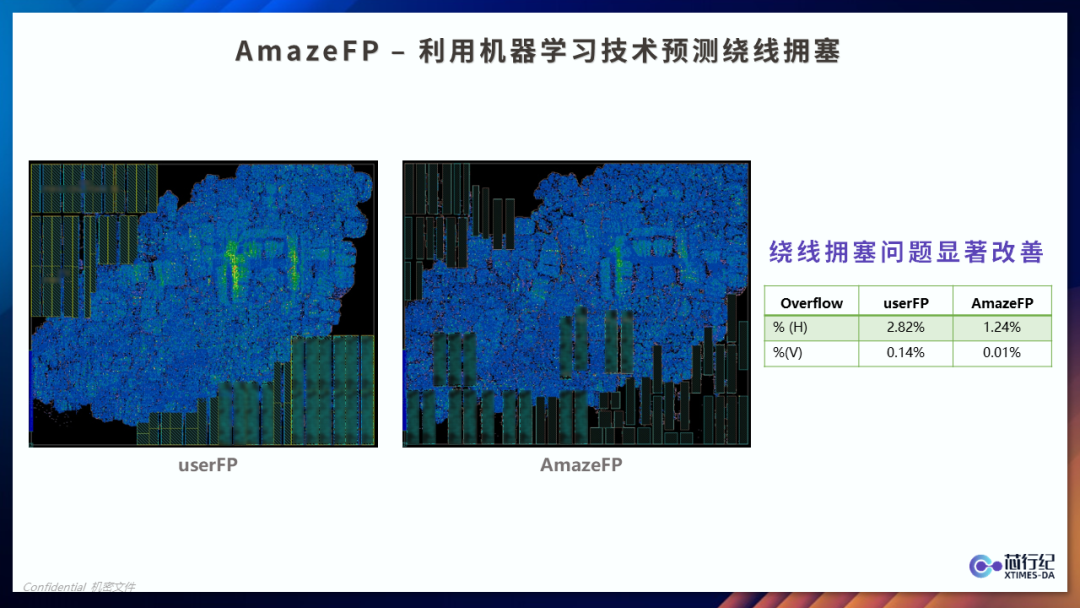

除了用机器学习可以得到更好的PPA和更快的runtime之外,我们还可以利用机器学习去预测绕线。因为在做floorplan的时候,其实很多后续的信息都是不完整的,所以说我们可以通过machine learning做一个预测,预估后面绕线的实际结果。大家可以看到这两个floorplan,很明显地,AmazeFP出来的结果中,绕线的问题会得到明显改善。

通过以上案例,我们想让各位知道,机器学习技术和EDA工具结合以后产生了巨大的威力,芯行纪作为一个专注数字后端技术的EDA公司,期望在人工智能技术和云技术上面能够做出更多的尝试并取得成绩。我们从最初规划工具时,在做最底层的软件架构的时候,就开始考虑了这些方向,并从第一行代码开始,我们就在执行这些想法,现在我们看见了很好的结果。

未来的一到两年内,大家会陆续看到更多Amaze系列的产品问世,我们也希望通过有AI和Cloud技术加持的产品,能够让大家眼前一亮。作为一家国内的EDA公司,我们希望并积极地会与IC设计公司和foundry进行更深入的合作,为集成电路事业贡献自己的一份力量。

关于芯行纪

芯行纪科技有限公司(X-Times Design Automation Co., LTD)汇聚全球杰出EDA技术支持和研发精英,着力于自主研发符合3S理念(Smart、Speedy、Simple)的数字实现EDA平台,包含新一代布局布线技术,同时提供高端数字芯片设计解决方案,可大幅度提升芯片设计效率,并助力实现芯片一次性快速量产,在人工智能、智能汽车、5G、云计算等集成电路领域为众多合作伙伴的高速发展和产业腾飞保驾护航。

审核编辑:汤梓红

-

集成电路

+关注

关注

5388文章

11547浏览量

361843 -

eda

+关注

关注

71文章

2759浏览量

173279 -

机器学习

+关注

关注

66文章

8418浏览量

132647

原文标题:用机器学习技术实现EDA工具的智能化变革

文章出处:【微信号:gh_2894c3fc5359,微信公众号:芯行纪】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

eda在机器学习中的应用

【书籍评测活动NO.51】具身智能机器人系统 | 了解AI的下一个浪潮!

EDA在物联网设计中的应用

安防智能化包含哪些系统

【⌈嵌入式机电一体化系统设计与实现⌋阅读体验】+《智能化技术在船舶维护中的应用探索》

数字孪生技术驱动未来智能化发展

为昕原理图设计EDA软件(Jupiter)试用

AI算法的本质是模拟人类智能,让机器实现智能化

创想焊缝跟踪系统适配欢颜机器人真正实现焊接自动化和智能化

用机器学习技术实现EDA工具的智能化变革

用机器学习技术实现EDA工具的智能化变革

评论