大数据时代,每个人的搜索框在某种程度上都代表着这个人的所思所想。如果将时间放长,样本量放大,那么一份年度搜索关键词就会呈现出了这个世界上绝大部分人是如何走过这一年的

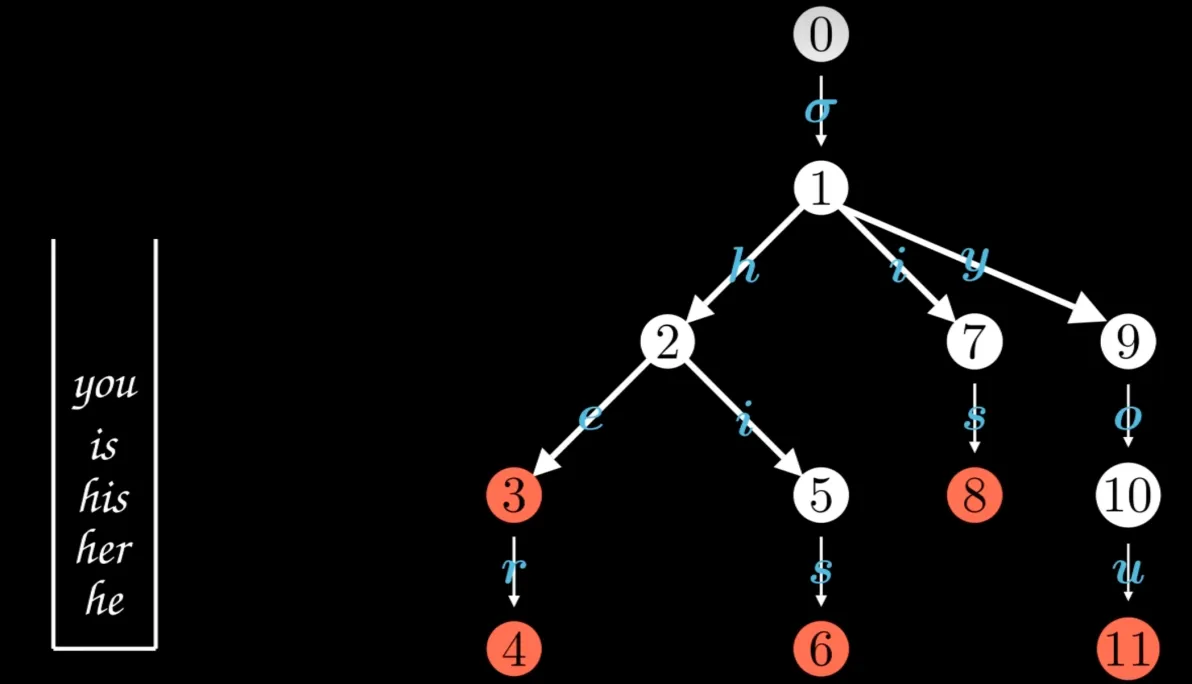

搜索产品型号与关键词

搜索

今天,咱们也将分享这样一份搜索趋势数据,看看各位小伙伴在ADI全平台上搜索的热门关键词,都在关心什么样的产品,学习什么样的资料,咨询什么样的问题?

关键词:杨老师模拟课

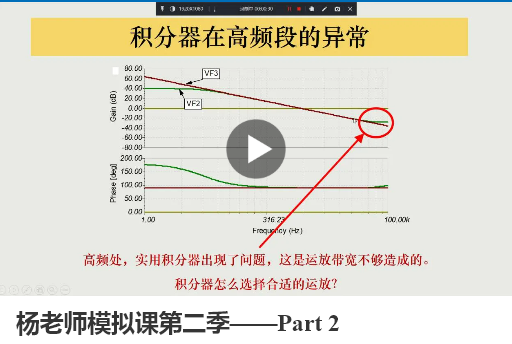

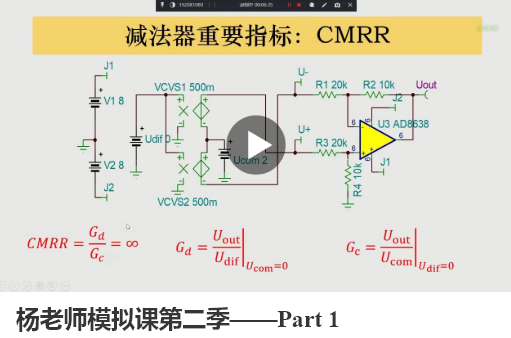

“杨老师模拟课”是西安交通大学电气工程学院教授、博士生导师、工学博士杨建国在多年的执教与科研时间中,积累的问题与详细解答,并从中精选了最具代表性的10个问题,做出了10堂视频课,结合PPT,细致逐步讲解。

“杨老师模拟课”是西安交通大学电气工程学院教授、博士生导师、工学博士杨建国在多年的执教与科研时间中,积累的问题与详细解答,并从中精选了最具代表性的10个问题,做出了10堂视频课,结合PPT,细致逐步讲解。

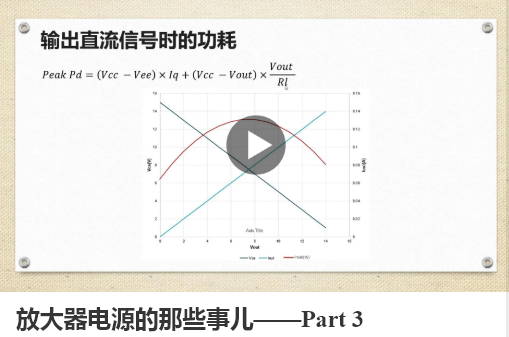

放大器是一种有源器件,需要供电才能工作,电源的不同选择和设置也会对放大器参数性能产生影响,因此,不管您是已入职场的设计人员,还是在正在学习电路设计的学生,都应该对放大器电源有更多的了解。《放大器电源的那些事儿》由ADI放大器应用工程师录制,合计22小节内容,主要介绍放大器的电源应用的相关注意事项。

放大器是一种有源器件,需要供电才能工作,电源的不同选择和设置也会对放大器参数性能产生影响,因此,不管您是已入职场的设计人员,还是在正在学习电路设计的学生,都应该对放大器电源有更多的了解。《放大器电源的那些事儿》由ADI放大器应用工程师录制,合计22小节内容,主要介绍放大器的电源应用的相关注意事项。

关键词:放大器设计问答

ADI的工程师们在与客户的长期沟通过程中,收到并解答了大量关于放大器的使用问题,很多问题都颇具代表性,为了让更多工程师能理解和使用好放大器这一器件,ADI特别梳理了相关内容,挑选出75个典型的常见问题并整合出一本《放大器设计问答》。

关键词:PCB设计秘籍

本书以ADI公司官方网站、ADI中文技术论坛、亚德诺半导体官方微信公众号的PCB设计内容资料为基础资料来源,按PCB布局布线、散热技巧、接地指导、抗扰度等角度进行分类整理,针对在各种器件、应用环境下,提供了一些实用的PCB设计指导以及常见问题解答。

公众号热门文章链接:

混合信号PCB布局设计的基本准则

电源PCB上电感应该如何安放?

使用高速转换器时应遵循哪些重要的PCB布线规则?

......

关键词:电流测量

ADC可在各类应用中实现精确可靠的转换性能,ADI公司拥有业界最齐全的数据转换器产品系列,DAC涵盖8位至24位,面向工业自动化、可编程逻辑控制器、光收发器、数据采集等各种应用,能够提供精确可靠、无与伦比的转换性能和价值;ADI推出电子书《ADC和DAC的基本架构》,旨在梳理ADC和DAC使用中相关的基础要点以及构架示例。

关键词:电源管理

ADI高性能电源管理解决方案通过先进的设计和封装技术满足严格的电源要求,包括出色的功率密度、超低噪声技术和出色的可靠性。ADI低复杂度的电源管理解决方案得到业界最全面的、从头至尾的电源设计工具套件以及高度可配置的电源互连解决方案的支持,可帮助我们的客户缩短产品上市时间,同时提供出色的性能。

相关链接:电源管理相关技术资料

关键词:精密信号链

精密技术信号链允许在各种设计权衡之间轻松变换,以为应用创建优质的终端解决方案。利用ADI公司完整的精密技术信号链加速技术选择和实施,这些信号链汇集了50多年的洞察力和专业知识。结合适当的工具、专门开发的知识库和可定制的解决方案,ADI的精密技术信号链能够轻松采用。相关链接:

精密技术信号链允许在各种设计权衡之间轻松变换,以为应用创建优质的终端解决方案。利用ADI公司完整的精密技术信号链加速技术选择和实施,这些信号链汇集了50多年的洞察力和专业知识。结合适当的工具、专门开发的知识库和可定制的解决方案,ADI的精密技术信号链能够轻松采用。相关链接:精密信号链平台相关解决方案

关键词:电机驱动与运动控制

运动控制是智能制造的核心构建模块,可实现高度灵活的高效制造。智能运动控制融合了精确反馈、先进感知、高性能控制和无缝连接技术,可提供确定性运动解决方案。ADI专注于为电机驱动与运动控制提供新技术和解决方案,帮助客户实现下一代先进和可持续的电机驱动与运动控制。

相关链接:电机驱动与运动控制相关解决方案

各位小伙伴,这些关键词你是否也搜索过呢?

快来回顾一下,分享你在今年搜索最多的关键词!以及它们是否成为了你的助力,为你的设计再添一份创新呢?

各位小伙伴,这些关键词你是否也搜索过呢?

快来回顾一下,分享你在今年搜索最多的关键词!以及它们是否成为了你的助力,为你的设计再添一份创新呢?

原文标题:ADI年度关键词曝光,这些你肯定搜索过!

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

-

亚德诺

+关注

关注

6文章

4680浏览量

15982

原文标题:ADI年度关键词曝光,这些你肯定搜索过!

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2023国产汽车芯片关键词:过车规、落地、降价

大臂展、大负载、具身智能……大族机器人2024年度关键词回顾

中国信通院魏亮:2024人工智能产业十大关键词解读

浅析2024年半导体行业的两大关键词

这些关键词带你了解智算中心高性能网络

中国信通院发布“2024云计算十大关键词”

全网热搜的关键词,芯讯通也被@了

5G RedCap贯通行动政策文件发布,这些关键词值得关注

微软Edge浏览器将引入PDF阅读器,实现关键词自动生成功能

苹果搜索广告将在70多个国家和地区上线,包括拉美地区

深开鸿用三个关键词,为你解读《2023 OpenHarmony 年度运营报告》

ADI年度关键词曝光,这些你肯定搜索过!

ADI年度关键词曝光,这些你肯定搜索过!

评论