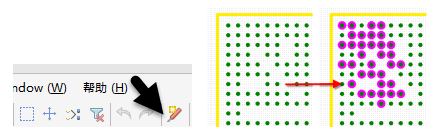

(1)为了方便识别哪些Bank之间可以互调,必须先对FPGA各个Bank进行区分。在原理图编辑界面中,执行图标命令“交叉探针”,单击某个FPGA的某个Bank,直接跳转到PCB中相对应的Bank管脚高亮,这时可以在某一机械层添加标注,进行标记,如图1所示。

图1 Bank的标记

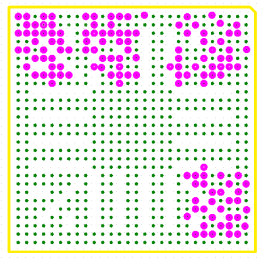

(2)按照相同的操作方法可以把调整Bank在PCB中进行标记,如图2所示。

图2 被标记的FPGA

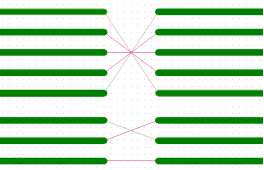

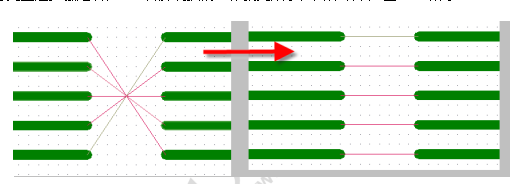

(3)完成上述步骤之后,就可以按照正常的BGA出线方式把所有的信号脚进行引出,并按照走线顺序对接排列,但非连接上,如图3所示,飞线是交叉的,但是不直接连上。最后保存好所有文档。

图3 信号走线的对接

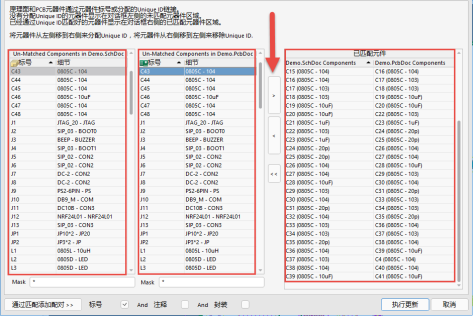

(4)在PCB设计交互界面中,执行菜单命令“工程-元器件关联”,进行元件匹配,将左边元件全部匹配到右边窗口,单击“执行更新”按钮,执行更新,如图4所示。

图4 元件的匹配

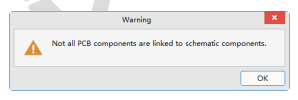

(5)执行菜单命令“工具-管脚/部件交换-配置”,定义和使能可调换管脚元件,如果弹出警告,须重新返回第(4)步进行操作,或者执行从原理图导入PCB的操作,使原理图和PCB完全对应上之后再按照此步骤进行操作,否则会弹出如图5所示的警告信息。

图5 警告信息

(6)找到FPGA对应的元件位号,勾选使能状态,双击该元件,对该元件的可以调换的I/O属性管脚创建Group操作,单击“OK”按钮,设置完毕,如图6所示。

图6 可调换FPGA的使能及Group设置

(7)执行菜单命令“工具-管脚/部件交换-交互式管脚/网络交换”,单击之前对接的信号走线,进行线序调换。注意:“Project”工程文件一定要保存一下,再操作。执行完上述步骤之后,PCB管脚调换的工作就完成了,具体效果如图7所示。

图7 线序的调换调整

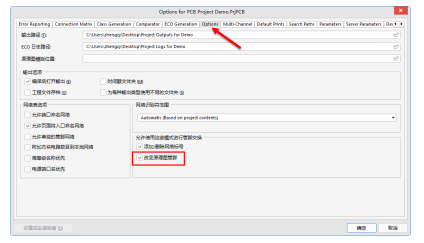

(8)PCB执行调换更改之后,需要把网络交互反导入原理图,如图8所示,执行菜单命令“工程-工程选项”,勾选反导入选项“改变原理图管脚”。

图8 反导入原理图设置

(9)在PCB设计交互界面中,执行“Update Schematic in Project”命令,按照之前原理图导入PCB那样的方法,完成PCB导入原理图。

因为有些原理图绘制的方式或格式错误,执行反标可能不完全或残缺,建议反标之后利用正导入方式核对一遍或者直接手工方式绘制管脚更换表,再一一进行比对更改。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21736浏览量

603202 -

pcb

+关注

关注

4319文章

23094浏览量

397764 -

PCB设计

+关注

关注

394文章

4688浏览量

85600 -

管脚

+关注

关注

1文章

227浏览量

32028 -

bank

+关注

关注

0文章

16浏览量

14847

原文标题:【干货分享】FPGA管脚的调整技巧

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA管脚的调整技巧

FPGA管脚的调整技巧

评论