在为高速ADC设计时钟网络时,抖动是最关键的参数之一。时钟抖动量将设置给定输入频率下可以达到的最大SNR。大多数现代高速ADC都有大约80fs的抖动,ADC的编码时钟应该在这个范围内。它当然应该小于1ps,以实现ADC的最大性能。

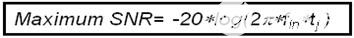

SNR和抖动之间的关系由以下公式给出:

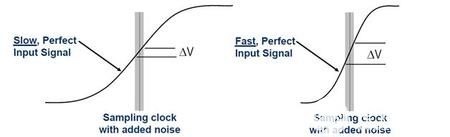

其中fin是输入信号的频率,tj是时钟的抖动。该公式表明,对于高频输入信号和固定量的抖动,最大SNR将降低。这是因为在给定的抖动量下,更快的压摆信号将具有更多的电压误差:

图1.ADC 噪声与时钟抖动的关系

对于频率成分相对较低的输入信号,例如在1MHz以下,时钟抖动变得不那么重要,但是当输入信号的频率为几百兆赫兹时,时钟上的抖动将成为误差的主要来源,并且将成为SNR的限制因素。

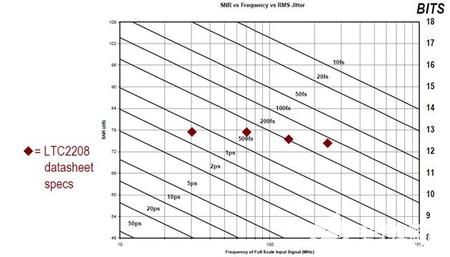

下面是一个简单的图表,显示了SNR如何随着输入频率和时钟抖动而降低:

图2.LTC2208 SNR 与频率 vs. 有效值抖动的关系

只需在X轴上找到您使用的输入频率,在Y轴上找到所需的SNR,您就可以准确地看到时钟上需要多小的抖动才能达到所需的SNR。为了将时钟的抖动与ADC的抖动相结合,您需要用功率将这两个项相加。

例如,如果你有一个100MHz的输入信号,并且你想要78dB的SNR,你将需要一个抖动小于200fs的时钟源。典型的FPGA将具有高达50ps的加性抖动,不应使用ADC时钟。通常,VCXO和低抖动PLL是最佳的ADC时钟源。

需要注意的是,这些方程源自标准采样理论,适用于任何制造商的所有ADC。

在设计具有高速ADC的系统时,考虑时钟抖动非常重要。它会严重限制您在系统中可以实现的SNR,并且可能会在系统设计中停止显示。保持尽可能低的时钟抖动与前端电路的设计同样重要。它不应该是事后的想法,而应该在设计的第一阶段考虑。

审核编辑:郭婷

-

adc

+关注

关注

100文章

7973浏览量

557327 -

SNR

+关注

关注

3文章

198浏览量

25773

发布评论请先 登录

一个低抖动时钟源的参考设计,不看肯定后悔

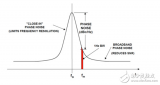

时钟抖动(CLK)和相位噪声之间的转换

最大信噪比与时钟抖动的关系

最大信噪比与时钟抖动的关系

评论