欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:校招FPGA笔试讲解

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1628文章

21722浏览量

602870

原文标题:校招FPGA笔试讲解

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

智多晶EDA工具HqFpga软件实用小功能

智多晶EDA工具HqFpga软件实用小功能增加啦,支持生成可调用网表的功能和ballmap功能。下面来给大家讲解一下如何通过HqFpga软件生成可调用的网表文件以及ballmap功能的使用。

请问DAC8760校零怎么给输出加负值?

是:数据0=0.7V;数据65535=10.7V(设置0-10V输出)。电流也是这个关系。试了5个板子都是一样,请问专家这个问题一般出在哪里。

2:DAC8760有校零寄存器,这个寄存器里写0-32678以内的数都可以。我要写负数或者大于32678的数就不起作用。第二个问题就是校

发表于 11-29 08:22

从校招新星到前端技术专家的成长之路

引言 我在2018年校招进入京东,主要负责广告投放系统的前端工作。在京东,这一路走来,我经历了多种角色转换,我从学生到职场人,从校招生到校招导师,从初级前端开发到前端技术专家,也见证了京东广告业务

开放原子校源行Meetup | 湖南两校共启OpenHarmony技术实习实训!

2024年7月1日-5日,开鸿智谷携手母公司拓维信息和开放原子校源行,在湖南中医药大学与湖南工业职业技术学院,成功举办了“开放原子校源行Meetup|OpenHarmony技术实习实训”主题活动

校企联合,共谋发展 | 欢迎陕西科技大学一行来访Aigtek安泰电子交流洽谈!

为进一步深化校企合作共建,促进优秀人才引进。4月12日,陕西科技大学电智学院的院长马院长、副院长任院长、电子信息工程专业副主任张攀峰老师、郭拓老师,到访西安安泰电子科技有限公司,就开展校企合作展开

基于微软数据中心的FPGA讲解分析

FPGA 和 GPU 最大的区别在于体系结构,FPGA 更适合做需要低延迟的流式处理,GPU 更适合做大批量同构数据的处理。

发表于 02-27 14:45

•649次阅读

锁定校源行(北理工站)!“开放原子开源大使”培训活动即将开启!

“开放原子校源行”公益项目由开放原子开源基金会与腾讯公司共同出资设立发起。双方携手通过建立高校开源社团、普及开源文化、研发开源课程体系等方式探索产教融合新路径。为高校开发者提供更大的实践舞台,培养

国外大学的FPGA开发项目盘点

据我了解,目前国内很多大学是没有开设FPGA相关课程的,所以很多同学都是自学,但是自学需要一定的目标和项目,今天我们就去看看常春藤盟校Cornell University 康奈尔大学开设的FPGA项目课程。

发表于 12-22 10:27

•1008次阅读

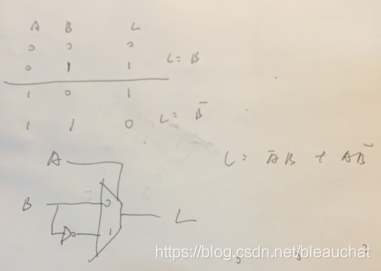

校招FPGA笔试讲解

校招FPGA笔试讲解

评论