台积电在2022 IEDM上发表了两篇关于3nm的论文;“Critical Process features Enabling Aggressive Contacted Gate Pitch Scaling for 3nm CMOS Technology and Beyond”和“A 3nm CMOS FinFlex Platform Technology with Enhanced Power Efficiency and Performance for Mobile SOC and High Performance Computing Applications”。

当我在演讲前阅读这两篇论文时,我的第一反应是第一篇论文描述了台积电的 N3 工艺,第二篇论文描述了 N3E 工艺,这在第二次演讲中得到了演讲者的证实。

我的第二个反应是这些论文延续了台积电尽量减少所呈现的技术细节数量的习惯。在这两篇论文中,电气结果至少以实数为单位,但第一篇论文只有 Contacted Gate Pitch,第二篇论文只有最小金属间距。我觉得这非常令人沮丧,一旦零件进入公开市场,内部人员和台积电的竞争对手可能已经知道它们是什么,关键pitch将被测量和披露,我不认为呈现高质量的技术论文会有什么问题。

N3工艺

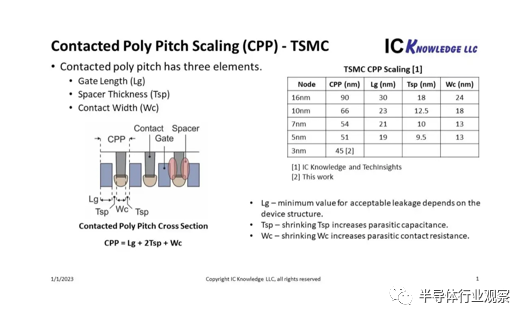

在第一篇论文中,台积电公开了 45nm 的 Contacted Gate Pitch(Contacted Poly Pitch,如我所描述的 CPP)。CPP 由栅极长度 (Lg)、接触间隔厚度 (Tsp) 和接触宽度 (Wc) 组成,如图 1 所示。

图 1.CPP。

从图 1 中,我们可以看到台积电通过减少构成 CPP 的所有三个元素来减少每个新节点的 CPP。逻辑设计是通过使用标准单元完成的,而 CPP 是标准单元宽度的主要驱动因素,因此缩小 CPP 是提高新节点密度的关键部分。

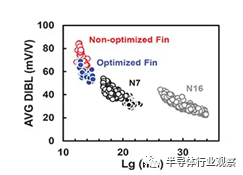

最小 Lg 是沟道栅极控制的函数,例如从具有不受约束的沟道厚度的单栅极平面器件转移到具有 3 个栅极围绕薄沟道的 FinFET,从而实现更短的 Lg。FinFET 的栅极控制在鳍底部最弱,优化至关重要。图 2 说明了多个 TSMC 节点的 DIBL 与 Lg,以及优化鳍片如何减少当前工作的 DIBL。

图 2. DIBL 与 Lg。

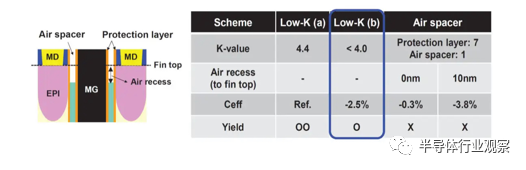

缩小 CPP 的第二个因素是 Tsp 厚度。除非垫片(spacer)经过优化以降低 k 值,否则降低 Tsp 会增加寄生电容。图 3 说明了 TSMC 对低 k 间隔物与气隙间隔物的研究。台积电发现低 k 间隔物是缩放 CPP 的最佳解决方案。

图 3. 与栅极间隔器的接触。

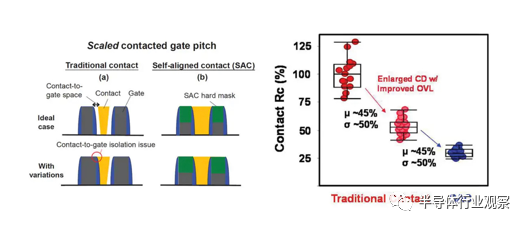

CPP 的最后一个元素是接触宽度。在这项工作中,开发了一种优化的自对准接触 (SAC) 方案,可提供较低的接触电阻。图 4 的左侧说明了 SAC,右侧说明了电阻改善。

图 4. 自对准触点。

这项工作使 N3 工艺具有 0.0199μm 2的高密度 SRAM 尺寸。随着台积电推进其 2nm 工艺,这项工作也很重要。在 2nm 时,台积电将转向一种称为水平纳米片 (HNS) 的环栅 (GAA) 架构,HNS 可实现更短的 Lg(4 个栅极而不是三个围绕一个薄栅极),但 Wc 和 Tsp 将还是有待优化。

N3E工艺

台积电将 N3E 工艺描述为 N3 的增强版本,有趣的是,N3E 被认为比 N3 实现了更宽松的间距,例如 CPP、M0 和 M1 都被认为出于性能和良率的原因而被放松。关于台积电 N3 是否准时,有不同的说法。我的看法是,N5 进入风险始于 2019 年,到 2020 年圣诞节,商店中出现了配备 N5 芯片的 Apple iPhone。N3 进入风险从 2021 年开始,配备 N3 芯片的 iPhone 要到明年才能上市。在我看来,这个过程至少晚了 6 个月。在本文中,公开了尺寸为 0.021 μm 2的高密度 SRAM 单元。大于 0.0199 μm 2的 N3 SRAM 单元。N3 的产率通常被描述为良好,提到了 60% 到 80%。

本文讨论的这个过程有两个主要特点:

FinFlex

最小金属间距为 23 纳米,铜互连采用“创新”衬里以实现低电阻。

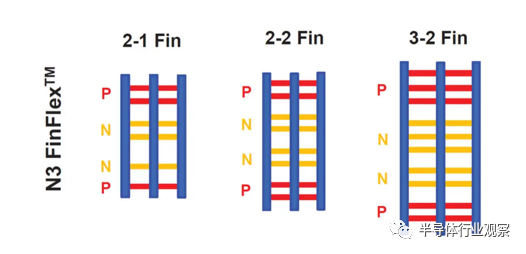

FinFlex 是一种混合和匹配策略,具有双高度cell,可以是顶部 2 鳍cell,底部 1 鳍cell以获得最大密度,2 鳍cell超过 2 鳍cell作为中等性能和密度,以及 3 鳍超过 2 个鳍状的cell可实现最佳性能。这为设计人员提供了很大的灵活性来优化他们的电路。

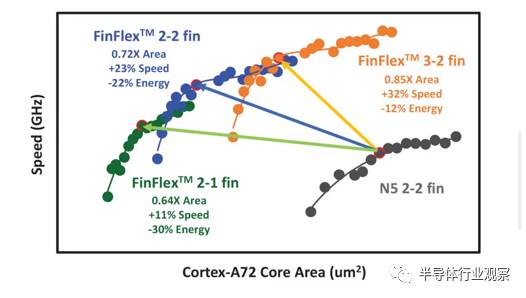

图 5 说明了各种 FinFlex 配置,图 6 将每种配置的规格与 5nm 的标准 2 over 2 鳍式cell进行了比较。

图 5. FinFlex cell。

图 6. 3nm FinFlexcell性能与 5nm cell的对比。

本文中的绘图是 15 级金属堆叠在大约 550 欧姆时的通孔电阻分布。在目前的工艺中,功率通过金属堆叠的顶部进入,必须通过通孔链向下传输到设备,550 欧姆的电源线电阻很大。这就是英特尔、三星和台积电都宣布为其 2 纳米级工艺提供背面供电的原因。随着晶圆的极度减薄,从背面引入电源的通孔应能使通孔电阻提高 10 倍以上。

比较

作为读者,您可能会有一个问题,即此工艺与三星的 3nm 工艺相比如何。台积电仍在使用 FinFET,而三星已过渡到 GAA——他们称之为多桥 HNS。

根据我们的计算,在 5nm 节点,台积电最密集的逻辑单元是三星最密集逻辑单元密度的 1.30 倍。如果您查看图 6 中的 TSMC 密度值,在 5nm 中,2-2 鳍式单元的密度比 2-2 单元高 1.39 倍,而 2-1 单元的密度提高了 1.56 倍。三星有两个版本的 3nm,SF3E(3GAE)版本比 5nm 密度高 1.19 倍,SF3(3GAP)版本比 5nm 密度高 1.35 倍,进一步落后于台积电行业领先的密度。我也相信台积电在 3nm 上有更好的性能和更好的功率,尽管三星已经缩小了功率差距可能是由于 HNS 工艺。

审核编辑 :李倩

-

台积电

+关注

关注

44文章

5703浏览量

167106 -

单栅极

+关注

关注

0文章

2浏览量

5815 -

FinFET

+关注

关注

12文章

251浏览量

90420

原文标题:台积电3nm FinFET工艺

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

台积电3nm FinFET工艺

台积电3nm FinFET工艺

评论