1、项目背景

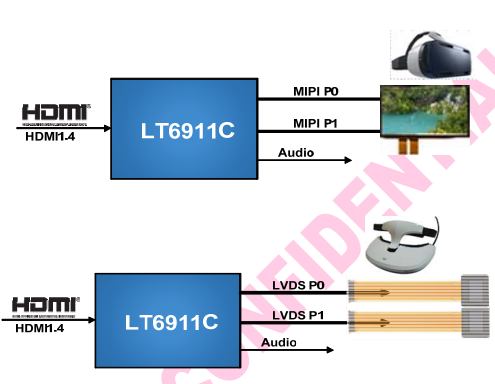

明德扬(MDY)为某研究所研制的视频接口转换模块,该模块将HDMI视频转成LVDS7:1视频。视频输入接口采用的是HDMI 4K输入,基于Xilinx K7325t的高速收发器,特点是无需外围HDMI接收芯片,大大简化了硬件设计。该视频接口转换模块如图1所示,其中k7核心板型号为MP5650,底板和核心板均为明德扬自研产品。

本文简单介绍了Xilinx官方的HDMI例程的建立步骤。

图1视频接口转换模块

图2 MP5650核心板

2、工具

Vivado 2022.1;

Vitis 2022.1;

HDMI License。

3、操作步骤

(1)新建一个vivado工程,平台选择KC705。

(2)选择HDMI 1.4/2.0 Receiver Subsystem IP核,按下图进行IP核的配置。

(3)配置完后,并自动产生IP相关文件,在IP核上右键选择Open IP Example Design,选择例程的存储路径,点击OK。

(4)软件会自动生成一个例程,待例程生成结束,进行Synthesis、 Implementation和 GenerateBitstream流程生成bit文件。

(5)导出硬件底层,建立vitis工程,选择File → Export → Export Hardware。

(6)建立一个文件夹,用来存放Vitis工程,启动Vitis,选择Tools → Launch Vitis IDE。

(7)打开Vitis环境,建立平台工程,选择File → New → Platform Project。

(8)选择vivado生成的exdes_wrapper.xsa文件,点击Finish。

(9)右键生成的硬件平台,选择Build Project。

(10)在platform.spr页面,选择Board Support Package,展开Peripheral Drivers。

(11)在Peripheral Drivers下,找到v_hdmi_rx_ss或者v_hdmi_tx_ss,点击Import Examples。

(12)在Import Examples选项中,选择一个应用工程,Microblaze对应的工程有Passthrough_Microblaze、Rxonly_Microblaze,Txonly_Microblaze。

(13)Build当前应用工程,得到.elf文件。

审核编辑黄昊宇

-

FPGA

+关注

关注

1629文章

21736浏览量

603366 -

HDMI

+关注

关注

32文章

1704浏览量

151923

发布评论请先 登录

相关推荐

HDMI1.4/2.0 Subsystem官方例程的建立

HDMI1.4/2.0 Subsystem官方例程的建立

评论