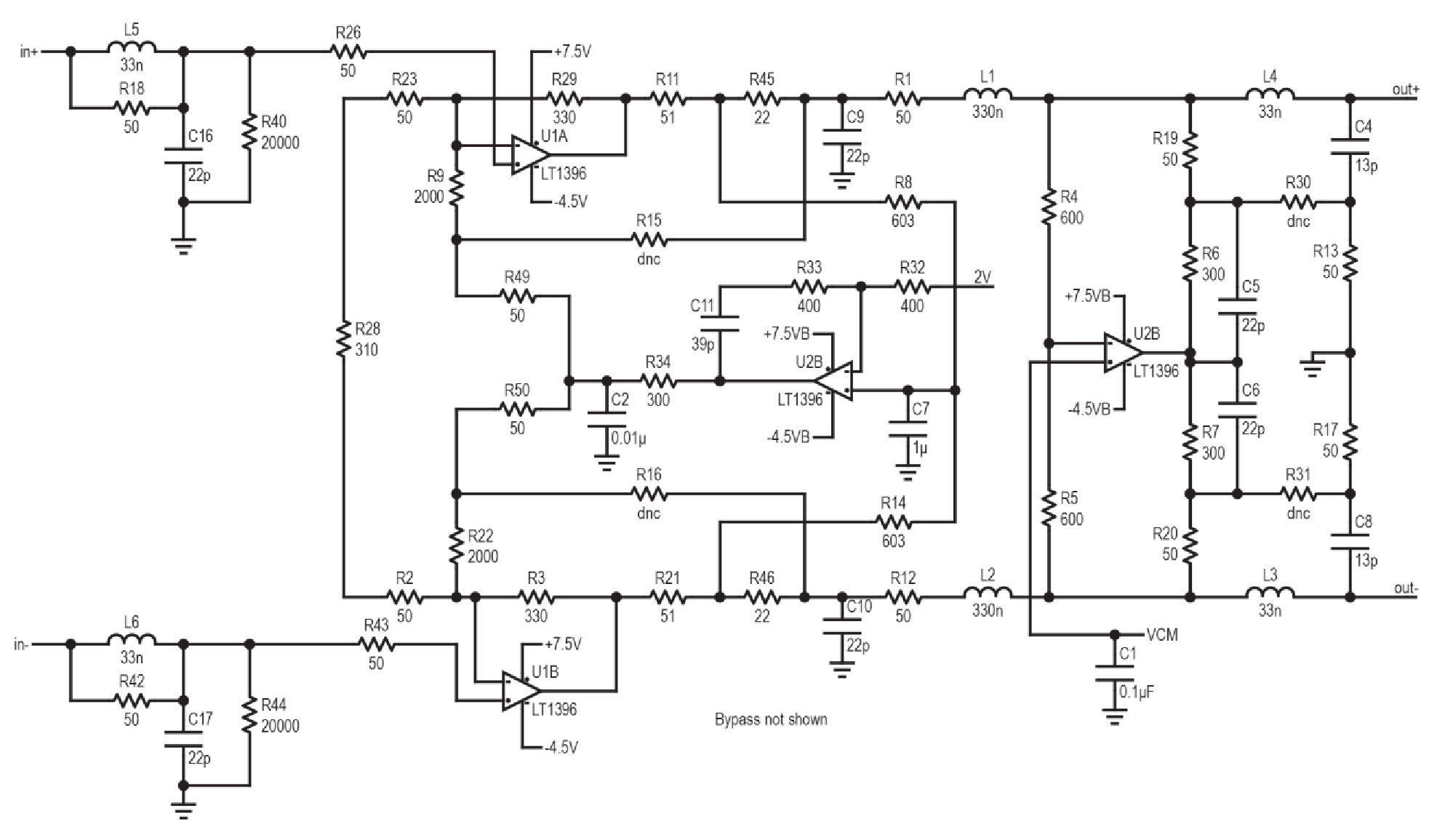

下面显示的电路效果很好。你应该尝试一下。

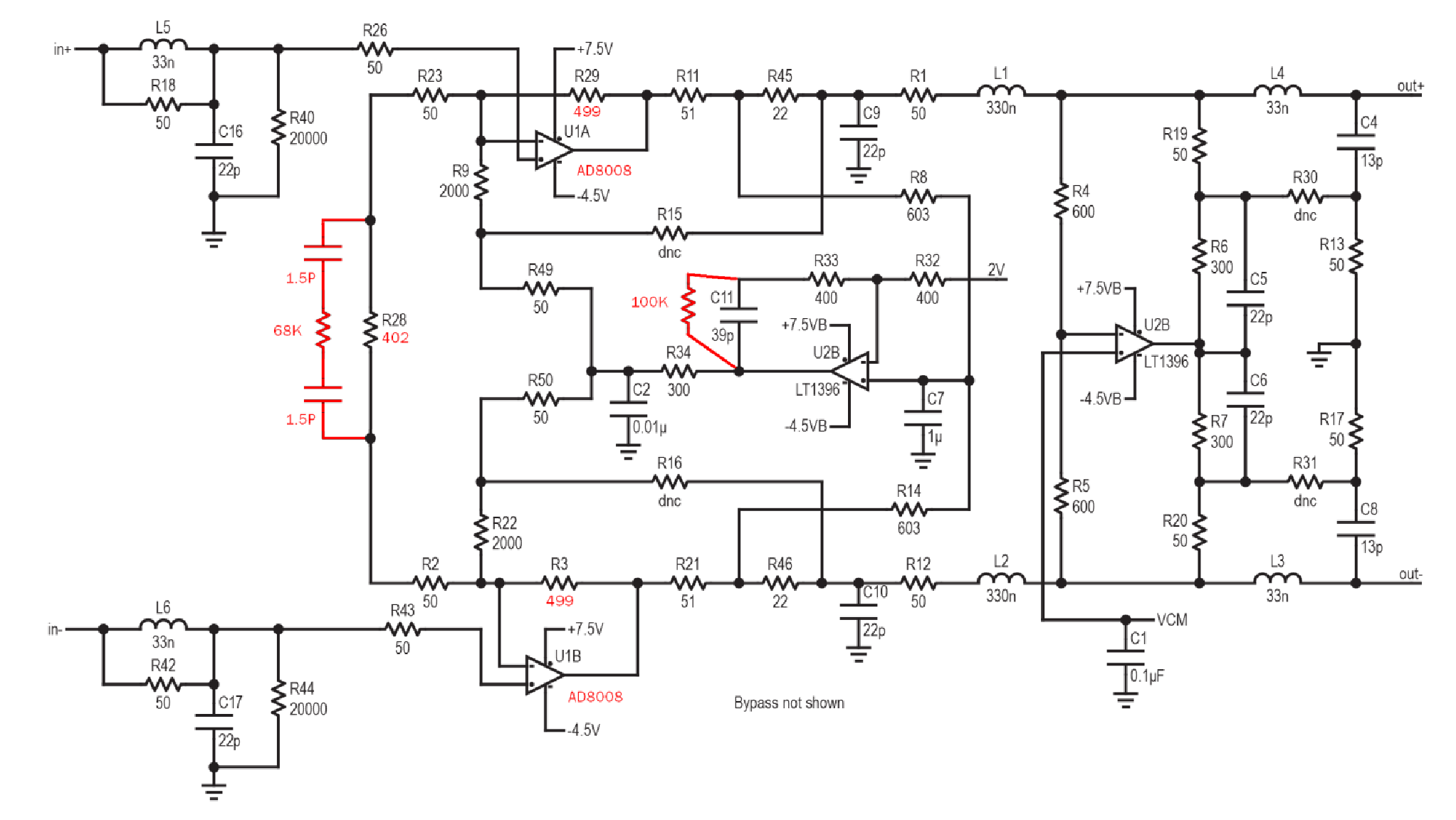

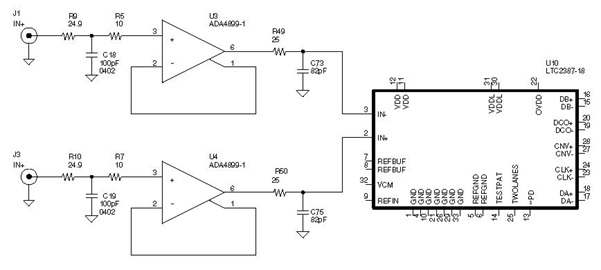

这适用于标称值为0-3V单端或差分信号,来自CCD、CMOS图像传感器或其他类似信号源。如图所示,信噪比为88dB。使用AD8008代替U1,并进行一些其他细微改动,可产生92dB SNR,在15Msps时在一个像素中建立至0.02%。

用于映像的驱动程序(长版本)

首先,我要说明此驱动程序不一定仅适用于映像应用程序。通过成像,我们实际上意味着:任何涉及采样同步步骤到不同电平的信号,例如您可能从CCD看到的信号。或者更准确地说,是突然的阶跃,或瞬态,然后相对静态地停留在任意电压电平下,最好涉及时钟周期的某个合理部分,以便在采样前建立。这些不同的级别可能是像素。例如,这可能意味着CCD场或线性阵列传感器,光学,X射线或红外图像传感器,或者实际上是多路复用信号。如果该驱动器之前有多路复用器,则多路复用器选择的信号的频谱功率分布应主要低于1 MHz,至少在采样前约10-15 nsec期间。

如果此用途用于CDS采样,则实际最大像素速率为7.5Msps,并且必须在数字域中减去黑色基准电压源。

LTC®2387 是一款 18 位 ADC,其 SNR 和线性度远超集成式 CCD 解决方案。

可以使用动态范围代替PGA,以适应大范围的积分时间或不同的器件。毋庸置疑,这并非针对消费类成像应用。本文的初衷是将LT1396用于U1和U2,但利用ADI公司的多个电流反馈放大器可以实现更低的噪声。以更高的功耗为代价,更高的SNR的好处可能受到传感器特性的限制,并且在一定程度上受到传感器使用的限制。例如,如果可以对多个帧进行平均,并且分辨率受到像素间增益和偏移变化以及噪声的影响,则驱动器的较高SNR在任何情况下都将具有有限的价值。

在撰写本文之前几个月,AD8008和AD8002对该电路进行了测试。当时,这个其他人口并不打算发表。这样做只是为了调查目的。其他供应商的电流反馈放大器(CFA)也已尝试过,因为它们在本系列的第一部分和第三部分中已经出现。但只有一家供应商的器件比 LT1396 实现了有意义的改进。现在,发布它似乎是合适的,因为该供应商现在是我们。AD8008 还具有低于 LT1396 的 in+ 偏置电流。

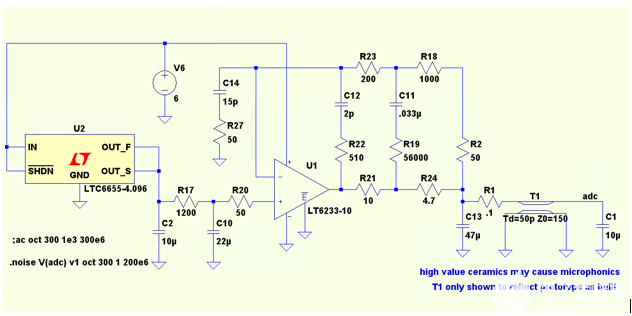

此拓扑与 2013 年 7 月的文章“用于成像的近乎无噪声的 ADC 驱动器”相关。该版本针对 84dB SNR 20Msps LTC2270 发布,其输入范围为 2.1V p-p。如果需要更多详细信息,我建议也阅读该文章。

图 2 红色值反映了 LT1396 版本更新至 AD8008 时的变化 红色元件是布局上不存在的建议附加组件。

本电路与20 Msps LTC2270的2013年拓扑结构之间的区别在于,此新版本必须在输入级提供增益,以便为LTC2387的8V峰峰值输入范围实现足够的信号摆幅。这种方法假设“视频”信号处于常见的3-5V峰峰值范围内。第一级输出端的信号电平必须大于ADC的输入范围,因为它在ADC之前的共模伺服级中衰减。共模伺服提供基本上无噪声的单端到差分平移。此版本中的衰减仅为3.8dB,小于我之前使用这种方法的情况。这部分是因为在12V电源下,驱动输入放大器输出端的无失真信号摆幅被限制在约8V峰峰值。被驱动放大器(消耗此增益)假设为单端驱动,其偏移量几乎是补码放大器的两倍。如果采用标称平衡的差分信号驱动,并且此版本与原始文章的不同之处在于它本质上是差分的,则输入级增益可能会更高,SNR也会得到改善。这种改善部分是由于噪声电流在较高增益下变得不那么显着,部分是由于共模伺服中的衰减更大,从而降低了噪声电压和噪声电流的影响。共模抑制将单端驱动(或在这种情况下,相当不平衡的差分驱动)转换为体面的差分驱动,更像传输线巴伦。原始文章使用 LT1395 系列作为单位增益输入缓冲器,直接从反相输入获取功率输出(用于驱动 ADC 的实际功率),就好像它是发射极跟随器一样。如果视频信号为 10V 峰峰值差分,则 LTC2387 可能采用该板精确地以这种方式驱动。这将需要一些不同的人口。当然,如果共模正确,并且输出阻抗得到良好控制,传感器的8Vp-p差分驱动可能会直接驱动ADC。LTC2270 版本将 4-5Vp-p 单端视频输入转换为 2.1Vpk-pk 差分。LT1396 基本上充当反馈环路内的一对互补发射极跟随器。放大器的输出仅用于通过最小402Ω FB电阻闭合环路。

以这种方式使用的 LT1395 具有相当低的噪声和非常快的建立速度。然而,在产生增益时,其4.5 nV/√Hz输入噪声电压和25 pA/√Hz的反相输入噪声电流是主要噪声源。不幸的是,低噪声电压反馈放大器和轨-轨输出放大器通常被宣传为适合成像驱动器,但通常速度太慢。

码型噪声和建立

慢建立会将任何时序变化、任何受传播延迟或幅度确定性变化影响的时钟馈通、任何串扰转换为通常所说的“码型噪声”。这通常是对角线的形式,有时会产生其他有趣但仍然不需要的效果。这些模式通常提供有关该变体起源的线索。如果建立不完全,时钟馈通或CCD中的电荷注入的重复变化将产生与时序变化类似的影响。同样的情况也存在于时序变化的多路复用信号中,或者与拓扑中的器件相关的可变电荷注入,或者多路复用器输出电容中常见的“电荷共享”。可怕的时序变化可能源于软件、中断驱动处理器,在较小程度上可能源于集成时序引擎、FPGA 中的 DLL 和其他设备,而不是传感器本身。图案噪声也可能源于串扰机制,其根源在于糟糕的PCB布局设计,当然也源于电源设计,尽管通常是间接的,但纹波转化为电荷注入的变化。

在某些情况下,成像客户断言,缓慢的建立应该不是问题,因为人们认为像素之间没有干扰,也没有时序变化。回想起来,这些似乎往往是后来发现模式噪声是一个问题的情况。然而,在某些情况下,模式噪声无疑是由于选择不当的差分放大器引起的振铃,不适合低增益、高压摆应用。由于相位裕量差,振铃也会将时序变化转化为模式噪声,因为它是另一种形式的存储器。反射回放大器输出的复杂电抗负载会产生模式噪声,因为它不仅可能延迟,而且可能会阻止建立,其方式是微妙的,在示波器、数据手册或仿真中观察建立行为不是很明显。我们曾有人发送简单的模型,质疑为什么模拟没有显示效果。

未充分建立的放大器可能看起来PSRR较差,因为电源会对转换和建立产生一些影响。这可能会被误解为仅仅是电源问题或PSRR问题。修理电源就像在断腿上贴创可贴一样。

许多放大器具有不对称压摆,再加上高dv/dt信号源、缓慢建立甚至后滤波,可能会将时钟直通变化、电荷注入和其他像素间干扰转化为平场中可识别的伪影。在许多情况下,建议在这种放大器之前进行一些频带限制,即使人们可能会认为它会加剧缓慢的建立。此问题可能标记为包络检测。从成像设备传导到慢速建立放大器的类似RFI的伪影可以产生模式,手机流量的接收也可以产生模式,尽管这更随机。假设可以在数字域中实现简单建立行为的模型,一致的建立时间虽然可能不够快,但不接近压摆率限制的非线性效应,在软件中更容易校正。

其中一些模式噪声问题的根源在于,放大器可用的建立时间通常小于预期,并且通常小于像素间隔的50%。在 15Msps 时,这意味着只有 33 纳秒。例如,LT6237(有时不明智地提升用于成像)在4Vp-p场景中需要大约1微塞才能建立到18位。这可以说太慢了大约 30 倍。当然,合适的放大器也必须是低噪声的。

在15 Msps和接近18位时,这似乎使CFA成为唯一明显的选择。LT1396在25 nsec内建立至0.1%,除此之外,数据手册中未对此进行表征。无论如何,这在建立和噪声方面都不够好。AD8008至0.1%的建立时间为18 nsec (2Vp-p),AD8002的建立时间为16 nsec。请注意,我仅使用稳定到 0.1% 进行比较,但甚至稳定到 0.01% 可以说是不够的。当然,许多成像设备不保证18位转换器,但是,如果可以对多个帧进行平均,则可以在统计上实现18位的好处。

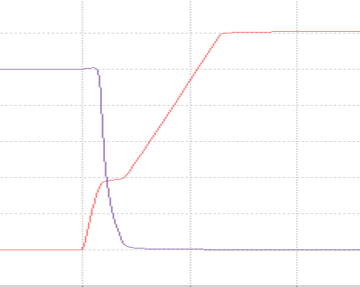

如上图所示的电路在一个像素间隔内建立到0.02%以内,在满量程阶跃后,在15Msps,在10Msps时在0.01%以内。

信 噪 比

然而,放大器的建立并不是选择放大器的唯一因素。反相输入噪声电流在所有这些CFA的低增益(<7dB)应用中占主导地位。

LT1395系列具有4.5 nV/√Hz和400 MHz GBWP,一直是我的主力。在下面的电路中,将LT1396作为U1时,我们看到SNR为87.5dB。这比之前发布的 LTC2270 版本的 83.5dB 要好 4dB。然而,就ADC输入端的噪声密度而言,它并没有更好;因为输入范围增加 12 dB 是导致 SNR 增加的原因。

但是,使用AD8008时,我们看到SNR为90.7dB;AD8002的信噪比为91.5dB。在稳定和信噪比之间有一些权衡。建立速度更快的版本在信噪比方面差约1 dB。

热尾

CFA表现出由于局部加热引起的热尾,主要是输入级中的第二个晶体管,在加热有机会到达第一个晶体管中的对应晶体管之前的一段时间内表现得最为严重。如果所有 4 个输入晶体管都处于相同的温度,它们的 VBE 将在很大程度上抵消。然而,它们的温度不同。

当在传递函数的另一端存在扩展停留时,影响的大小最为严重,约为0.05%。一个表观的热时间常数约为1.3-1.5微塞,但它不是一个简单的时间常数。对应晶体管之间存在时间滞后,看到耗散的晶体管的热时间常数以及芯片本身的热质量之间存在时间滞后。使用汞湿继电器揭示了这一点,但限制了可以产生的脉冲的持续时间。这种成像驱动器/ADC组合还带来了我在汞润湿开关中没有观察到的光效。电导率开始和停止时的行为显示了涉及表面张力的物理现象的证据。然而,使用模拟开关生成测试信号在早期阶段向我们隐藏了这些影响,似乎是由于载流子寿命长会延迟完全关闭,从而产生延长的建立时间,奇怪的是,误差相同,但极性与热效应相反,持续时间约为 750 nsec 至 1 微塞。更令人高兴的是,对于像素之间的短时间瞬变,返回到原始状态时的热误差很小。在平坦场中,当时钟馈通或像素之间的其他瞬变时,这些效应不应像缓慢的电建立那样产生图案噪声。

随着脉冲持续时间和信号电平的变化,效果从看似过阻尼的缓慢建立到立即过冲不等。过冲不属于与反馈环路中相位裕量差或振铃相关的类型,而是显示为 1.3-1.5 微塞的简单 tau。然而,由于存在具有不同tau的相反效应,因此沉降的形状随时间而变化,在某些情况下会产生快速建立的错觉,然后是延迟的过冲。对于许多成像应用,这种热尾应该不是问题,因为它可能只在线条或帧的开头看到。对于医学成像,在平坦的视场中响应短时间瞬变而快速建立是最重要的,热尾部在假设的高对比度图像中表现为微妙的重影,在低对比度视场中是难以察觉的,即使增强到高对比度。如果能够显示这种分辨率的高对比度彩色图像,则需要大约80亿种颜色才能使热尾部可辨别。

模拟校正还是数字校正?

有一个一阶补偿网络,我没有在PCB上做规定,它由0.75 pF组成,与68KΩ串联,放置在R28上。这是以1.5pF-68K-1.5pF的形式进行测试的。

它的tau为51 nsec。尽管实际的热尾是一个更复杂的功能,与复杂的3D热环境以及与加热相邻输入晶体管相关的热滞后,此时存在一定程度的抵消,但简单网络在干扰短的情况下在不到1个时钟周期内加速建立。但是,如果在可变持续时间偏移到输入范围的相反极端后需要建立到16-18位电平,则在数字域中对放大器中的热过程进行建模可能是解决此问题的最佳方法。可能有必要使用软件学习,因为可能有多个贡献者,包括成像设备,这可能会混淆简单的方法。

线性

该电路线性度的测试以与原始文章类似的方式完成,涉及fs/2或fs/4的高电平方波,以及较低幅度的正弦波,即奈奎斯特模拟像素的方波。如果采样的时间相对于方波被推到“像素”的末端,因此,您将努力对实际像素进行采样,则互调失真应最小。不建议提前采样,因为这会缩短建立时间。不太明显的是,如果过早采样,共模伺服将没有时间建立,因此,不会有效地抑制共模。有些人质疑成像应用中是否需要高线性度,但即使我可以,我也不会解决这个问题。LT1396版本的线性度不如AD8008,这可能与LT1396中的交越失真有关。然而,LT1396 版本的线性度实际上可能不是许多成像应用所关心的问题,87dB SNR 可能是可以接受的,因为它很可能由传感器主导。在这种情况下,LT1396 的较低电流消耗可能很有吸引力。AD8002的失真比AD8008版本略大,但噪声更低,因此对于其他客户来说可能更可取。许多成像器件甚至会比LT1396版本的–87dBfs本底噪声高20 dB左右。对于短孔径时间、低照度、低剂量激发或小面积成像器,驱动器的信噪比无关紧要...多。事实上,LT6411 是一款源自 LT1395 系列的器件,仍采用 12V 工艺,由于采用了内部反馈电阻器,因此建立时间要快得多,而且应该会产生与 LT1396 版本大致相同的本底噪声,因此正在考虑对上述电路板进行新的迭代。AD8003三元组有第二种变体,但事实证明它具有更严重的热尾,尽管它可能有一些优点,因为它更快。

本电路与 LTC2270 的原始 2013 成像拓扑不同,因为输入级还有助于从单端信号到差分信号的转换。由于差分增益约为3,因此第一级的输出具有一个共模分量,该分量相对于差分分量降低约14 dB。因此,即使ADC的输入范围高出4倍,输出共模伺服也可以与原始设计大致相同。然而,这种更高增益、更高输入范围的版本确实有一个额外的共模环路,用于控制电平转换,并降低输出伺服在电平转换中的作用。然而,这种电平转换可能需要微控制器和DAC的参与。原型在伺服中具有很高的增益,并且在照明发生剧烈变化的情况下,伺服器必须做出响应。可能需要降低该伺服的增益。(C11与电阻并联)。这是视频电平的问题,因为0-4V或0-5V不允许那么多的动态余量。如果输入共模相对稳定,电平偏移可能只是一个固定偏置。

共模输出伺服必须控制一对节点,在共模下,不得显示为容抗。输出滤波器将共模伺服与第一级的输出、电平转换伺服、ADC的输入电容以及各种传输线隔离开来。滤波器还尽可能降低混叠噪声带宽,并降低从ADC返回的瞬变的频率成分,以及从前端返回的瞬态共模的频率成分,共模伺服都无法很好地处理,使其保持闭环操作。

此 LTC2387 版本中的共模伺服 U2A 通过 C5 和 C6 工作于输出滤波器,以及旨在显示为 ADC 吸收性网络的一部分。如果没有此功能,使用双工器级跟随伺服可能会影响共模建立。例如,电路板具有将最后一个吸收器从R13移动到R30的规定,或者在两者之间分配。但是,将整个共模瞬态功率返回到共模伺服的输出可能是不明智的。伺服可以被视为在不影响差分阻抗的情况下降低了共模阻抗。

L1、L2、L3 和 L4 是共模环路的组成部分,将受控节点与容性负载 C9 和 C4 隔离开来。滤波器L4和C4的输出端以及对应的输出端是差分双工器,在较高频率下似乎对ADC具有吸收性。差分信号不与共模伺服相互作用,但共模组件将在L1和L4之间的节点及其对应处看到低阻抗。

正如本系列第三部分所解释的,输出伺服中元件的宽松公差会影响SNR和失真。与其重复原始文章中解释的细节,如果这篇文章在细节上显得有点不足,我会要求您阅读这些细节。

使用具有相对高输入电流的CFA可能会成为某些传感器的问题来源。LT1395的最大in+电流为30 uA。然而,许多低噪声VFB放大器也具有相当高的输入电流。例如,LT6200 的最大偏置电流规格为 –40uA,而 LT6237 的输入电流规格均为 12uA,但两者都太慢。AD8008和AD8002的最大输入+电流分别为8uA和10uA。如果采样速率小于10 Msps,则可以使用LTC6268 FET放大器(5 nV/√Hz)作为输入级。然而,LTC6268 被限制在一个 5V 电源内,因此需要一个差分视频信号才能实现实用。

测试和验证

由于没有预算可以购买,也没有时间设计一个 18 位线性 CCD 仿真器,也不可能有任何 CCD 或光源,就此而言,这可能为我们提供任何方法来证明该解决方案在我们愿意相信的范围内是线性的,我们别无选择,只能澄清原始文章中提出的情况, 并完善它。我们确实收到评论说,成像客户不知道如何解释我们提出的案例。

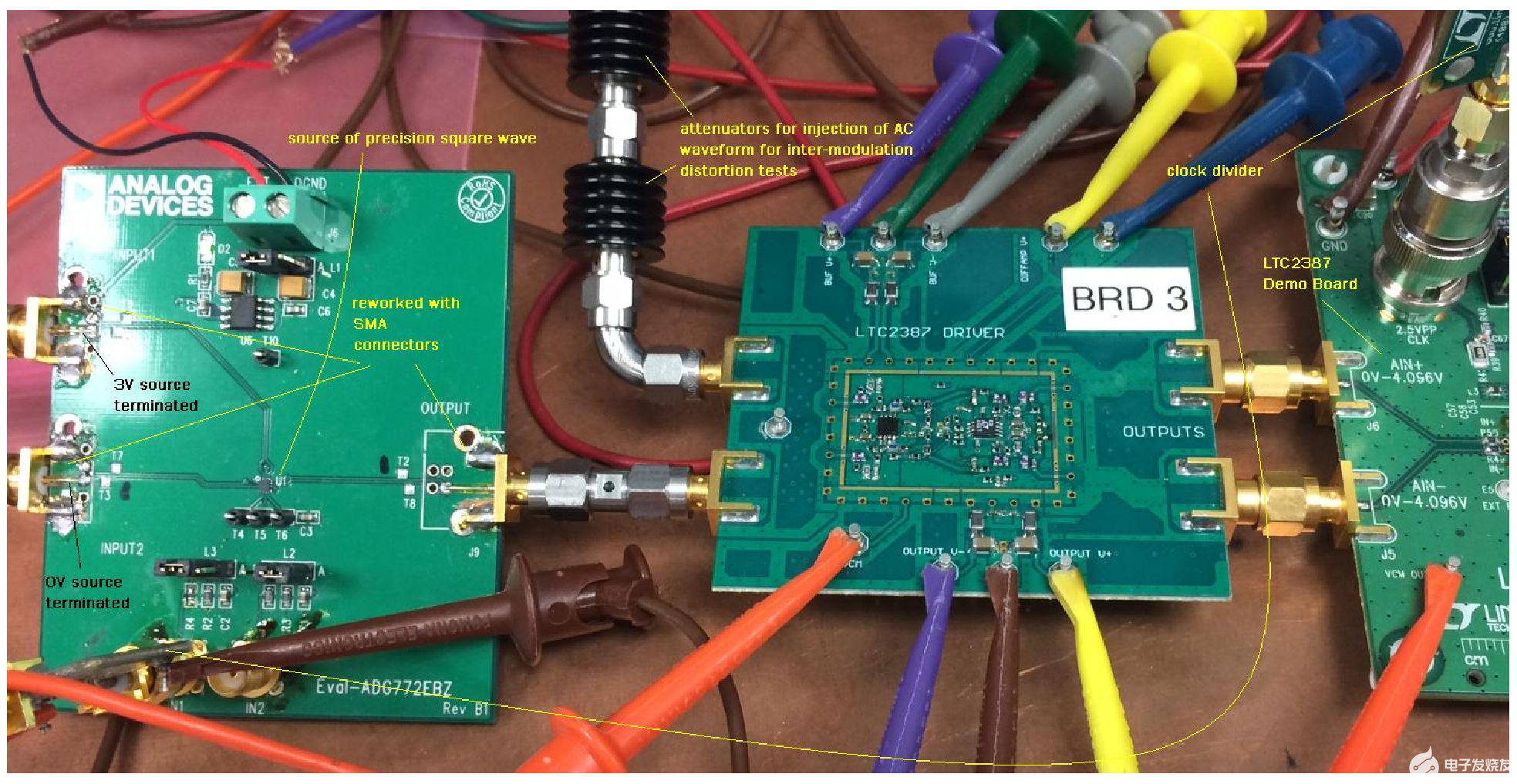

图3.精密方波源与正弦波相结合的实验装置

原始文章中的测试用例是奈奎斯特的方波,并结合了 70 KHz 的音调。在方波的存在下,有一些IM产品生产出来,但基本表观功率没有变化,至少没有出小数点后3位。AD8008的正弦波IM失真水平相当低,为15-16位电平。

在本设计中,使用 LT1396 时,奈奎斯特鳍片处的杂散约为 –65dBfs,或相对于 –20dB 正弦波约为 –45dB。AD8008的功耗为–98dBfs。这与16位ADC的量化误差功率相同。我并不是说它源于量化误差;它只是在功率方面具有可比性。在以热噪声为主的时域应用中,至少在AD8008的情况下,热噪声无关紧要。

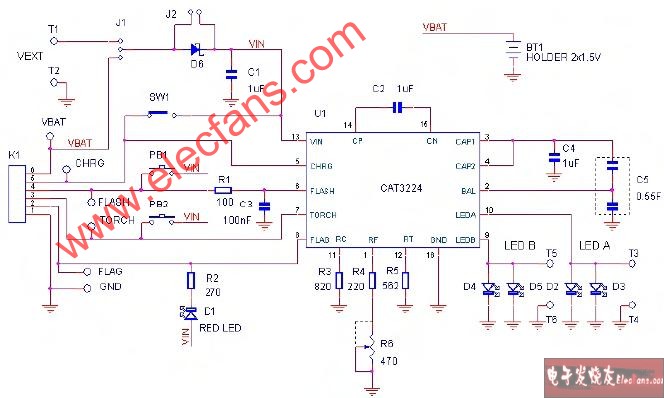

在这种新案例中,我们的单端方波源是一个ADG772模拟开关,在两个基准电压之间切换,每个基准电压都有传输线的源端接。它们在放大器上不是端接,而是在R18中以高频端接。此开关是差分开关,未使用的线路也是源端接的。请注意,L4与R18并联可降低源阻抗,以提高噪声密度。R40和R44本身不是端接,其值取决于成像设备。无缓冲成像器件可能要求不存在这些电阻。重复电荷转移代表相当低的阻抗,并将提供足够的偏置电流。

如果采用单端驱动,则另一路输入可采用仿真成像器件阻抗的源进行偏置,或者采用来自低噪声基准电压源的低阻抗进行偏置。

CFA的输入电流相对于许多电压反馈放大器来说很高,如果唯一的存储机制是C16,则在一个时钟周期内,在15 Msps时,它可能会下降近20mV。如果时序是确定性的,这只是一个偏移量。如果时间是可变的,这可能会变成噪音或模式。4V范围内的20 mV压降为0.5%,18位转换器的压降为1300个。如果定时信号和采样之间的总抖动为50 psec,则转换为约1 lsb的噪声。现在,按照高速标准,50 psec的抖动很大,而1 lsb比热噪声低20 dB,因此除非时序由软件驱动,否则它不太可能成为噪声源。软件中更高优先级的中断可能会产生非常重大的损害。请注意,FPGA 中的 DLL 很容易产生 50 psec 抖动。

在此LTC2387版本的互调测试中,由于与发生器、滤波器和直流模块有关的原因,我们将交流频率提高到300 KHz,但将其功率电平降至–20dBfs,从而使方波驱动具有接近全振幅。当两个音调的功率相等时,IM产品通常最大,但幅度瞬变越高,更接近实际成像信号。此场景旨在仿真成像信号中的近满量程步进,但使用较弱正弦波的调制作为线性度的度量。如果存在显著的非线性,无论是以压缩形式还是以差分相位误差的形式,三阶交调产物都会从方波偏移300 KHz。如果有压缩,基波的振幅也会改变,尽管需要大量的数字才能看到效果。我们在基本功率Pscope中添加了数字,以测试这一点。

由于缺乏更好的术语,即关于双极零的对称,如果存在相同程度的压缩(增益降低),则由正弦波叠加在两个不同的逻辑状态上产生的信号的对称双峰性质可能不会产生显着的三阶IM。它将在奈奎斯特以下2fsine生产产品,这是由于这两种状态之间的相位交替产生的。因此,我们还在奈奎斯特测试了300 KHz正弦波与方波的组合,在双极性零点和传递函数的任一最大值之间切换。接近满量程的压缩会产生AM,AM在奈奎斯特减去f处显示为音调,向外是下边带,但实际上两个边带组合为另一个之上的上边带别名。这种情况实际上并没有产生更严重的三阶互调失真,因此假定线性度是可以接受的。请注意,方波中与fs/2的轻微偏移会隔离两个边带,但也会导致整个“像素”的采样。

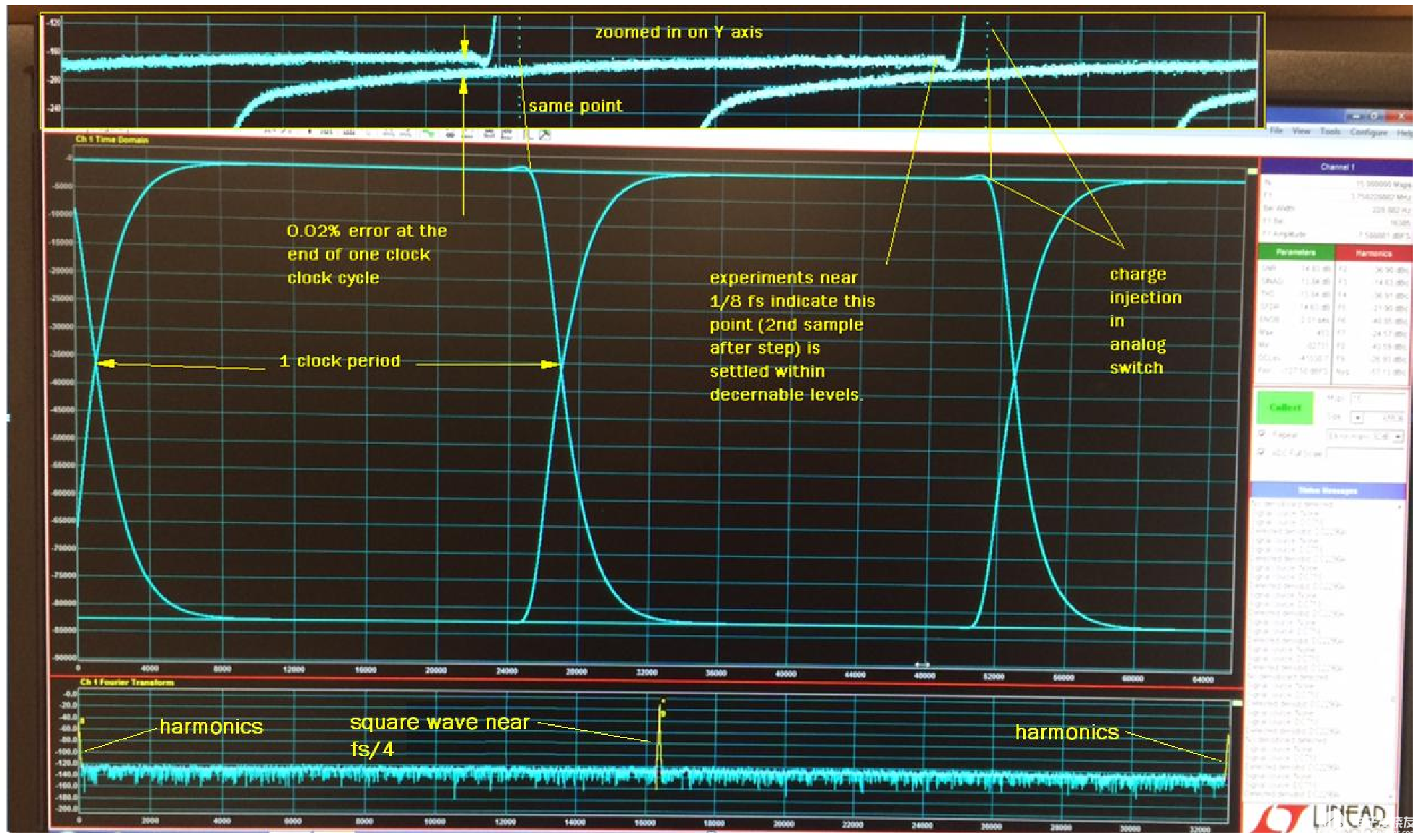

图4.1/2 奈奎斯特 (3.75 MHz) 附近的方波测试,显示变焦 Y 轴上的热尾(上插图)

图4显示了奈奎斯特/2附近的方波,而不是奈奎斯特附近的方波测试。频域图上指示的谐波只是偶数阶,所有奇次分量都存在于fs下的方波中。不对称压摆率会产生第 2 个(在本例中靠近奈奎斯特)、第 4 个(靠近 DC)及以上,显示此仅用于阐明测试场景。压摆率的不对称性是可见的,因为线在两种状态之间没有交叉一半。如果方波在奈奎斯特,在状态变化之前采样,则数据将由相同值的样本对组成。不会有关于回转或沉降的信息。有两个时域图,上面的图夸大了大约 125 倍。上图显示了这种情况在由点组成的图中的重叠性质,放大到双极零点附近的区域。

复杂性的批评与辩护

对这个电路以及本系列中其他电路最激烈的批评是复杂性。有几个基本事实强加了这种程度的复杂性。高线性度需要放大器的高GBWP,不幸的是,这意味着大量的噪声带宽。ADC的输入带宽为200MHz,或27个奈奎斯特区,频率为15Msps。如果采样受到放大器的整个带宽的影响,假设噪声密度是平坦的,则放大器的噪声将比限制在1奈奎斯特区的噪声大14.3 dB*。*(10log(200/7.5)=14.3 dB) 由于放大器占主导地位,这将接近 14 dB 的损失。这意味着必须对输出进行滤波才能获得高SNR的优势。但是,您不能将 BW 限制为 1 奈奎斯特区并获得快速稳定。大约需要奈奎斯特 BW 的 3-5 倍。将带宽从ADC的全200MHz带宽限制到约37MHz,仍然有7 dB的优势。这是 5 个奈奎斯特区,其中包括奈奎斯特方波的 5 次谐波。虽然需要降低噪声带宽,但具有陡峭过渡带或阻带中深零点的滤波器会响应突然的阶跃而振铃。

驱动ADC时,滤波器的建立有两个方面发挥作用;对输入波形的脉冲响应(与RF工程师的S21相关),以及对从ADC接收瞬变的响应反射(S22)。在双端口反射滤光片中,这些是密切相关的。在吸收式过滤器或可被视为多端口过滤器的过滤器中,这些过滤器可以在一定程度上彼此分离。吸收式滤波器对于实现直接采样ADC的全部性能至关重要。但是,它们往往更复杂。

响应来自LTC2387的干扰而建立的可用时间为1/fs-39nsec,或27 nsec(15Msps)。一个枯燥的推理表明,LT1396的25 nsec建立就足以满足这种情况。但是,放大器必须从ADC的角度建立,同时通过限带滤波器的延迟响应进行交互,同时驱动滤波器的复阻抗。此外,相互依赖的放大器可延长相对于单个放大器的建立时间。然而,差分输入级由两个CFA组成,与由电压反馈放大器组成相比,其相互依赖性要小得多。为了可视化这种效果,例如对于单端输入信号,驱动放大器反相输入端的信号由输入级直接缓冲,就像发射极跟随器一样,并注入相反的放大器,充当反相放大器。这一方面显著改善了响应快速输入阶跃的初始建立。然而,令人高兴的是,滤波器减轻了反射到放大器中的干扰。为了直接采样ADC的高线性度,以及成像应用,可能需要输出网络的快速建立,以消除采样过程中的任何非线性电荷,以及成像应用,也许是为了降低模式噪声。这通常意味着高斯吸收滤波器。不幸的是,吸收式滤光片通常比反射滤光片复杂2-3倍。在这样的驱动器中实现最佳阻尼需要一个具有脉冲响应的滤波器,该滤波器在两个方向上完全按照所需的建立时间建立,也许要考虑放大器的压摆率。如果压摆率不对称,则不太可能在两个偏移的建立和带宽之间实现最佳权衡,并且滤波器的建立速度必须更快。假设对称回转,滤波器本身的最佳脉冲响应将是涉及放大器摆动的脉冲响应,而不是理想的步进。但是,如果放大器的压摆率限制在某个幅度以上,这将意味着针对不同的偏移提供不同的解决方案。因此,在放大器之前需要一些压摆率限制,由C16和C17确定。如果在放大器之前限制压摆率,使放大器远离压摆率限制,则滤波器应针对任何幅度偏移保持一致,并且更容易在软件中进行校正。使放大器远离压摆限制还可以防止输入端产生较大的误差电压,使其远离非线性操作,并避免延长恢复过程。

共模伺服必须工作在一对看似实际阻抗而不是无功阻抗的节点中,因此,输出滤波器再次比简单的反射滤波器稍微复杂一些。由单个放大器控制的这两个节点必须在复阻抗方面匹配,否则会将该放大器的共模误差和噪声转换为差分元件,并被ADC看到。

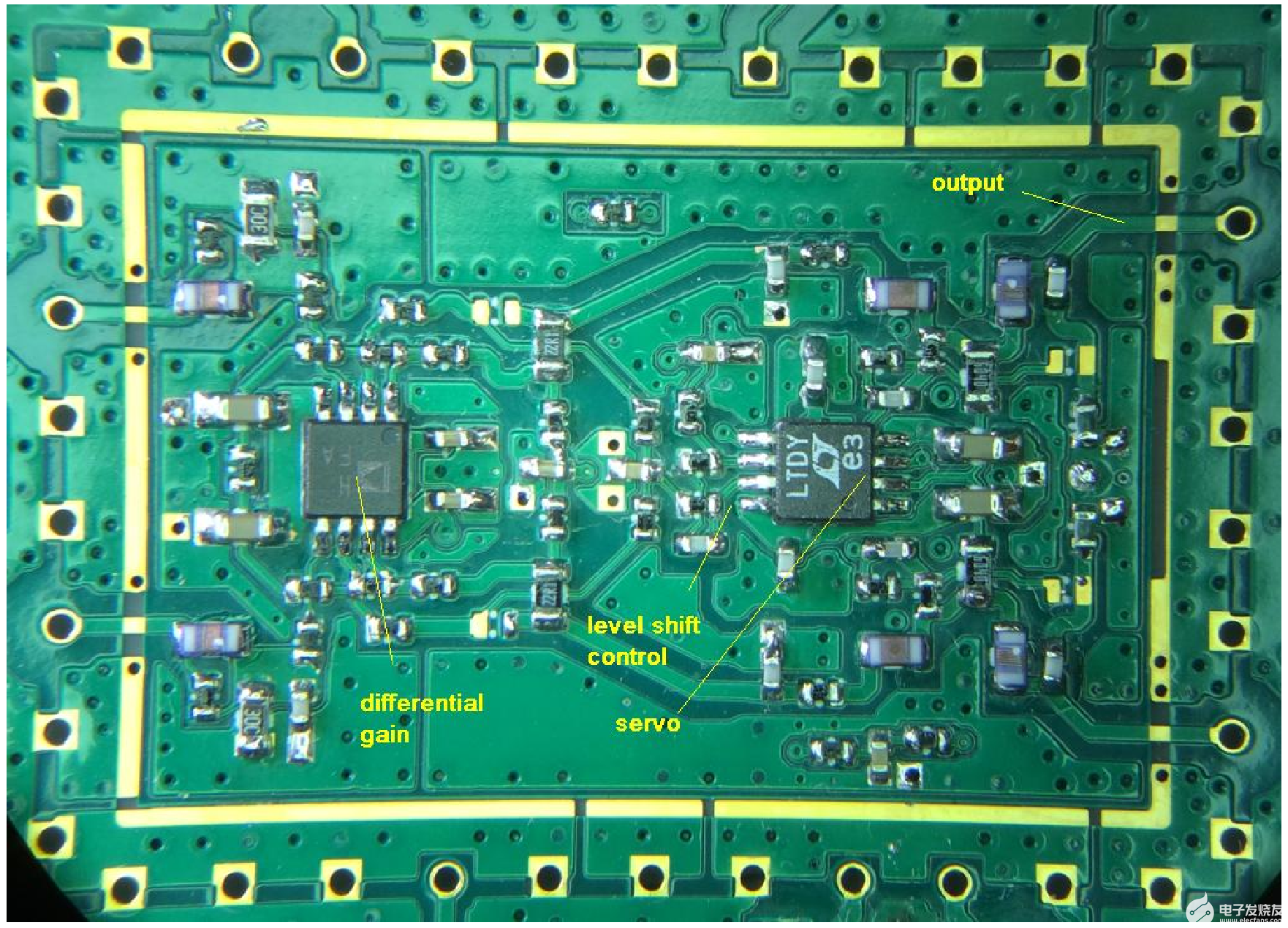

传输线上反射的控制,以及将高速路径与低速共模环路隔离的其他元素也增加了复杂性。该原型板旨在使我们能够评估采用 MS8 封装的 LT1396 与 AD8008 以及其他器件。还有其他具有不同引脚布局的器件,它们建立速度更快,噪声更低,并且可能更适合产生紧凑的布局。已经考虑使用电阻器阵列,这可能会产生更紧凑的布局。如果对此电路感兴趣,可以提供帮助,并且可以以空白或部分填充的形式提供现有电路板。必须针对每个传感器和应用评估此驱动程序的适用性。但是,这种拓扑的动态范围和快速建立可能无需为每种类型的传感器进行定制。该声明假设增益足够低,可以容纳预期的最高信号电平。

其他应用

对于某些应用,放弃ADC输入范围的一半并使用单极性驱动可能是有意义的。请注意,这意味着ADC使用0V-4.096V差分驱动,而不是单端驱动。如果一个假设的成像设备在“黑暗”中具有最低的噪声密度,我们称之为黑暗,黑暗可以放置在双极零度。这意味着无需注入大规模偏移,这是1/f噪声的另一个潜在来源。LTC2397 的 1/f 区域在双极性零点时非常低,在接近全标度时则不那么低。从理论上讲,考虑到放大器的5个奈奎斯特噪声带宽区的折叠,在增益降低的情况下,使用一半的输入范围时,AD8008的1/f转折频率应约为1000 Hz,LT1396的1/f转折频率应约为10 Hz,而AD8002的双极性零时可能只有约10 Hz。

当基准电压源的灵敏度最大化(接近满量程)时,ADC的1/f转折不是那么低。1/f 转角约为 15KHz,内部基准基于接近满量程的直流测量。AD8002版本的1/f角在零点处确实明显更好。

请参阅第四部分文章,了解如何在整个范围内驱动 LTC2387 基准以实现低 1/f。

使用输入级时,一个输入为0V,另一个输入接收以地为参考的单极性信号,可能需要对共模舵机和电平转换控制进行一些更改。我应该为伺服系统使用两个单放大器,因为这会使电路板更加灵活。如果电平转换控制能够使用更负的电源轨,输出共模伺服可能采用单个正电源,则输入级的噪声增益可以更好地保留。

以这种单极性方式使用,这很像本系列的第三部分,即跨阻应用,但用于更快的上升时间或更短的脉冲。然而,这仅适用于脉冲或像素与采样同步的应用,例如源自与采样同步的脉冲激励。如果增益下降2倍,在AD8008版本中,仅使用ADC范围的1/2,SNR仍将约为88dB,而ADC现在占主导地位,放大器的贡献基本上下降了6dB。

审核编辑:郭婷

-

传感器

+关注

关注

2551文章

51097浏览量

753556 -

CMOS

+关注

关注

58文章

5718浏览量

235500 -

驱动器

+关注

关注

52文章

8236浏览量

146363

发布评论请先 登录

相关推荐

什么是逻辑驱动器

LTC2387-18正弦信号驱动器的设计要求

电机驱动器是什么

如何驱动LTC2387基准

LTC2387驱动器:用于成像的驱动器

LTC2387驱动器:用于成像的驱动器

评论