实验存储系统设计实验

本次实验只有两道题目,但其实具有一定难度,这两题分别为汉字字库存储芯片扩展实验和MIPS寄存器文件设计,这次实验利用logisim进行设计,实验报告分为两个主要部分,在这两个部分中依次对两个实验的方案设计,设计思路进行了介绍。

字库存储芯片扩展实验

1.1设计要求

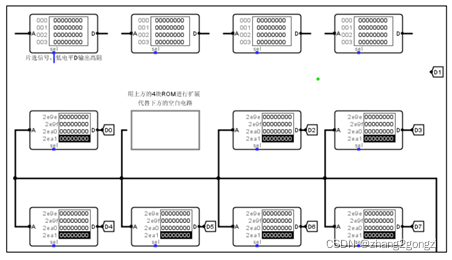

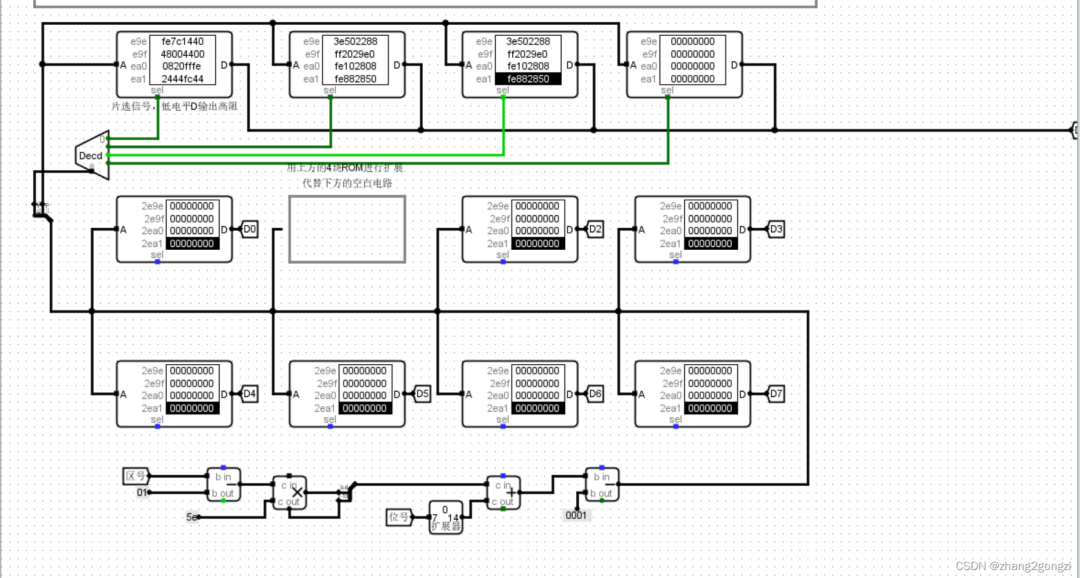

现有如下 ROM 组件,4片4K32位 ROM ,7片 16K32位 ROM,实验中有一个 16*16 点阵字库文件(存储字库的存储系统),由 7 片 16K× 32 位 ROM 和一个空白器件构成。空白处表示缺少一个器件,请按照字扩展(容量扩展,地址线扩展)的方式利用图中第一行所给出的 4 片 4K×32 位 ROM 的 存储器完成最终字库存储器,并把字库数据进行简单的分割后,存入这 4 片 4K ×32 位的 ROM 中。

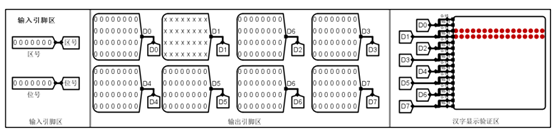

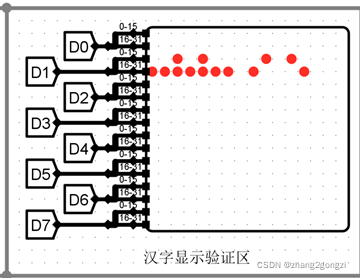

字库电路输入输出引脚如图所示,输入引脚是 7 位的区号和位号;输出 引脚是 32 位的 D7~D0,每一个输出都是 32 位的汉字点阵信息,用于连接到汉 字点阵输入端(拆分为高低 16 位)

1.2设计原理

1.2.1 字括展

由题目得,要求我们用4片4K×32 位ROM按照字扩展的括展方式实现16K×32位ROM,因此这边给大家介绍一下字括展的原理

字括展也称为容量括展或地址总线括展,当存储芯片的存储容量不能满足存储器对存储容量的要求时,需要进行字括展的方式来括展,其中需要将所有存储芯片的数据线,读写控制线各自并联,同时分别与CPU的数据线和读写控制线连接,各存储芯片的片选信号可以由CPU多余的地址线通过译码器译码产生,通过计算得出,为实现上图电路,共需要16K/4K=4个ROM芯片实现

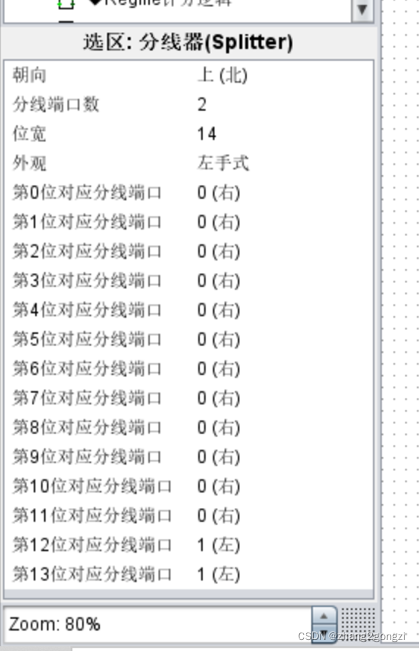

1.2.2 地址线连接

cpu分为地址线、数据线和控制线,地址线是用来传输地址信息用的,因为需要16K×32位的ROM系统,所以目标芯片中含有16K个地址,对应着14条地址线(2的14次方=16K),其中备用芯片12条地址线,高两位(分线器分开)用作片选,可以接到2-4译码器的输入端,在这边的话,需要分线器进行工作,将14个地址分开,分为低12位和高两位,对其进行编辑,将0-11设为0,其他位为1,高两位地址用于芯片的选择。

低 12 位地址直接连 4K×32b 的 ROM 芯片的地址线。4 个芯片的 32 位输出直接连到 D1,因为同时只有一个芯片工作,因此不会冲突

1.2.3 数据线连接

题目告诉我们,数据为32位,但输出LED矩阵位为16×16,所以说,该数据线应该有16位

每个16K×32b 的 ROM 的内部各自存储 16K 个地址,每个地址里存放 4 个字节数据。地址范围都一样:0x0000~0x3FFF

4 个 4K×32b 的 ROM,地址范围分别是也都一样:0x000~0xFFF,每个共有 4K个地址,现在需要把 16K×32b 的 ROM 中的数据按照顺序 每 4K 个为一组分为四组,分别放到 4 个 4K×32b 的 ROM 中去。HZK16_1 .txt 中的 1~4096 个数据放到 0 号 4K 的 ROM 中,4097~ 8192 个数据放到 1 号 4K 的 ROM 中,8193~12288 个数据放到 2 号 4K 的 ROM 中,12289~16384 个数据放到 3 号 4K 的 ROM 中

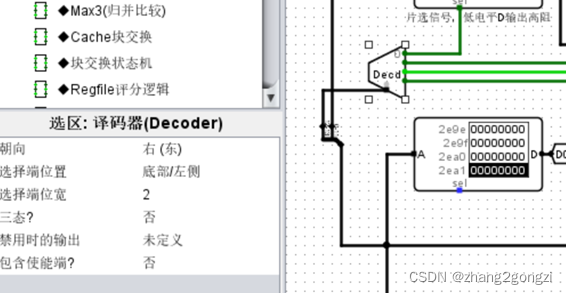

1.2.4 片选信号连接

在运行时,还需要对于片选信号线进行连接,将鼠标放置在上面,会得到相应的记录,如得到信号是1,不工作。对于连接片选信号线,可以选择译码器或是多路选择器,我选择的是译码器,连接原理为:将整个存储系统地址线的高位用于译码器的输入端,而译码器的输出端用于连接四个芯片各自合适的片选信号线。

在页面中增加一个译码器,数据位宽改为2,对于连发,需要进行讨论,对应的16K数据放置芯片位置,需要对应其译码器的连接

1.3实验步骤

1.理解题目,按照实验要求对四个4×32位的芯片进行字括展,使其成为16K×32位的芯片

2.了解数据线,地址线,片选信号的连接方式,然后进行连接

3.地址线通过分线器来进行分离,其中还需要对其中的数据进行调整,分为高2位和低14位,高位为1,低位为0

4.之后对于片选信号进行连接,加入译码器,其中译码器位宽为2,可选为00,01,10,11四个信号

5.进行编译测评,改正错误

1.4故障与调试

1.4.1 LED灯展示不正确

故障现象:LED无法正确明亮与熄灭

原因分析:结果检查,线条的连接没有问题,应该是只读存储器中,存储的数据存在问题,

解决方案:四个4K×32位的ROM当中,数据并不是平分的,并且对于不同的连接方式,前4k的数据需要放在不同的芯片当中

1.5测试与分析

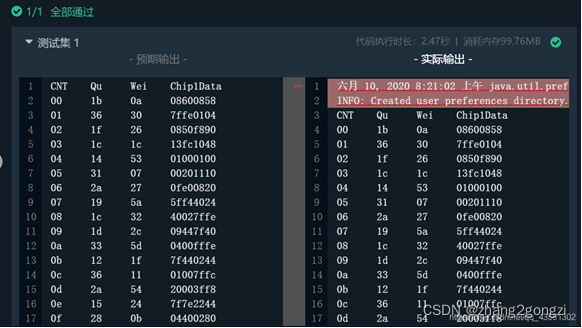

自行测试与头歌网测试皆正确

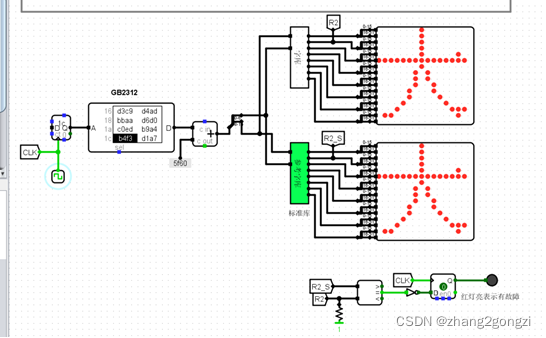

1.6最终电路图

MIPS寄存器文件设计

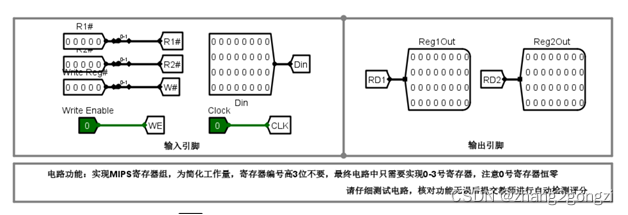

2.1设计要求

利用 Logisim平台构建一个简化的MIPS寄存器文件,内部包含 4个 32 位寄存器。通过 R1#、R2#给定两个寄存器的地址编号,就可以从右侧的 R1、R2 引脚 读读出对应寄存器的值。输入引脚还包括写入寄存器的编号 W#,数据写入引脚 Din,当写使能信号 WE 有效,时钟的配合下将数据总线上的数据通过 Din 端写入寄存器文件内部对 应的寄存器中具体引脚为下图所示

2.2设计原理

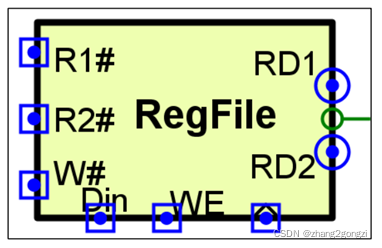

2.2.1 封装

首先需要看寄存器文件的封装,由输入引脚(R1,R2,W#,Din,WE,CLK时钟信号)

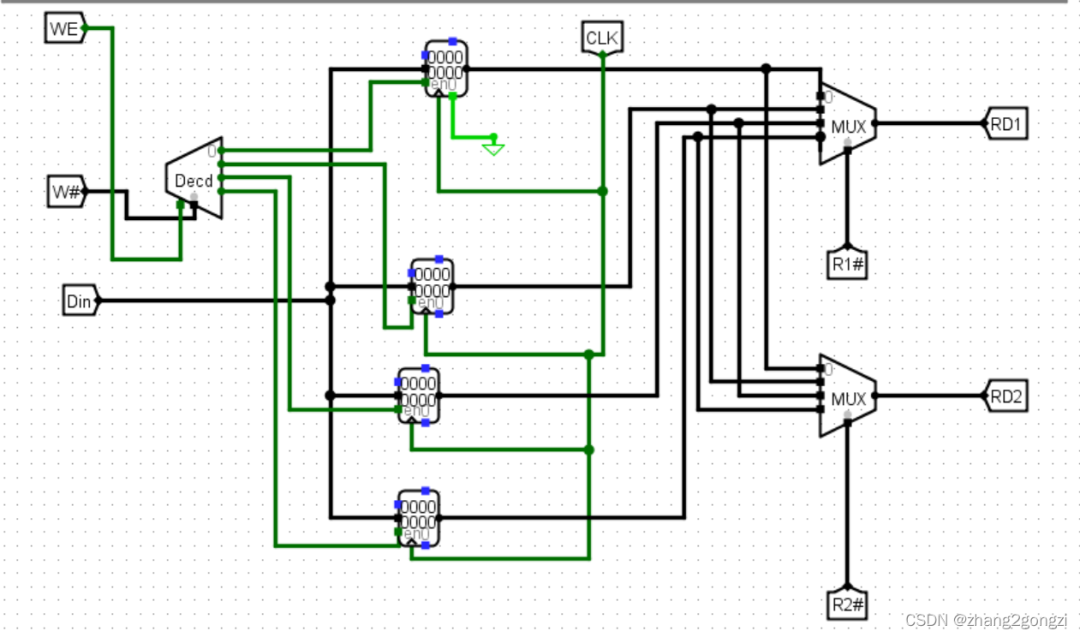

2.2.2 读控制电路设计

R1,R2分别为读寄存器的编号,我们寄存器设计好之后,一次可以读入两个寄存器里面的值,那么指定哪两个寄存器里面的值输出呢,那就需要我们通过R1#,R2#这两个信号,给出寄存器的编码,然后RD1,RD2分别是寄存器一二的数据输出引脚,它工作原理为,如果对寄存器文件进行读的话,可以读出寄存器中的值,寄存器由R1#,R2#的编号来指定是那两个寄存器,值由RD1,RD2进行输出。

由指令执行过程中,需要读两个寄存器的值,把他们送到目的寄存器中,所读寄存器的编号,由电路设计决定,为源寄存器中的编码决定的,由RD1,RD2进行输出。

数据输出可以根据 R1#、R2#的编码控制多路选择器进行选择输出。也可以采用译码器+三态门进行输出控制。由于这里需要同时读出两个寄存器,所以相关逻辑必须有两份。

2.2.3 写控制电路设计

W#这个输入引脚,是写寄存器的时候用,写寄存器时,要求WE,W#信号有效,然后数据从Din输入引脚写入数据,Din为32位,所有寄存器皆为32位。WE为写使能信号,数据必须由W#指定写入哪个寄存器,同时,WE有效,在时钟脉冲下,将Din端数据写到寄存器文件(由W#指定)中。

在指令执行时,通过分线器,将相应位提取出来,相应位代表着最终指令执行之后,想写入的目的寄存器的编号,数据送到Din端,然后RegWrite也就是写使能信号有效后,由CLK信号,把指定寄存器的数据,写入。

写入时根据 W#收到的写入寄存器编号,利用译码器或多路选择器选择具体 寄存器(写信号 WE 和译码信号同时有效时,令寄存器的使能端 en=1)

2.3实验步骤

(1)理解题目,按照实验要求进行电路连接

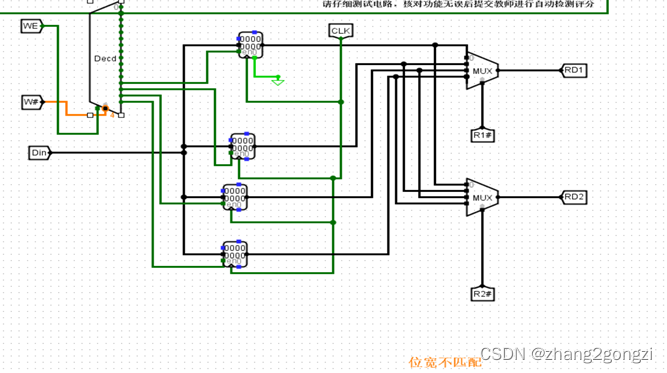

(2)W#为两位,可能值为00,01,10,11。当值不同时,选择不同寄存器,所以加入译码器,通过W#输出信号,由输出信号进行选择

(3)写信号还需要别的信号有效,才具备写入条件,如何控制写入寄存器,将WE和译码信号的值送入使能端,=1时,可以写入

(4)查看寄存器片选信号,如为1有效,为0无效

(5)同步置1和清零可不连,可以将电源连到地线,一直无效

(6)写入数据要把数据输出引脚连在对应寄存器输入引脚

(7)选择与门,并更改与门位宽,W#需要译码器,改为两位,W#连到译码器输入端,然后译码器四个输出引脚,WE是1时,W#如果也是1,与门相连

(8)按要求连接,进行测试

2.4故障与调试

2.4.1 位宽不匹配

故障现象:LED无法正确明亮与熄灭

原因分析:题目只给出四个寄存器,所以只需要两个位宽就足够

解决方案:将位宽改为2

2.5测试与分析

自行测试与头歌网测试皆正确

2.6最终电路图

审核编辑:汤梓红

-

寄存器

+关注

关注

31文章

5336浏览量

120230 -

计算机

+关注

关注

19文章

7488浏览量

87849 -

mips

+关注

关注

1文章

239浏览量

47749 -

存储系统

+关注

关注

2文章

409浏览量

40852 -

存储芯片

+关注

关注

11文章

896浏览量

43132

原文标题:【实践】头歌计算机组成原理存储系统设计实验报告(字库存储芯片,MIPS寄存器文件设计)

文章出处:【微信号:feifeijiehaha,微信公众号:电路和微电子考研】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

头歌计算机组成原理存储系统设计实验报告(字库存储芯片,MIPS寄存器文件设计)

头歌计算机组成原理存储系统设计实验报告(字库存储芯片,MIPS寄存器文件设计)

评论