1、概述

开关电源的设计是一份非常耗时费力的苦差事,需要不断地修正多个设计变量,直到性能达到设计目标为止。本文step-by-step 介绍反激变换器的设计步骤,并以一个6.5W 隔离双路输出的反激变换器设计为例,主控芯片采用NCP1015。

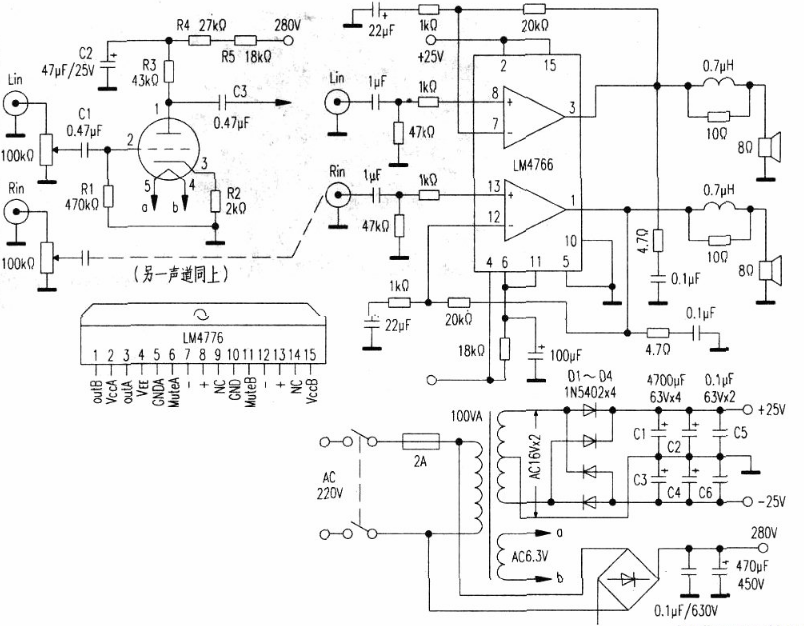

基本的反激变换器原理图如图 1 所示,在需要对输入输出进行电气隔离的低功率(1W~60W)开关电源应用场合,反激变换器(Flyback Converter)是最常用的一种拓扑结构(Topology)。简单、可靠、低成本、易于实现是反激变换器突出的优点。

2、设计步骤

接下来,参考图 2 所示的设计步骤,一步一步设计反激变换器

1.Step1:初始化系统参数

------输入电压范围:Vinmin_AC 及Vinmax_AC

------电网频率:fline(国内为50Hz)

------输出功率:(等于各路输出功率之和)

------初步估计变换器效率:η(低压输出时,η取0.7~0.75,高压输出时,η取0.8~0.85)根据预估效率,估算输入功率:

对多路输出,定义KL(n)为第n 路输出功率与输出总功率的比值:

单路输出时,KL(n)=1.

2. Step2:确定输入电容Cbulk

Cbulk 的取值与输入功率有关,通常,对于宽输入电压(85~265VAC),取2~3μF/W;对窄范围输入电压(176~265VAC),取1μF/W 即可,电容充电占空比Dch 一般取0.2 即可。

一般在整流后的最小电压Vinmin_DC 处设计反激变换器,可由Cbulk 计算Vinmin_DC:

3. Step3:确定最大占空比Dmax

反激变换器有两种运行模式:电感电流连续模式(CCM)和电感电流断续模式(DCM)。两种模式各有优缺点,相对而言,DCM 模式具有更好的开关特性,次级整流二极管零电流关断,因此不存在CCM 模式的二极管反向恢复的问题。此外,同功率等级下,由于DCM模式的变压器比CCM 模式存储的能量少,故DCM 模式的变压器尺寸更小。但是,相比较CCM 模式而言,DCM 模式使得初级电流的RMS 增大,这将会增大MOS 管的导通损耗,同时会增加次级输出电容的电流应力。因此,CCM 模式常被推荐使用在低压大电流输出的场合,DCM 模式常被推荐使用在高压 小电流输出的场合。

图 4 反激变换器

对CCM 模式反激变换器而言,输入到输出的电压增益仅仅由占空比决定。而DCM 模式反激变换器,输入到输出的电压增益是由占空比和负载条件同时决定的,这使得DCM 模式的电路设计变得更复杂。但是,如果我们在DCM 模式与CCM 模式的临界处(BCM 模式)、输入电压最低(Vinmin_DC)、满载条件下,设计DCM 模式反激变换器,就可以使问题变得简单化。于是,无论反激变换器工作于CCM 模式,还是DCM 模式,我们都可以按照CCM模式进行设计。

如图 4(b)所示,MOS 管关断时,输入电压Vin 与次级反射电压nVo 共同叠加在MOS的DS 两端。最大占空比Dmax 确定后,反射电压Vor(即nVo)、次级整流二极管承受的最大电压VD 以及MOS 管承受的最大电压Vdsmax,可由下式得到:

通过公式(5)(6)(7),可知,Dmax 取值越小,Vor 越小,进而MOS 管的应力越小,然而,次级整流管的电压应力却增大。因此,我们应当在保证MOS 管的足够裕量的条件下,尽可能增大Dmax,来降低次级整流管的电压应力。Dmax 的取值,应当保证Vdsmax 不超过MOS管耐压等级的80%;同时,对于峰值电流模式控制的反激变换器,CCM 模式条件下,当占空比超过0.5 时,会发生次谐波震荡。综合考虑,对于耐压值为700V(NCP1015)的MOS管,设计中,Dmax 不超过0.45 为宜。

4. Step4:确定变压器初级电感Lm

对于CCM 模式反激,当输入电压变化时,变换器可能会从CCM 模式过渡到DCM 模式,对于两种模式,均在最恶劣条件下(最低输入电压、满载)设计变压器的初级电感Lm。由下式决定:

其中,fsw 为反激变换器的工作频率,KRF 为电流纹波系数,其定义如下图所示:

对于DCM 模式变换器,设计时KRF=1。对于CCM 模式变换器,KRF<1,此时,KRF 的取值会影响到初级电流的均方根值(RMS),KRF 越小,RMS 越小,MOS 管的损耗就会越小,然而过小的KRF 会增大变压器的体积,设计时需要反复衡量。一般而言,设计CCM 模式的反激变换器,宽压输入时(90~265VAC),KRF 取0.25~0.5;窄压输入时(176~265VAC),KRF 取0.4~0.8 即可。

一旦Lm 确定,流过MOS 管的电流峰值Idspeak 和均方根值Idsrms 亦随之确定:

其中:

设计中,需保证Idspeak 不超过选用MOS 管最大电流值80%,Idsrms 用来计算MOS 管的导通损耗Pcond,Rdson 为MOS 管的导通电阻。

5. Step5:选择合适的磁芯以及变压器初级电感的匝数

开关电源设计中,铁氧体磁芯是应用最广泛的一种磁芯,可被加工成多种形状,以满足不同的应用需求,如多路输出、物理高度、优化成本等。

实际设计中,由于充满太多的变数,磁芯的选择并没有非常严格的限制,可选择的余地很大。其中一种选型方式是,我们可以参看磁芯供应商给出的选型手册进行选型。如果没有合适的参照,可参考下表:

选定磁芯后,通过其Datasheet 查找Ae 值,及磁化曲线,确定磁通摆幅△B,次级线圈匝数由下式确定:

其中,DCM 模式时,△B 取0.2~0.26T;CCM 时,△B 取0.12~0.18T。

6. Step6:确定各路输出的匝数

先确定主路反馈绕组匝数,其他绕组的匝数以主路绕组匝数作为参考即可。主反馈回路绕组匝数为:

则其余输出绕组的匝数为:

辅助线圈绕组的匝数Na 为:

7. Step7:确定每个绕组的线径

根据每个绕组流过的电流RMS 值确定绕组线径。

初级电感绕组电流RMS:

次级绕组电流RMS 由下式决定:

ρ为电流密度,单位:A/mm2,通常,当绕组线圈的比较长时(>1m),线圈电流密度取5A/mm2;当绕组线圈长度较短时,线圈电流密度取6~10A/mm2。当流过线圈的电流比较大时,可以采用多组细线并绕的方式,以减小集肤效应的影响。

其中,Ac 是所有绕组导线截面积的总和,KF 为填充系数,一般取0.2~0.3.

检查磁芯的窗口面积(如图 7(a)所示),大于公式 21 计算出的结果即可。

8. Step8:为每路输出选择合适的整流管

每个绕组的输出整流管承受的最大反向电压值VD(n)和均方根值IDrms(n)如下:

选用的二极管反向耐压值和额定正向导通电流需满足:

9. Step9:为每路输出选择合适的滤波器

第n 路输出电容Cout(n)的纹波电流Icaprms(n)为:

选取的输出电容的纹波电流值Iripple 需满足:

输出电压纹波由下式决定:

有时候,单个电容的高ESR,使得变换器很难达到我们想要的低纹波输出特性,此时可通过在输出端多并联几个电容,或加一级LC 滤波器的方法来改善变换器的纹波噪声。注意:LC 滤波器的转折频率要大于1/3 开关频率,考虑到开关电源在实际应用中可能会带容性负载,L 不宜过大,建议不超过4.7μH。

10. Step10:钳位吸收电路设计

如图 8 所示,反激变换器在MOS 关断的瞬间,由变压器漏感LLK 与MOS 管的输出电容造成的谐振尖峰加在MOS 管的漏极,如果不加以限制,MOS 管的寿命将会大打折扣。因此需要采取措施,把这个尖峰吸收掉。

反激变换器设计中,常用图 9(a)所示的电路作为反激变换器的钳位吸收电路(RCD钳位吸收)。

RClamp 由下式决定,其中Vclamp 一般比反射电压Vor 高出50~100V,LLK 为变压器初级漏感,以实测为准:

图 9 RCD 钳位吸收

CClamp 由下式决定,其中Vripple 一般取Vclamp 的5%~10%是比较合理的:

输出功率比较小(20W 以下)时,钳位二极管可采用慢恢复二极管,如1N4007;反之,则需要使用快恢复二极管。

11. Step11:补偿电路设计

开关电源系统是典型的闭环控制系统,设计时,补偿电路的调试占据了相当大的工作量。目前流行于市面上的反激控制器,绝大多数采用峰值电流控制控制模式。峰值电流模式反激的功率级小信号可以简化为一阶系统,所以它的补偿电路容易设计。通常,使用Dean Venable提出的Type II 补偿电路就足够了。

在设计补偿电路之前,首先需要考察补偿对象(功率级)的小信号特性。

如图8 所示,从IC 内部比较器的反相端断开,则从控制到输出的传递函数(即控制对象的传递函数)为:

附录分别给出了CCM模式和DCM模式反激变换器的功率级传递函数模型。NCP1015工作在DCM 模式,从控制到输出的传函为:

其中:

Vout1 为主路输出直流电压,k 为误差放大器输出信号到电流比较器输入的衰减系数(对NCP1015 而言,k=0.25),m 为初级电流上升斜率,ma 为斜坡补偿的补偿斜率(由于NCP1015内部没有斜坡补偿,即ma=0),Idspeak 为给定条件下初级峰值电流。于是我们就可以使用Mathcad(或Matlab)绘制功率级传函的Bode 图:

在考察功率级传函Bode 图的基础上,我们就可以进行环路补偿了。

前文提到,对于峰值电流模式的反激变换器,使用Dean Venable Type II 补偿电路即可,典型的接线方式如下图所示:

通常,为降低输出纹波噪声,输出端会加一个小型的LC 滤波器,如图 10 所示,L1、C1B 构成的二阶低通滤波器会影响到环路的稳定性,L1、C1B 的引入,使变换器的环路分析变得复杂,不但影响功率级传函特性,还会影响补偿网络的传函特性。然而,建模分析后可知:如果L1、C1B 的转折频率大于带宽fcross 的5 倍以上,那么其对环路的影响可以忽略不计,实际设计中,建议L1 不超过4.7μH。于是我们简化分析时,直接将L1直接短路即可,推导该补偿网络的传递函数G(s)为:

其中:

CTR 为光耦的电流传输比,Rpullup 为光耦次级侧上拉电阻(对应NCP1015,Rpullup=18kΩ),Cop 为光耦的寄生电容,与Rpullup 的大小有关。图 13(来源于Sharp PC817 的数据手册)是光耦的频率响应特性,可以看出,当RL(即Rpullup)为18kΩ时,将会带来一个约2kHz左右的极点,所以Rpullup 的大小会直接影响到变换器的带宽。

k Factor(k 因子法)是Dean Venable 在20 世纪80 年代提出来的,提供了一种确定补偿网络参数的方法。

如图 14 所示,将Type II 补偿网络的极点wp 放到fcross 的k 倍处,将零点wz 放到fcross的1/k 处。图 12 的补偿网络有三个参数需要计算:RLed,Cz,Cpole,下面将用k Factor 计算这些参数:

-------确定补偿后的环路带宽fcross:通过限制动态负载时(△Iout)的输出电压过冲量(或下冲量)△Vout,由下式决定环路带宽:

-------考察功率级的传函特性,确定补偿网络的中频带增益(Mid-band Gain):

-------确定Dean Venable 因子k:选择补偿后的相位裕量PM(一般取55°~80°),由公式 32 得到fcross 处功率级的相移(可由Mathcad 计算)PS,则补偿网络需要提升的相位Boost 为:

则k 由下式决定:

-------补偿网络极点(wp)放置于fcross 的k 倍处,可由下式计算出Cpole:

-------补偿网络零点(wz)放置于fcross 的1/k 倍处,可由下式计算出Cz:

3 仿真验证

计算机仿真不仅可以取代系统的许多繁琐的人工分析,减轻劳动强度,避免因为解析法在近似处理中带来的较大误差,还可以与实物调试相互补充,最大限度的降低设计成本,缩短开发周期。

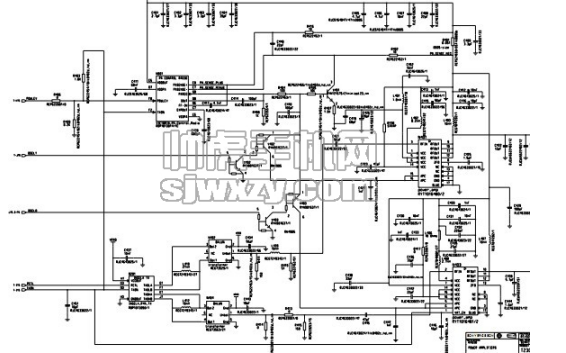

本例采用经典的电流型控制器UC3843(与NCP1015 控制原理类似),搭建反激变换器。其中,变压器和环路补偿参数均采用上文的范例给出的计算参数。

仿真测试条件:低压输入(90VAC,双路满载)

1.原理图

图 17 仿真原理图

2. 瞬态信号时域分析

从图 18 可以看出,最低Cbulk 上的最低电压为97.3V,与理论值98V 大致相符。

3. 交流信号频域分析

4. 动态负载波形测试

测试条件:低压输入,满载,主路输出电流0.1A---1A---0.1A,间隔2.5ms,测试输出电压波形。

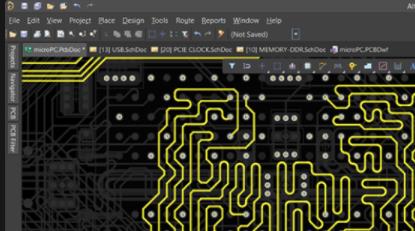

4 PCB 设计指导

1. PCB layout—大电流环路包围的面积应极可能小,走线要宽。

2. PCB layout—高频(di/dt、dv/dt)走线

a. 整流二级,钳位吸收二极管,MOS 管与变压器引脚,这些高频处,引线应尽可能短,layout 时避免走直角;

b. MOS 管的驱动信号,检流电阻的检流信号,到控制IC 的走线距离越短越好;

c. 检流电阻与MOS 和GND 的距离应尽可能短。

3. PCB layout—接地

初级接地规则:

a. 所有小信号GND 与控制IC 的GND 相连后,连接到Power GND(即大信号GND);

b. 反馈信号应独立走到IC,反馈信号的GND 与IC 的GND 相连。

次级接地规则:

a. 输出小信号地与相连后,与输出电容的的负极相连;

b. 输出采样电阻的地要与基准源(TL431)的地相连。

5. PCB layout—实例

6、总结

本文详细介绍了反激变换器的设计步骤,以及PCB 设计时应当注意的事项,并采用软件仿真的方式验证了设计的合理性。同时,在附录部分,分别给出了峰值电流模式反激在CCM 模式和DCM 模式工作条件下的功率级传递函数。

附录:峰值电流模式功率级小信号

对CCM 模式反激,其控制到输出的传函为:

峰值电流模式的电流内环,本质上是一种数据采集系统,功率级传函由两部分Hp(s)和Hh(s)串联组成,其中

Hh(s)为电流环电流采样形成的二阶采样环节(由Ray Ridley 提出):

其中:

上式中,PO 为输出总功率,k 为误差放大器输出信号到电流比较器输入的衰减系数,Vout1 为反馈主路输出电压,Rs 为初级侧检流电阻,D 为变换器的占空比,n 为初级线圈NP与主路反馈线圈Ns1 的匝比,m 为初级电流上升斜率,ma 为斜坡补偿的补偿斜率,Esr 为输出电容的等效串联电阻,Cout 是输出电容之和。

注意:CCM 模式反激变换器,从控制到输出的传函,由公式 40 可知,有一个右半平面零点,它在提升幅值的同时,带来了90°的相位衰减,这个零点不是我们想要的,设计时应保证带宽频率不超过右半平面零点频率的1/3;由公式 41 可知,如果不加斜坡补偿(ma=0),当占空比超过50%时,电流环震荡,表现为驱动大小波,即次谐波震荡。因此,设计CCM 模式反激变换器时,需加斜坡补偿。

对DCM 模式反激,控制到输出的传函为:

其中:

Vout1 为主路输出直流电压,k 为误差放大器输出信号到电流比较器输入的衰减系数,m为初级电流上升斜率,ma 为斜坡补偿的补偿斜率,Idspeak 为给定条件下初级峰值电流。

审核编辑:汤梓红

-

原理图

+关注

关注

1308文章

6372浏览量

236230 -

开关电源

+关注

关注

6478文章

8405浏览量

484859 -

电路设计

+关注

关注

6679文章

2474浏览量

206205 -

电路原理图

+关注

关注

40文章

348浏览量

38553

发布评论请先 登录

相关推荐

一套已经实现过的NE5532+LM3886 PCB功放

如何完整地设计一套硬件电路?

XMOS推出一套适合iPhone和iPod底座的参考设计

功放机电路图系列一(六款模拟电路设计原理图详解)

三联屏一套多少钱_配一套三联屏需要什么设备(电脑)

PT6303锂电池串联保护芯片的电路和锂电池充电电路原理图合集

整流电路故障检修的一套方法资料下载

altiumdesigner多少钱一套

如何设计一套电路原理图

如何设计一套电路原理图

评论