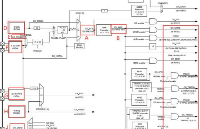

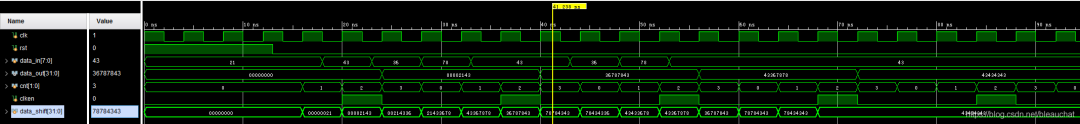

verilog模型举例

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:verilog的时钟分频与时钟使能

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1634文章

21832浏览量

608115

原文标题:verilog的时钟分频与时钟使能

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

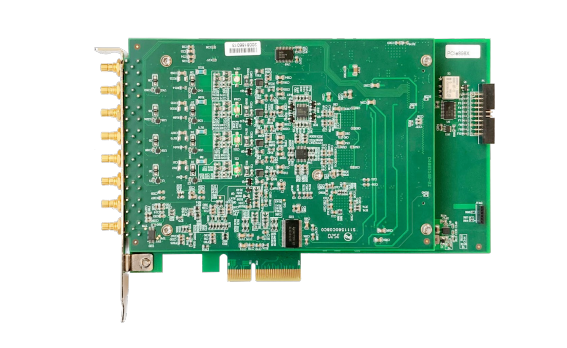

一文看懂!时钟在数据采集系统中究竟起到哪些关键作用?

等重要性能指标,因此合理选择时钟源对于优化系统性能至关重要。 时钟的分类 板载10M参考源 使用板载10MHz参考源,通过板载逻辑控制电路,并根据用户设置的分频比,生成相应的时钟信号。

时序约束一主时钟与生成时钟

一、主时钟create_clock 1.1 定义 主时钟是来自FPGA芯片外部的时钟,通过时钟输入端口或高速收发器GT的输出引脚进入FPGA内部。对于赛灵思7系列的器件,主

时钟抖动和时钟偏移的区别

时钟抖动(Jitter)和时钟偏移(Skew)是数字电路设计中两个重要的概念,它们对电路的时序性能和稳定性有着显著的影响。下面将从定义、原因、影响以及应对策略等方面详细阐述时钟抖动和时钟

【GD32 MCU 入门教程】GD32 MCU 常见外设介绍(1)RCU 时钟介绍

众所周知,时钟是MCU能正常运行的基本条件,就好比心跳或脉搏,为所有的工作单元提供时间 基数。时钟控制单元提供了一系列频率的时钟功能,包括多个内部RC振荡器

带时钟使能的八进制D型触发器SN54HCT377 SN74HCT377 数据表

电子发烧友网站提供《带时钟使能的八进制D型触发器SN54HCT377 SN74HCT377 数据表.pdf》资料免费下载

发表于 05-22 10:03

•0次下载

STM8L152xx使用LSI作为时钟源的时候,USART不能使用是怎么回事?

时钟

CLK_SYSCLKDivConfig(CLK_SYSCLKDiv_1);//不分频

CLK_SYSCLKSourceSwitchCmd (ENABLE);//使能切换

发表于 05-13 08:58

具有时钟使能端的八路 D 类触发器SNx4HC377数据表

电子发烧友网站提供《具有时钟使能端的八路 D 类触发器SNx4HC377数据表.pdf》资料免费下载

发表于 05-06 11:30

•0次下载

Verilog 电子时钟实现

在Verilog中实现一个简单的电子时钟,你可以使用一个计数器来周期性地递增一个计数值,然后根据这个计数值来显示时钟的不同时刻。以下是一个简单的例子:

module clock_display

发表于 03-26 07:48

verilog的时钟分频与时钟使能

verilog的时钟分频与时钟使能

评论