做动态仿真验证通常会遇到要等待仿真结果的情况,特别是在调试某个测试用例的时候。很多时候,工程师们会自然地认为仿真速度大部分依赖于跑仿真任务的服务器本身的性能,以及EDA仿真工具的能力。而实际上,高效的验证环境以及代码质量也是影响仿真速度的关键因素。

另一方面,提高仿真速度这回事,对于芯片工程师来说本身就是“求人不如求己”。提高服务器机器性能意味着更大的资金投入,更高性能的仿真工具也不是一时半会能达成的。而探索更高效的验证方法学,构建更高执行效率的代码是当下就能做的事情。

本文的主要内容参考来自于Cliff Cummings在2019年DVCon会议上发表的文章:Yikes! Why is My SystemVerilog Still So Slooooow. 这篇文章主要探讨了SystemVerilog仿真速度跟Coding风格之间的关系,文章中有详细的实验目标、方法和数据结果呈现。本文将摘录和分析那些对仿真速度影响较大的编码风格。

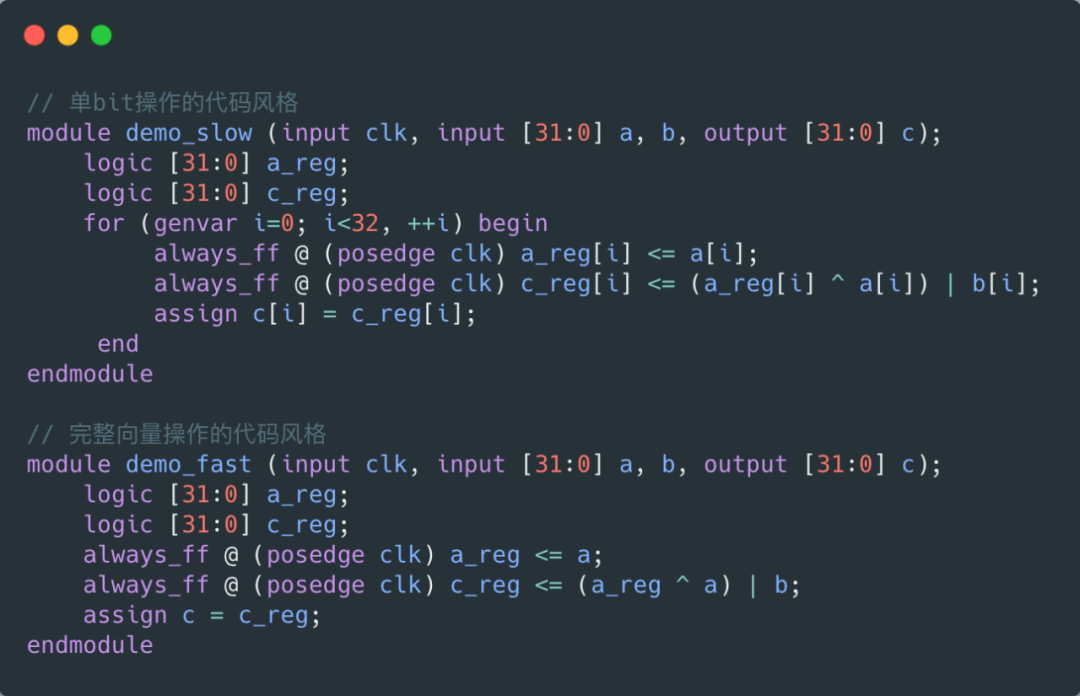

使用向量操作代替单bit操作

仿真器在做完整向量计算的速度比单bit计算要高。根据参考文献的数据,在某款仿真工具下,最高提速可以达到3倍以上。

下面是一个例程,分别呈现不同的代码实现风格。

避免在循环中实例化对象

这个技巧关系到内存的分配和回收。低效的内存管理会导致严重的cache miss、堆栈管理开销和垃圾回收开销,尽管这些都是操作系统帮我们做的。

当我们需要一种新的数据结构时,可以使用结构体struct就不用class,类的例化和垃圾回收都是开销。创建一个对象的时候,不要上来就是一个new,可以考虑是否可以重用之前创建过的对象。

如下例程,应用这个技巧在三款主流仿真工具上都能带来仿真速度收益,最高有超过一半的速度提升。

条件判断字符串处理

在仿真过程中不断地打印信息或者读写文件会导致仿真速度非常慢,毕竟调用计算机IO效率并不高。在UVM中有健全的report管理机制,可以根据设定的verbosity等级来判断是否需要打印信息出来。

除了信息打印,字符串的格式处理也是很大的开销。如果借用report的管理机制来判断是否有必要进行字符串格式处理,可以非常有效地提高仿真速度。

如下例程,带有条件判断的代码在三款主流仿真工具上都能带来仿真速度收益,而且这个收益非常大,达到了33倍~100倍。

减少不必要的端口采样或驱动

这是另一种减少不必要操作的技巧。要知道在UVM中,操作TLM analysis port是开销比较大的,因为端口的驱动行为,都会通过回调机制来执行关联到该端口的所有consumer的端口动作。理解这个实现机制,其实还得看看UVM的源码,这里就不做展开解析了。

此外,某些个analysis port是否连接到其他component是依赖于当前的验证环境的,如果根据analysis port的状态判断是否进行端口驱动,可以减少一些不必要的操作。

如下例程,在monitor的run_phase中根据其analysis port状态来进行端口采样和广播给其他组件,可以带来一部分的仿真速度收益。

用回调函数代替低效的随机约束

SystemVerilog提供了很多种随机化变量和添加随机约束的方法,具体可以参考公众号的另外两篇文章《暗藏玄机的SV随机化》《五花八门的SystemVerilog随机约束》。在设计随机约束的时候,除了要确保约束不冲突(即约束有解)之外,还需要避免产生无效的约束解。

其实,SV已经提供了pre_randomize() / post_randomize()两个分别在求解随机值前后会执行的回调函数。灵活使用这两个函数可以避免一些非常低效的约束行为。

如下例程,使用post_randomize对随机后的数列进行排序,可以避免在约束中使用循环去限制每一个数列元素,从而获得数十倍的仿真速度提升。

参考文献

[1] Cliff Cummings, John Rose, Adam Sherer. "Yikes! Why is My SystemVerilog Still So Slooooow." (2019)

[2] IEEE Standard Association. "IEEE Standard for SystemVerilog-Unified Hardware Design, Specification, and Verification Language." (2013).

审核编辑 黄昊宇

-

仿真

+关注

关注

50文章

4070浏览量

133552 -

服务器

+关注

关注

12文章

9123浏览量

85331 -

eda

+关注

关注

71文章

2755浏览量

173205

发布评论请先 登录

相关推荐

SystemVerilog中的类构造函数new

[启芯公开课] SystemVerilog for Verification

如何用questasim进行systemverilog仿真

round robin 的 systemverilog 代码

SystemVerilog Assertion Handbo

SystemVerilog的断言手册

SystemVerilog的正式验证和混合验证

如何利用SystemVerilog仿真生成随机数

SystemVerilog中枚举类型的使用建议

一些有趣的数组相关的SystemVerilog约束

解码国产EDA数字仿真器系列之二 | 如何实现全面的SystemVerilog语法覆盖?

一些有趣的数组相关的SystemVerilog约束

如何实现全面的SystemVerilog语法覆盖

一些个SystemVerilog高效仿真技巧

一些个SystemVerilog高效仿真技巧

评论