负载效应 (loading) 的控制对良率和器件性能有重大影响,并且它会随着 FinFET(鳍式场效应晶体管)器件工艺的持续微缩变得越来越重要。当晶圆的局部刻蚀速率取决于现有特征尺寸和局部图形密度时,就会发生负载效应。刻蚀工艺 loading 带来的器件结构上的微小变化可能会对器件良率和性能产生负面影响,例如在伪栅多晶硅刻蚀过程中,由于刻蚀的负载效应,可能会在栅极和鳍结构交叉区域产生多晶硅边角残留,进而造成 FinFET 结构的改变,并直接影响 FinFET 栅极的长度和电学性能。多晶硅边角残留对良率和器件性能的影响,包括可接受的残留的尺寸大小,可使用 SEMulator3D提前预测。

FinFET器件的多晶硅边角残留

建模和工艺窗口检查

多晶硅边角残留会在鳍片栅极交叉区域产生金属栅极凸起。这些凸起可以在许多不同的 FinFET 节点上找到,多晶硅边角残留通常在伪栅多晶硅刻蚀工艺中形成。

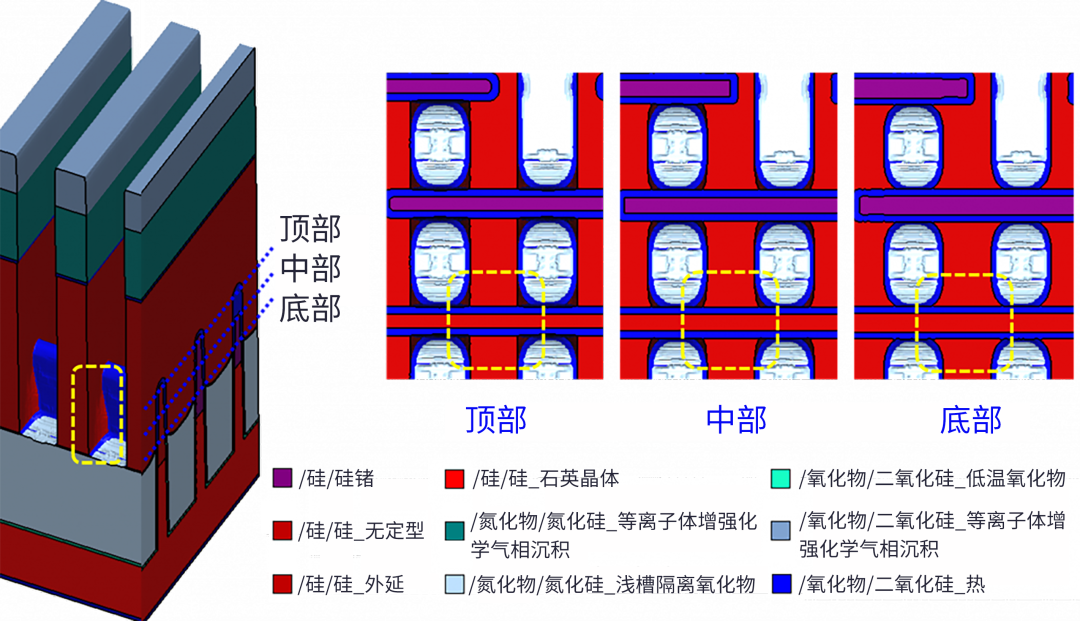

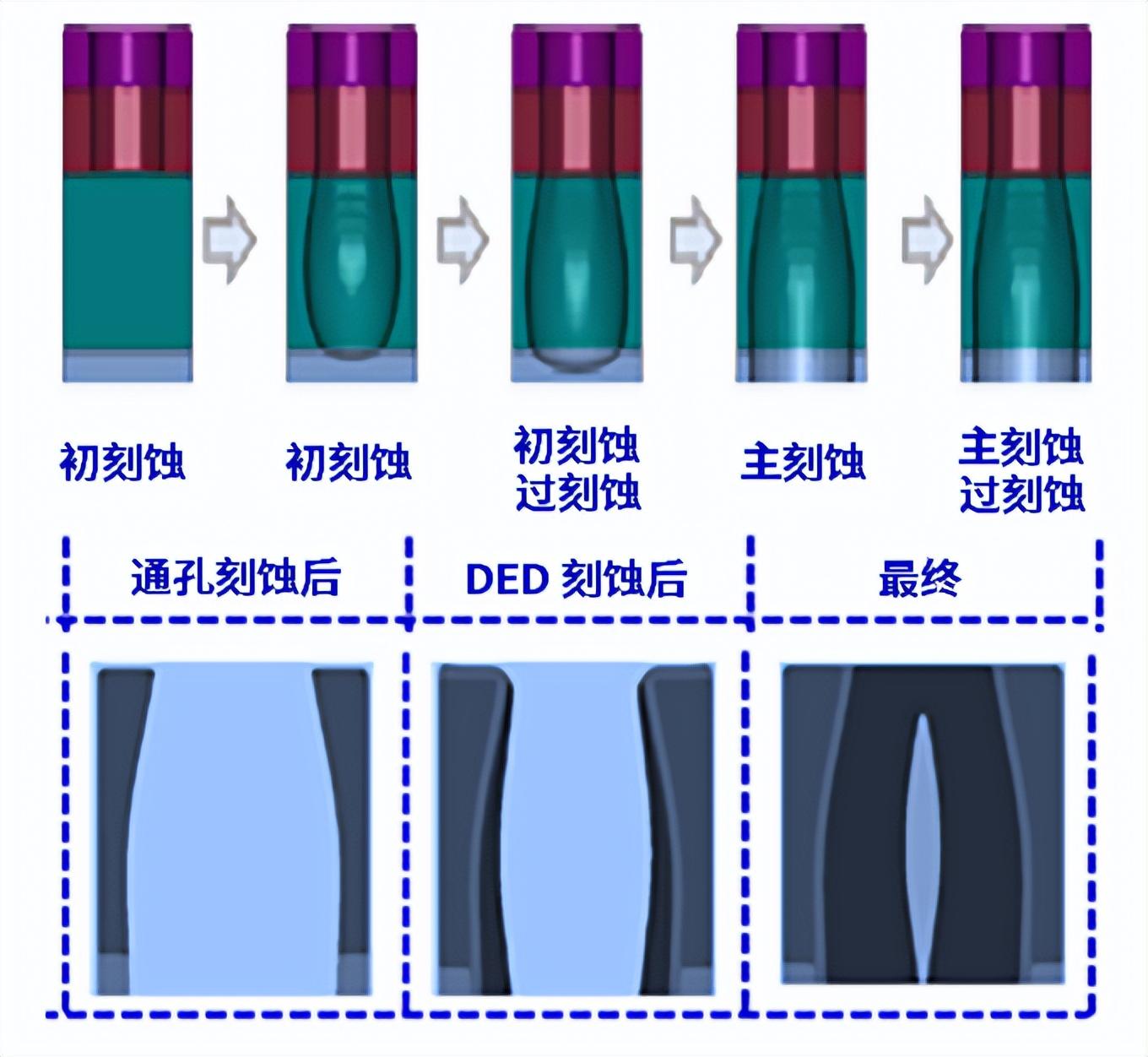

图1:在不同高度生成的3D边角残留及其轮廓

我们在 SEMulator3D 中构建了一个使用 SRAM111 结构的 5nm logic 虚拟工艺模型,以研究多晶硅刻蚀残留的行为。在这个模拟的多晶硅刻蚀工艺中,SEMulator3D 使用了图形负载刻蚀来模拟多晶硅残留轮廓。图1(左)显示了计算机生成的多晶硅残留结构,不同高度(鳍片顶部、中部和底部)的多晶硅轮廓见图1(右)。

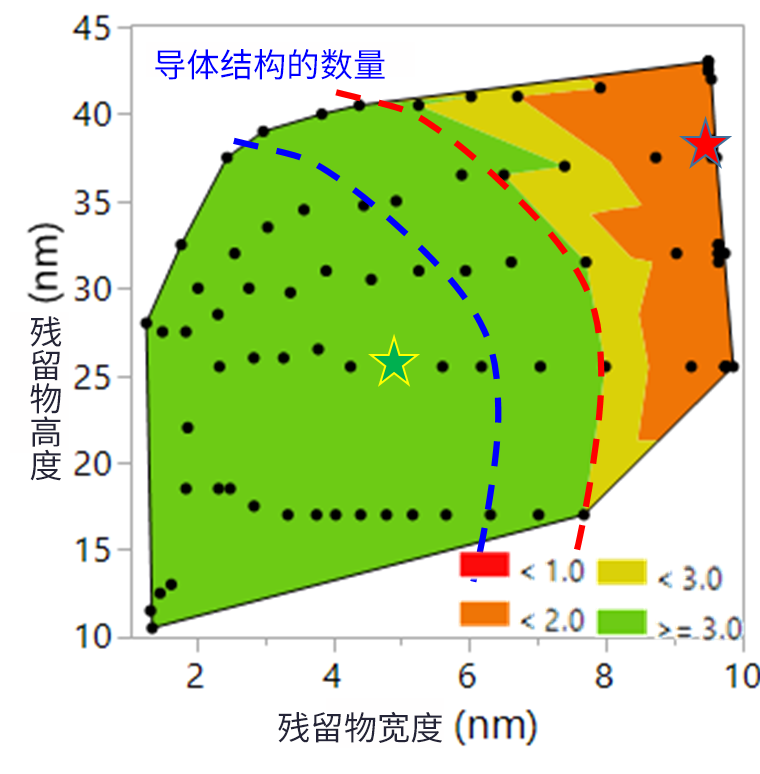

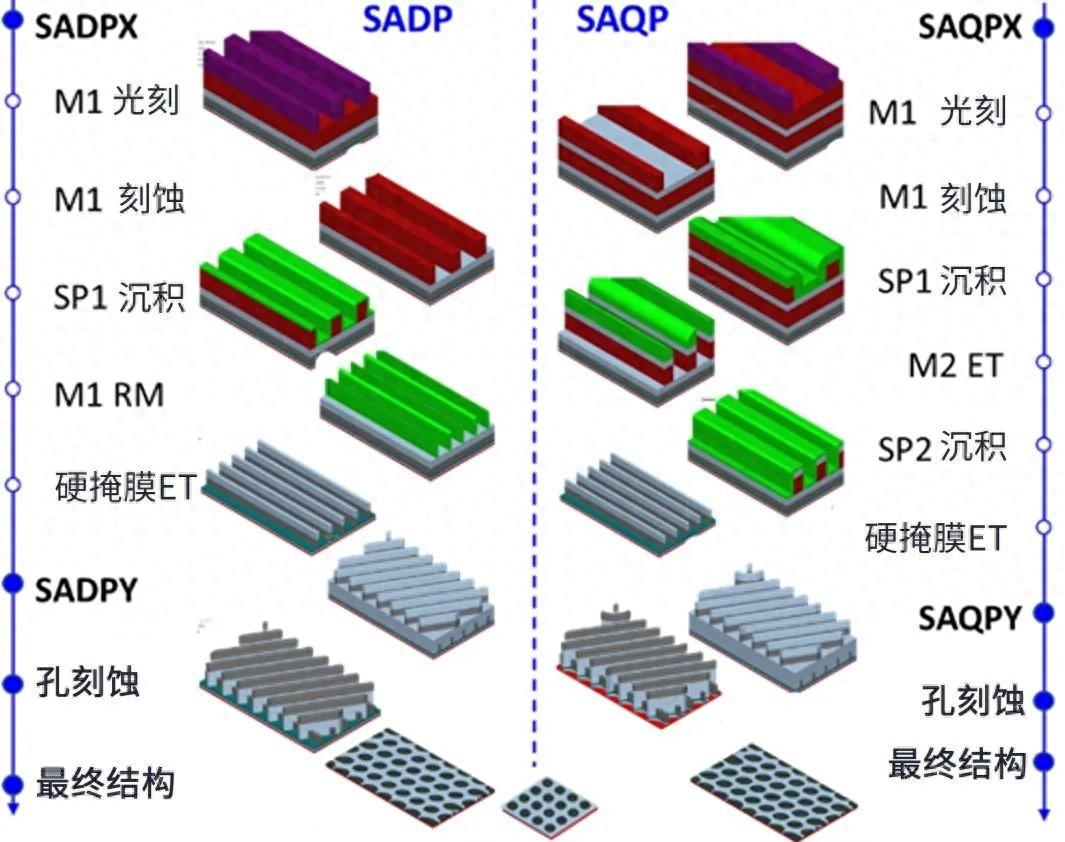

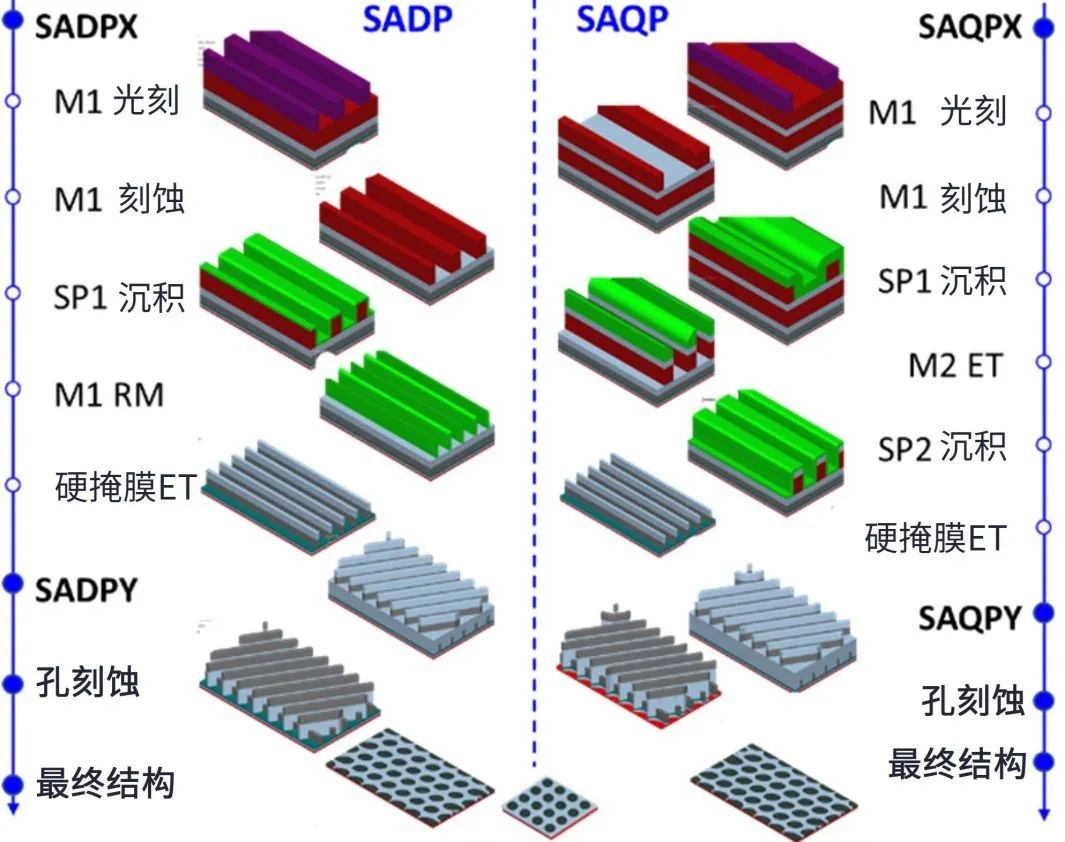

在该模拟器件发生结构硬失效(如短路)之前,多大的多晶硅边角刻蚀残留是可以被接受的,可以通过在虚拟 DOE(实验设计)中测试100种残留宽度和高度的组合来研究这个问题。我们测量了虚拟制造过程中关键步骤的导体结构数量,作为了解器件中是否有短路或故障(如源漏外延与伪栅多晶硅之间的短路)的一个指标 。如果残留物太大并使伪栅多晶硅与源漏外延层短接,那么结构中导体结构 (net) 的数量将小于3。图2所示的等高线图包含不同残留宽度和高度下的导体结构数量,绿色区域显示,可以把器件源漏栅3个导体结构区分开的器件结构。考虑到残留宽度和高度的潜在制造差异(可能分别为1.5nm和5nm),安全的工艺窗口需要往左下方做适当平移(如蓝色虚线所示)。

图2:包含不同残留物宽度和高度下导体结构数量的等高线图

多晶硅边角残留

对FinFET器件性能的影响

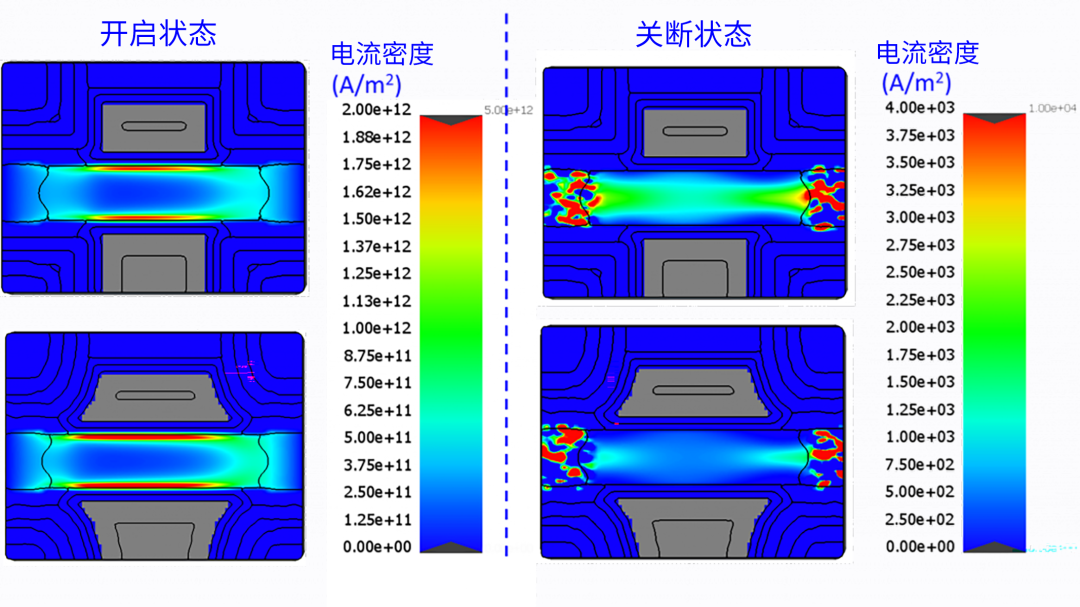

使用可接受的多晶硅残留(没有硬失效)之后,我们模拟了器件电学性能。结果表明,较大的残留实际上有益于开启状态下的驱动电流提升、关断状态下漏电流、亚阈值摆幅和漏致势垒下降 (DIBL) 的减小。与无残留的理想结构相比,它可以通过更高的开启状态电流 (108%) 和更低的关断状态漏电流 (50%) 提高器件性能。为了进一步了解该器件性能提升的机制,我们研究了存在较大残留时鳍片底部的开启和关断状态下的电流密度分布(见图3)。

开启状态时,如果存在多晶硅残留,通道长度会加大,残留覆盖了源极/漏极和栅极之间的部分串联电阻区,从而使这个区域的串联电阻减小,导致驱动电流增大;器件关断时,源极和漏极之间的大部分鳍片区域都可以由栅极控制。因此,当存在多晶硅残留时,源极和漏极之间的电阻较高,并带来较低的关断漏电流。

图3:鳍片底部的通/断态电流分布(上图:无残留,下图:有残留)

结论

本文中,我们使用了 Coventor SEMulator3D 来研究 5nm FinFET 工艺中的工艺窗口以及多晶硅边角刻蚀残留对器件性能的影响。这项研究帮助我们更好地了解不同伪栅多晶硅残留尺寸下可接受的工艺窗口和相关器件性能。我们的研究表明,不必追求多晶硅边角残留的最小化,而是可以通过控制多晶硅残留的尺寸,在不损失良率的同时获得器件性能的提升。

审核编辑:汤梓红

-

晶体管

+关注

关注

78文章

10439浏览量

148605 -

FinFET

+关注

关注

12文章

262浏览量

92364 -

负载效应

+关注

关注

0文章

17浏览量

2987

原文标题:使用虚拟实验设计预测先进FinFET技术的工艺窗口和器件性能

文章出处:【微信号:泛林半导体设备技术,微信公众号:泛林半导体设备技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

5nm及更先进节点上FinFET的未来:使用工艺和电路仿真来预测下一代半导体的性能

借助虚拟工艺加速工艺优化

labview实验设计

基于labview的高频电子虚拟实验设计

基于FinFET IP的数据转换器设计

实验设计基础

Xilinx与台积电合作采用16FinFET工艺,打造高性能FPGA器件

使用虚拟实验设计加速半导体工艺发展

使用虚拟实验设计加速半导体工艺发展

技术报告 | Gate 和 Fin Space Variation 对应力调制及 FinFET 性能的影响

使用虚拟实验设计预测先进FinFET技术的工艺窗口和器件性能

使用虚拟实验设计预测先进FinFET技术的工艺窗口和器件性能

评论