许多当前的无线电架构都包含下变频级,可将RF或微波频段向下转换为中频以进行基带处理。无论最终应用如何,无论是通信、航空航天和国防,还是仪器仪表,感兴趣的频率都在向射频和微波频谱推高。这种情况的一种可能解决方案是使用越来越多的下变频级,如图1所示。但是,另一种更有效的解决方案是利用带有集成数字下变频器(DDC)的RF ADC,如图2所示。

将DDC功能与RF ADC集成,无需额外的模拟下变频级,并允许RF频域中的频谱直接转换为基带进行处理。RF ADC能够在千兆赫兹频域中处理频谱,从而减轻了在模拟域中执行潜在的多次下变频的需要。DDC的能力允许频谱的连续性以及通过抽取滤波进行滤波,这也提供了改善频带内动态范围(增加SNR)的优势。

图2.使用带DDC的RF ADC的接收器信号链。

本文主要重点介绍AD9680(以及AD9690、AD9691和AD9684)中的DDC功能。为了了解DDC功能以及如何分析DDC与ADC配合使用时的输出频谱,我们将以AD9680-500为例。作为辅助手段,将使用ADI公司网站上的频率折叠工具。这个简单而强大的工具可用于帮助理解ADC的混叠效应,这是分析集成DDC(如AD9680)的RF ADC输出频谱的第一步。

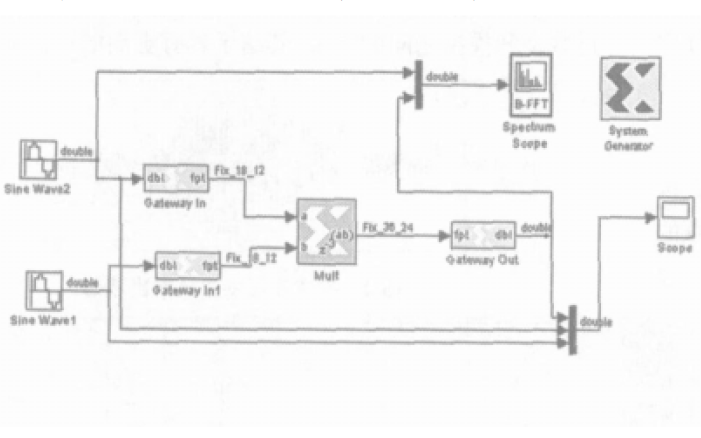

在本例中,AD9680-500采用368.64 MHz输入时钟和270 MHz模拟输入频率工作。首先,了解AD9680中数字处理模块的设置非常重要。AD9680将设置为使用数字下变频器(DDC),其中输入为实数,输出为复数,数控振荡器(NCO)调谐频率设置为98 MHz,半带滤波器1(HB1)使能,6 dB增益使能。由于输出很复杂,因此禁用了复数到实际的转换块。DDC 的基本示意图如图 3 所示。为了理解输入音调的处理方式,重要的是要了解信号首先通过NCO,NCO在频率上移动输入音调,然后通过抽取,可以选择通过增益模块,然后选择性地通过复数到实际转换。

图3.AD9680中的DDC信号处理模块。

了解流经AD9680的信号流的宏观视图也很重要。信号通过模拟输入进入,通过ADC内核进入DDC,然后通过JESD204B串行器,然后通过JESD204B串行输出通道输出。图4所示AD9680的框图对此进行了说明。

图4.AD9680原理框图

输入采样时钟为368.64 MHz,模拟输入频率为270 MHz时,输入信号将混叠到98.64 MHz的第一个奈奎斯特区。输入频率的二次谐波将在171.36 MHz处混叠到第一个奈奎斯特区,而第三个谐波混叠为72.72 MHz。图 5 中的频率折叠工具的绘图对此进行了说明。

图5.由频率折叠工具说明的ADC输出频谱。

图5所示的频率折叠工具图给出了ADC内核输出端的信号在通过AD9680中的DDC之前的状态。信号在AD9680中通过的第一个处理模块是NCO,它将频谱在频域中向左移动98 MHz(回想一下我们的调谐频率为98 MHz)。这会将模拟输入从 98.64 MHz 下移至 0.64 MHz,二次谐波将下移至 73.36 MHz,第三次谐波将下移至 –25.28 MHz(回想一下,我们正在查看复杂的输出)。这显示在下面图6中可视模拟的FFT图中。

图6.NCO = 98 MHz 的 DDC 后的 FFT 复数输出并抽取 2。

从图 6 中的 FFT 图中,我们可以清楚地看到 NCO 如何移动我们在频率折叠工具中观察到的频率。有趣的是,我们在FFT中看到了一种无法解释的基调。然而,这种语气真的无法解释吗?NCO 不是主观的,会改变所有频率。在这种情况下,它将基波输入音98 MHz的别名下移至0.64 MHz,并将二次谐波移至73.36 MHz,将第三次谐波移至–25.28 MHz。此外,另一个音调也发生了变化,出现在86.32 MHz。这语气到底是从哪里来的?DDC或ADC的信号处理是否以某种方式产生了这种音调?好吧,答案是否定的...是的。

让我们更仔细地看一下这个场景。频率折叠工具不包括ADC的直流失调。此直流偏移导致直流(或 0 Hz)时出现音调。频率折叠工具假设理想ADC没有直流偏移。在AD9680的实际输出中,0 Hz时的直流失调音调的频率下移至–98 MHz。 由于复杂的混频和抽取,该直流失调音折回实际频域中的第一个奈奎斯特区。当观察一个复杂的输入信号时,一个音调在负频域中移入第二个奈奎斯特区,它将绕回实频域中的第一个奈奎斯特区。由于我们启用了抽取率等于 2 的抽取,因此我们的抽取奈奎斯特区宽度为 92.16 MHz(回想一下:fs= 368.64 MHz,抽取采样率为 184.32 MHz,奈奎斯特区为 92.16 MHz)。直流偏移音偏移至–98 MHz,与92.16 MHz的抽取奈奎斯特区边界的增量为5.84 MHz。当这个音调折回第一个奈奎斯特区时,它最终在实际频域中与奈奎斯特区边界的偏移量相同,即92.16 MHz – 5.84 MHz = 86.32 MHz。这正是我们在上面的FFT图中看到的基调!因此,从技术上讲,ADC产生信号(因为它是直流偏移),而DDC只是稍微移动它。这就是良好的频率规划的用武之地。适当的频率规划可以帮助避免这种情况。

现在我们已经看了一个使用抽取率等于 2 的 NCO 和 HB1 滤波器的示例,让我们向该示例添加更多内容。现在,我们将提高DDC中的抽取率,以查看当采用更高的抽取率以及NCO的频率调谐时,频率折叠和转换的效果。

在本例中,我们将介绍AD9680-500,其工作输入时钟为491.52 MHz,模拟输入频率为150.1 MHz。AD9680将设置为使用数字下变频器(DDC),具有实输入、复数输出、155 MHz的NCO调谐频率、半带滤波器1(HB1)和半带滤波器2(HB2)(总抽取率等于4)和6 dB增益。由于输出很复杂,因此禁用了复数到实际的转换块。回想一下图 3 中 DDC 的基本示意图,该示意图给出了通过 DDC 的信号流。信号再次首先通过NCO,NCO在频率上移动输入音调,然后通过抽取,通过增益模块,在我们的例子中,绕过复数到实际转换。

我们将再次使用频率折叠工具来帮助了解ADC的混叠效应,以评估模拟输入频率及其谐波在频域中的位置。在本例中,我们有一个真实信号,采样率为491.52 MSPS,抽取率设置为4,输出很复杂。在ADC的输出端,信号如图7所示,使用频率折叠工具显示。

图7.由频率折叠工具说明的ADC输出频谱。

输入采样时钟为491.52 MHz,模拟输入频率为150.1 MHz,输入信号将驻留在第一奈奎斯特区。输入频率的二次谐波在300.2 MHz处混叠到191.32 MHz的第一个奈奎斯特区,而450.3 MHz处的第三个谐波混叠到41.22 MHz处的第一个奈奎斯特区。这是ADC输出端的信号在通过DDC之前的状态。

现在让我们看看信号如何通过DDC内部的数字处理模块。我们将观察信号经过每个阶段的过程,并观察NCO如何移动信号以及抽取过程随后折叠信号。我们将根据输入采样率、491.52 MSPS 和 f 来维护该图。s条款将与此采样率有关。让我们观察一下图 8 中所示的一般过程。NCO 会将输入信号向左移动。一旦复数(负频)域中的信号移位超过–fs/2,它将折回第一个奈奎斯特区。接下来,信号通过第一个抽取滤波器HB2,该滤波器抽取2倍。在图中,我显示了抽取过程,但没有显示滤波器响应,即使操作一起发生。这是为了简单起见。在第一次抽取两倍后,频谱从fs/4 至 fs/2转换为 –f 之间的频率s/4和直流。同样,从 –f 开始的光谱s/2 至 –fs/4转换为直流和f之间的频率s/4.信号现在通过第二个抽取滤波器HB1,该滤波器也抽取2(现在的总抽取等于4)。fs/8 和 fs/4 之间的频谱现在将转换为 –f 之间的频率s/8和直流。类似地,–f 之间的光谱s/4 和 –fs/8将转换为直流和f之间的频率s/8.尽管图中显示了抽取,但未显示抽取滤波操作。

图8.抽取滤波器对ADC输出频谱的影响——通用示例。

回想一下前面讨论的示例,输入采样速率为491.52 MSPS,输入频率为150.1 MHz。NCO 频率为 155 MHz,抽取率等于 4(由于 NCO 分辨率,实际 NCO 频率为 154.94 MHz)。这导致输出采样速率为122.88 MSPS。由于AD9680配置为复杂混频,因此需要在分析中考虑复频域。图9显示频率转换非常繁忙,但通过仔细研究,我们可以处理信号流。

图9.抽取滤波器对ADC输出频谱的影响——实际示例。

NCO 转移后的频谱:

基频从+150.1 MHz向下移动到–4.94 MHz。

基本波的图像从–150.1 MHz偏移到186.48 MHz。

二次谐波从191.32 MHz向下移动到36.38 MHz。

第三次谐波从+41.22 MHz向下移动到–113.72 MHz。

抽取 2 后的频谱:

基频保持在–4.94 MHz。

基波镜像向下转换为–59.28 MHz,并由HB1抽取滤波器衰减。

二次谐波保持在36.38 MHz。

第三次谐波被HB2抽取滤波器显著衰减。

抽取 4 后的频谱:

基波保持在–4.94 MHz。

基本波的图像保持在–59.28 MHz。

二次谐波保持在–36.38 MHz。

第三次谐波被HB1抽取滤波器滤除并几乎消除。

现在让我们看一下AD9680-500的实际测量结果。我们可以看到基波位于–4.94 MHz。基波图像位于–59.28 MHz,振幅为–67.112 dBFS,这意味着图像已衰减约66 dB。二次谐波位于36.38 MHz。 请注意,VisualAnalog 无法正确找到谐波频率,因为它无法解释 NCO 频率和抽取率。

图 10.DDC 后信号的 FFT 复数输出图,NCO = 155 MHz 并抽取 4。

从FFT中,我们可以看到AD9680-500的输出频谱,DDC设置为实际输入和复数输出,NCO频率为155 MHz(实际154.94 MHz),抽取率等于4。我鼓励您浏览信号流图,以了解频谱是如何偏移和转换的。我还鼓励您仔细浏览本文中提供的示例,以了解DDC对ADC输出频谱的影响。我建议打印出图8,方便在分析AD9680、AD9690、AD9691和AD9684的输出频谱时参考。在支持这些产品时,我遇到了许多与ADC输出频谱中频率相关的问题,这些问题被认为是无法解释的。然而,一旦分析完成并通过NCO和抽取滤波器分析信号流,很明显,最初被认为是频谱中无法解释的杂散实际上只是驻留在它们应该在的位置的信号。我希望在阅读和研究本文后,您下次使用集成了DDC的ADC时能够更好地处理问题。 请继续关注第二部分,我们将继续研究DDC操作的其他方面以及如何模拟其行为。我们将研究ADC混叠引起的抽取滤波器响应,提供更多示例,并使用虚拟评估来观察AD9680中DDC的工作及其对ADC输出频谱的影响。

审核编辑:郭婷

-

变频器

+关注

关注

251文章

6570浏览量

145142 -

adc

+关注

关注

98文章

6513浏览量

545035 -

RF

+关注

关注

65文章

3055浏览量

167121

发布评论请先 登录

相关推荐

下变频的设计问题

卫星电视下变频器(高频头)的工作原理

基于FPGA的数字下变频器的设计与实现

如何在数字下变频实现FPGA

基于FPGA的数字下变频器(DDC)的设计

下变频器输入信号幅度对下变频的影响

如何通过下变频器帮助抑制高频干扰

利用带有集成数字下变频器的RF AD解决下变频级问题

利用带有集成数字下变频器的RF AD解决下变频级问题

评论