在恶劣环境中,外部接口需要电气隔离,以确保安全性、功能性或提高抗噪性。这包括用于工业测量和控制的数据采集模块中使用的模拟前端,以及处理节点之间的数字接口。

过去,高达几Mbs的带宽足以满足转换器接口或工业背板的需求,允许使用光耦合器隔离串行外设接口(SPI)或RS-485等协议。数字隔离器提高了此类隔离接口的安全性、性能和可靠性,并提供集成隔离和I/O。然而,工业 4.0 和物联网 (IoT) 等趋势需要更普遍的测量和控制,速度和精度更高,导致对增加带宽的更大需求。

对电流隔离的需求也在激增,因为这些与物理域的数字交互增加,需要保护电机和电力系统、人类操作员和静电放电,以及雷击引起的浪涌等外部因素。精密测量还需要与噪声源隔离,例如更本地化和微型的电源电路以及高速数字处理。

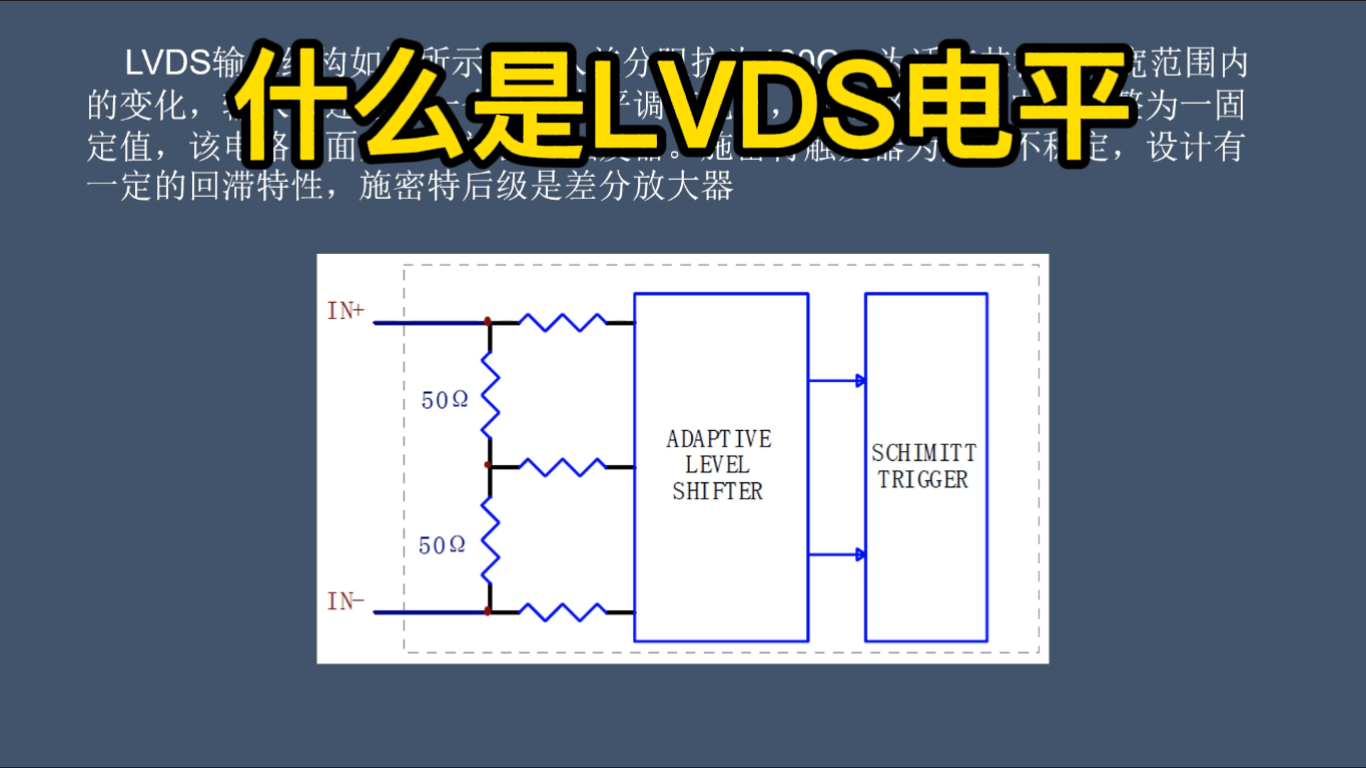

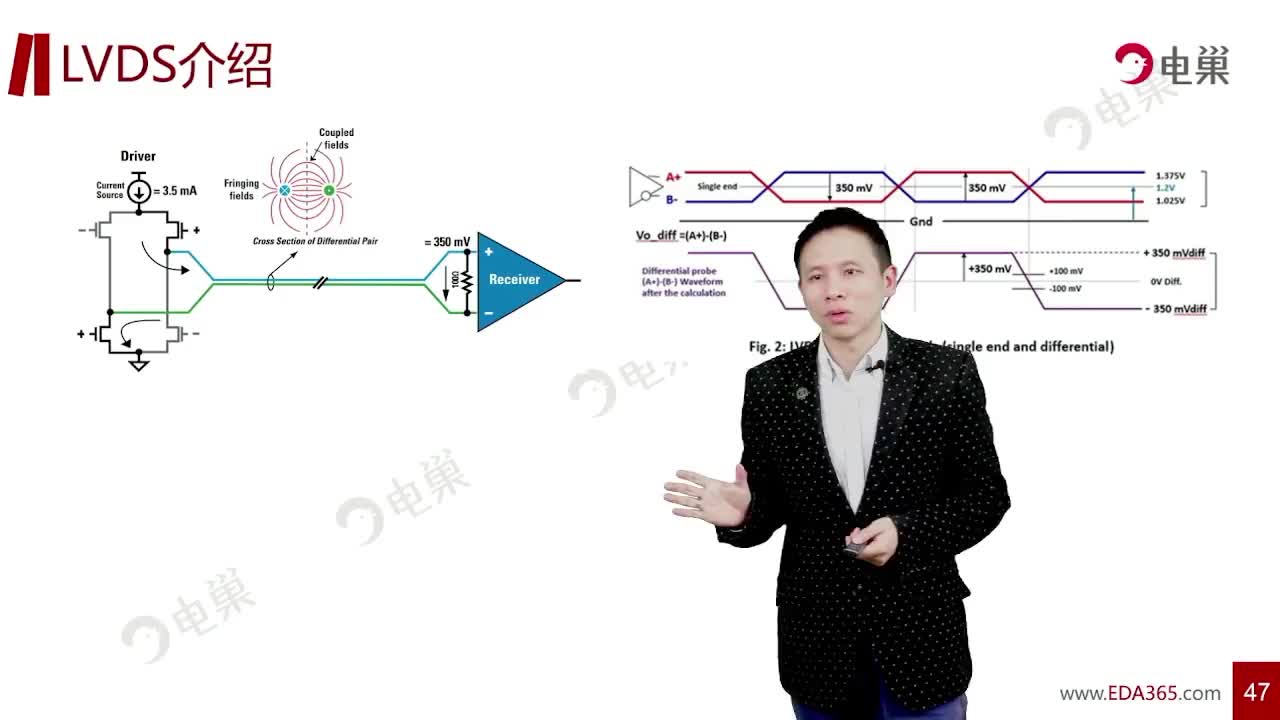

低压差分信号 (LVDS) 是一种无处不在的高速接口,适用于更高性能转换器和高带宽 FPGA 或 ASIC I/O。由于反相和同相信号之间的相互耦合,差分信号对外部电磁干扰(EMI)具有很高的抗扰度,这也相应地最大限度地减少了LVDS信号产生的任何EMI。为LVDS接口添加隔离提供了一个透明的解决方案,可以插入到现有的信号链中,用于高速和精密测量以及控制应用。

今天有哪些选择?

与光耦合器相比,标准数字隔离器仍然是更快、更可靠、更可靠的解决方案,用于转换器和处理器接口的电流隔离。然而,支持高速或精密转换器的典型LVDS数据速率为数百Mbs,而最快的标准数字隔离器支持高达150 Mbps。

为了支持更高带宽的隔离,系统设计人员(到目前为止)已转向定制设计密集型解决方案,例如使用变压器或电容器的解串或分立解决方案。这些增加了成本和设计时间,反序列化甚至可能需要一个额外的简单FPGA来执行该功能。变压器和电容器需要对LVDS信号进行仔细的信号调理,因此应用和数据速率特定的解决方案需要交流平衡编码。另一种解决方案是使用光纤通信链路,但由于成本和复杂性的增加,这更适合多千兆位要求。高速隔离的一系列选项如图1所示,价值主张(取决于设计的难易程度和成本)与实现的最大速度进行了对比。

图1.隔离器实现与隔离器速度的价值主张。

相比之下,如图2所示,ADI公司推出了一系列嵌入式LVDS隔离器:ADN4650/ADN4651/ADN4652,采用i耦合器技术,工作速率高达600 Mbps。除了符合 TIA/EIA-644-A LVDS 标准的 I/O 外,完整的隔离器信号链采用全差分,实现了高抗扰度和低辐射解决方案。提供两个隔离LVDS通道,一个发送和一个接收(ADN4651,反之亦然)或两个发送或接收(ADN4650)。内部高速电路工作电压为2.5 V,在工业系统中可能不作为电源轨存在,因此提供内部低压差稳压器(LDO)(如图3所示),即使在采用3.3 V电源供电时,也能使用单个宽体SOIC解决方案。®

图2.ADN4651 600 Mbps LVDS隔离器框图

图3.ADN4651的眼图和直方图。

这些新型LVDS隔离器是否是一种即插即用型解决方案?

为了保证这些LVDS隔离器可以插入转换器至处理器接口或工作速率高达600 Mbps的处理器内链路,ADN465x系列具有超低抖动的精密时序。这一点很重要,因为在600 Mbps时,单位间隔(UI,例如位时间)仅为1.6 ns,因此边缘的任何抖动仍必须留出足够的时间让接收组件对位进行采样。假设误码率为1×10,ADN465x的典型总抖动为70 ps,或600 Mbps时UI的<5%-12.

如何量化抖动

观察抖动的最基本方法是使用差分探头测量LVDS信号对,并在上升沿和下降沿触发,示波器设置为无限持久性。这意味着从高到低和从低到高的转换是叠加的,允许测量交越点。交越器的宽度对应于迄今为止测量的峰峰值抖动或时间间隔误差(TIE)(比较图3所示的眼图和直方图)。一些抖动是由随机源(如热噪声)引起的,这种随机抖动(RJ)意味着示波器上的峰峰值抖动受运行时间的限制;直方图上的尾部将随着运行时间的增加而增大。

相比之下,确定性抖动 (DJ) 的来源是有界的,例如脉冲偏斜引起的抖动、数据速率相关抖动 (DDJ) 和码间干扰 (ISI)。脉冲偏斜是由于高到低和从低到高的传播延迟之间的差异引起的。这通过偏移交越来可视化,在0 V时,两个边沿被分开(很容易从图3直方图中的分离中看出)。DDJ产生于工作频率上传播延迟的差异,而ISI产生于先前的转换频率对电流转换的影响(边沿时序通常在1秒或0秒后与1010模式不同)。

为了完全估计给定误码率(TJ@BER)的总抖动,可以根据测量中对TIE分布的模型拟合来计算RJ和DJ。其中一个模型是双狄拉克模型,它假设高斯随机分布与对偶狄拉克增量函数(对应于确定性抖动的两个狄拉克增量函数之间的分离)卷积。对于具有显著确定性抖动的 TIE 分布,分布将在视觉上近似于此模型。一个复杂的问题是,一些确定性抖动会导致高斯分量,这意味着双狄拉克可以低估确定性抖动并高估随机抖动。但是,两者相结合仍可准确估计给定误码率的总抖动。

RJ 被指定为来自建模高斯分布的一西格玛均方根值,这意味着要推断更长的运行长度(低 BER),只需选择适当的多西格玛以沿着分布的尾部移动足够远(14 西格玛表示 1×10-12位错误)。然后添加 DJ 以提供TJ@BER估计值。对于信号链中的多个元件,无需添加多个TJ值(这会高估抖动),RJ值可以几何相加,DJ值代数求和,从而对完整的信号链进行更合理的完整TJ@BER估计。

ADN4651的RJ、DJ和TJ@BER均单独指定,根据对多个单元的统计分析,为每个器件提供最大值,以保证这些抖动值在整个电源、温度和工艺范围内。

不同的LVDS接口如何依赖于精确的数据转换?

典型的接收器可以承受10%或20%的抖动,因此使用ADN465x隔离外部LVDS端口允许工业背板通过电缆安全地在PLC和I/O模块之间扩展。最大电缆距离将取决于允许的数据速率、电缆结构和连接器类型,但在较低的数据速率(例如使用高速连接器和适当的屏蔽双绞线电缆时为 200 Mbps)下,可能会有几米的电缆。

模数转换器(ADC)接口通常利用LVDS的源同步数据传输。这意味着LVDS时钟与其他LVDS通道上的一个或多个数据位流并行传输。ADN4650的通道间和器件间偏斜较低,分别为≤300 ps和≤500 ps。这些偏斜值指定了多个通道上从高到低(或从低到高)传播延迟之间的最大差值,这是所有ADN4650器件在电源、温度和工艺方面的统计保证。≤100 ps 的低脉冲偏斜允许在上升和下降时钟沿上计时数据时实现时钟同步,以实现双倍数据速率 (DDR),某些转换器用于增加输出带宽。

为了成功完全隔离使用外部时钟源的模拟前端,可能需要隔离ADC采样时钟,例如,一组多个数据采集通道,所有时钟都在一起。这对任何隔离器都提出了挑战,因为时钟上的任何抖动都会直接增加孔径抖动,从而降低测量质量。与时钟源一样,用于时钟分配的LVDS信号链组件(如扇出缓冲器)通常会将此抖动指定为附加相位抖动。这意味着将输入时钟的相位噪声与输出时钟的相位噪声进行比较,其差值在相关频率范围内进行积分 - 12 kHz至20 MHz是常见的。ADN465x系列本质上是具有集成隔离的LVDS缓冲器,因此在分析对ADC采样的影响时也采用相同的视角。通过使用ADN465x时,通过确保仅376 fs的典型附加相位抖动,即使添加电流隔离也可以保持原始测量质量,特别是因为增加隔离可以消除处理器侧数字电路的噪声。

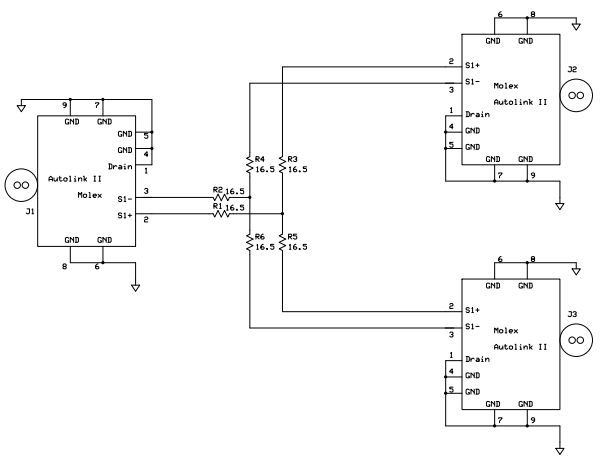

基准电压源电路CN-0388中的18位、5 MSPS、SAR ADC验证了600 Mbps的无差错传输、与300 MHz时钟同步以及隔离采样时钟时的完整ADC性能和分辨率(如图4所示)。现有的ADC评估平台在ADC电路板和高速SDP-H1评估平台之间隔离,使用透明隔离模拟前端的中介层。该软件保持不变,使用精密模拟源根据数据手册规格进行评估时,确认其性能与非隔离平台相同。

图4.用于AD7960和SDP-H1的ADN4651隔离电路。

还有哪些应用可以使用LVDS隔离?

隔离式模拟前端或隔离式工业背板是说明隔离LVDS提供的机会的两个有用的应用示例,但该技术还有许多其他应用。平板显示器的视频信号通常使用LVDS信号,HDMI信号使用类似的差分信号,共模逻辑(CML)。这些通常不需要隔离,但对于某些应用,例如医学成像或工业PC中的外部显示端口,电流隔离可以分别保护人员或设备。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19275浏览量

229740 -

FPGA

+关注

关注

1629文章

21735浏览量

603143 -

转换器

+关注

关注

27文章

8701浏览量

147143

发布评论请先 登录

相关推荐

为何要隔离LVDS?

请问再LVDS差分线是是否要串上100Ω的电阻?

为何要隔离 LVDS?

SN55LVDS31,SN65LVDS31,SN65LVDS

什么是LVDS

LVDS分离器简化高速信号分配

LVDS技术原理和设计简介

浅谈分离LVDS信号设计技术

德索讲解LVDS连接器结构可分离性

德索谈LVDS连接器可分离性的需求

为什么要分离LVDS

为什么要分离LVDS

评论