最近在用LTspice仿真D触发器的一个串并输入功能,只有第一个触发器的波形跟理论分析一致,其他剩余的就是怎么也不行。 经过资料查找,和不停地尝试,最终还是找出了原因。 确实每一个工具还是有其特点的,跟实际的芯片还是有差异。

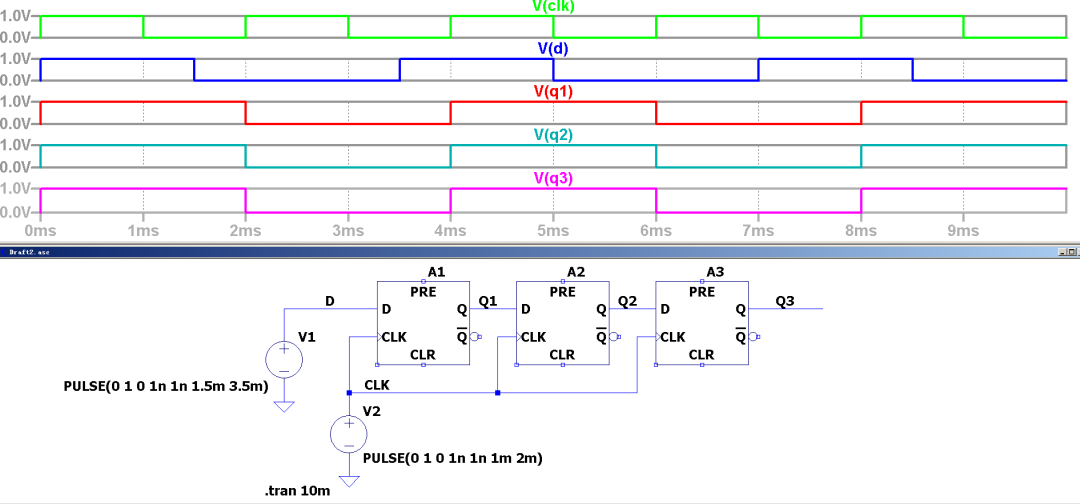

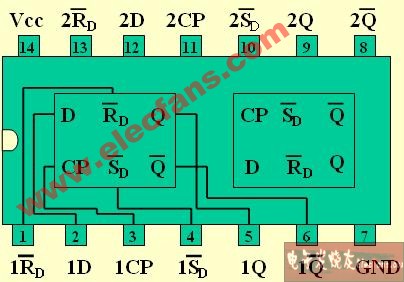

今天就来看看这个问题的前世今生。 首先看一下要仿真的电路图。

在这种类型的寄存器中,输入是一次一位串行,输出也是串行一位。 带D触发器的串行输入串行输出移位寄存器设计,每个触发器一次只能存储一位,因此对于 4 位移位寄存器,需要四个触发器。 如上所示,串行数据通过第一个触发器的 D 应用到所有剩余的触发器。 当一系列数据输入寄存器时,每一位都随着时钟脉冲的每个正沿提供给下一个触发器,并且随着每个时钟脉冲,串行数据从一个触发器移动到下一个触发器。 如果时钟每跳动四次也就是四个周期,那么可以并行取出一次,也就完成了串行转并行的功能。

打开LTspice以后,放置元器件然后进行仿真,但是得出来的结果如下。 两个电源设置上升沿和下降沿都设时间都为1ns,频率和高电平让其不一样。

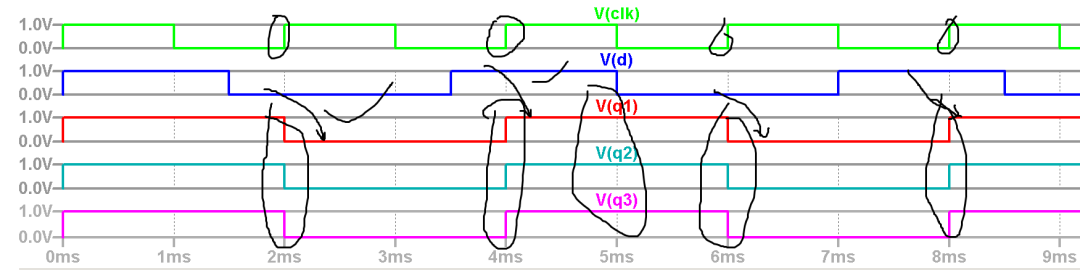

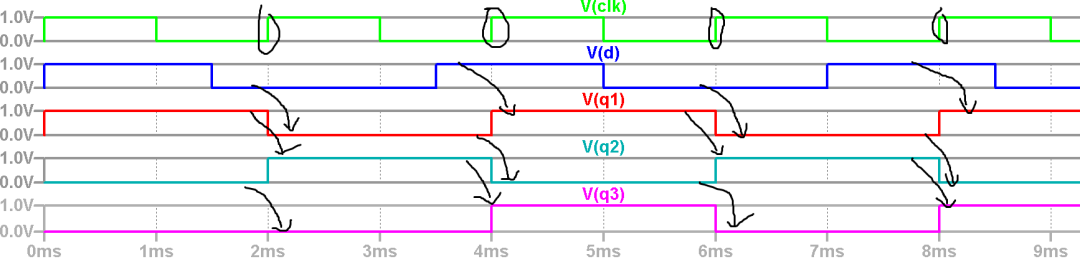

可以看到,输入并没有移位,而是Q2和Q3都是跟Q1一模一样的波形。 这个是不对的,我们可以看到,该跳转的没有跳转。 可以看到只有Q1的输出是正确的。

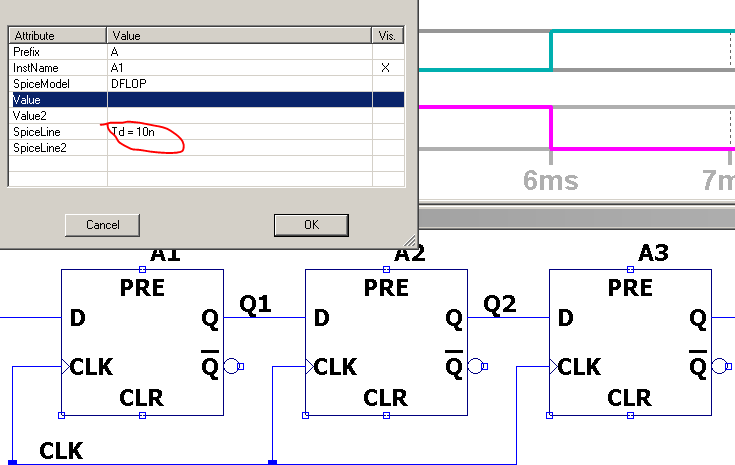

这个问题困扰我也挺久,后来发现是由于这个器件可以说理想器件吧,输出没有延时导致的。 我也尝试过设置这个器件的上升沿和下降沿但是都不行,只有设置了这个器件的延时功能,就可以了。 如果所示,只要打开触发器的属性,然后在SpiceLine里面输入延时10nS。 具体如下图所示。

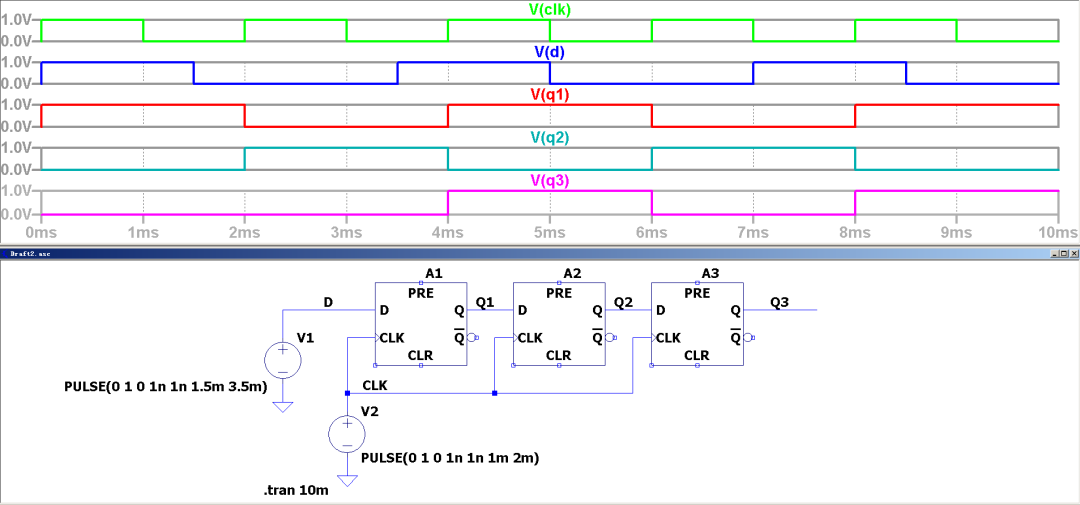

此时再运行这个仿真电路图,就可以得出来正确的结果。 如下图所示。

我们再来分析一下,这次的波形结果。

如图中箭头所标出来的,这次的波形就完全符合理论分析了。 每一次时钟跳转的时候,其D触发器会把其输入转到输出。

-

寄存器

+关注

关注

31文章

5377浏览量

121394 -

仿真

+关注

关注

50文章

4134浏览量

134124 -

D触发器

+关注

关注

3文章

164浏览量

48068 -

触发器

+关注

关注

14文章

2019浏览量

61397 -

LTspice

+关注

关注

1文章

119浏览量

13480

发布评论请先 登录

相关推荐

使用LTspice仿真D触发器的串并输入功能

使用LTspice仿真D触发器的串并输入功能

评论