本应用笔记介绍了如何利用 FPGA 系列的专用 I/O 功能,将具有高速并行低压差分信号 (LVDS) 输入的 LTC2000、16 位、2.5GSPS 数模转换器 (DAC) 连接至 ALTERA STRATIX IV FPGA。

系统硬件包括一个DC2085A LTC2000评估板和一个DK-DEV-4SGX230NSTRAIX IV GX开发板。

来自主机PC的简单软件界面用于配置硬件和加载数据模式。DAC数据模式存储在外部双倍数据速率III型同步动态随机存取存储器(DDR3)中,最大模式深度为256兆采样,便于评估非常复杂的模拟波形。

LTDACgen 是一个图形程序,可生成正弦和扩频模式,以便使用此参考设计评估 LTC2000。LinearLabTools 允许从 Matlab 或 Python 直接控制此参考设计,允许客户使用自己的数据模式进行测试,并将其他仪器纳入评估过程。

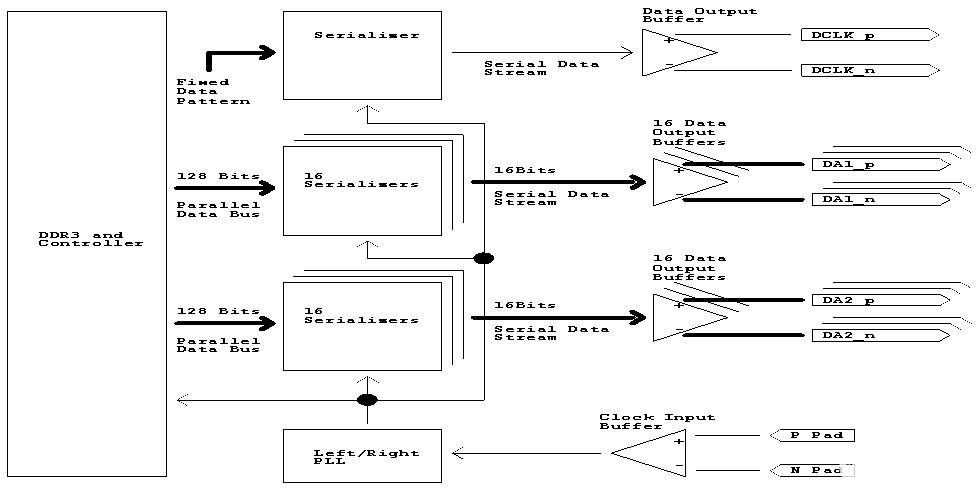

LTC2000 的数字接口由两个 16 位 LVDS 数据流组成,每个数据流支持高达 1250 MSPS 的数据速率和 625 MHz DDR 时钟。

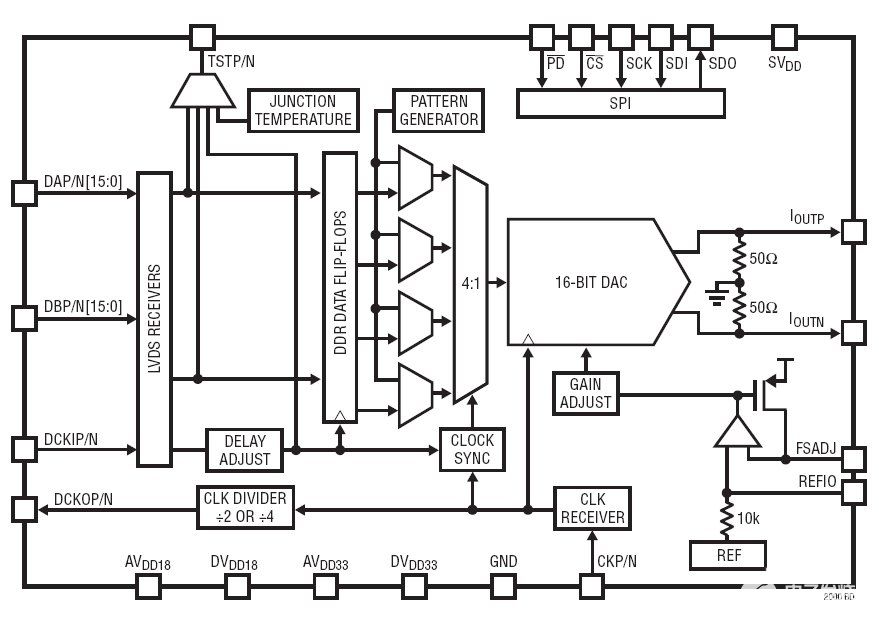

图 1:LTC2000 框图

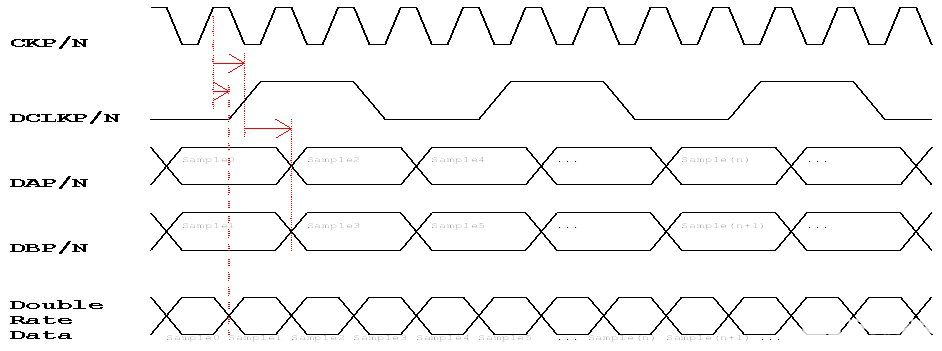

CK是直接控制DAC输出更新的转换时钟。LTC2000 包含一个可编程时钟分频器和 LVDS 发送器,后者提供了一个分频版本 (f)CK/2或 fCK/4) 的 CK在主机 FPGA 或 ASIC 使用的 DCKO 引脚上。DCKI是DDR数据时钟输入。由DCKI计时的两个16位数据总线由CK时钟的多路复用器组合成单个16位双倍速率数据流,然后将其转换为模拟信号。有关更多详细信息,请参阅 LTC2000 的产品手册。

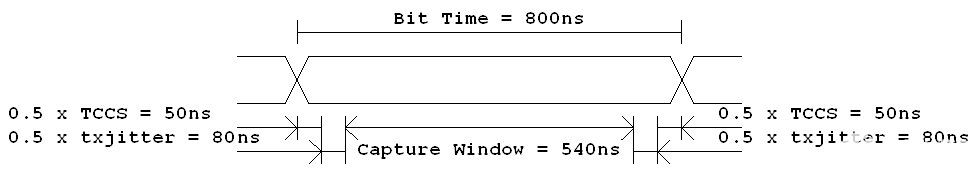

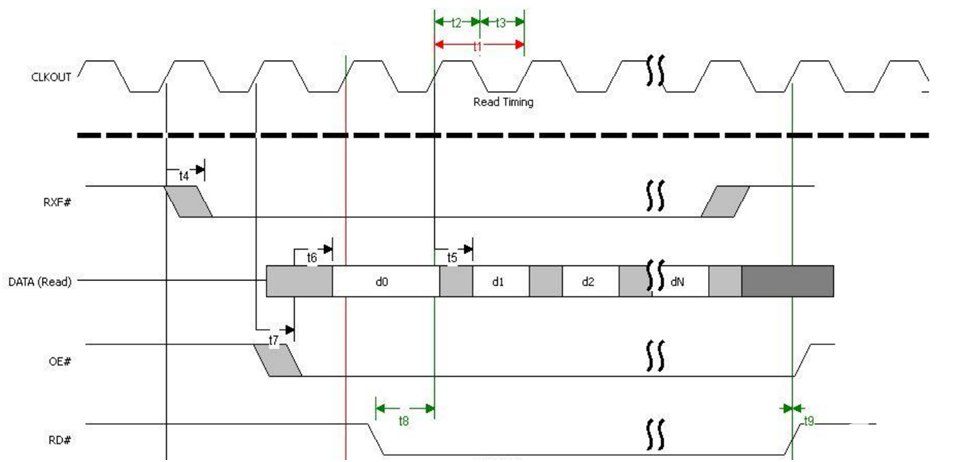

图 2:LTC2000 接口时序图

表1总结了时钟发生器和FPGA的要求。

| 信号名称 | 速度要求(最大) | 源 |

| CK | 2.5千兆赫 | 外部超低抖动/噪声时钟发生器 |

| 德利克 | 625兆赫 | FPGA |

| 大 | 1250兆秒 | FPGA |

| .DB | 1250兆秒 | FPGA |

| 双倍速率数据流 | 2.5GSPS | 内部 LTC2000 |

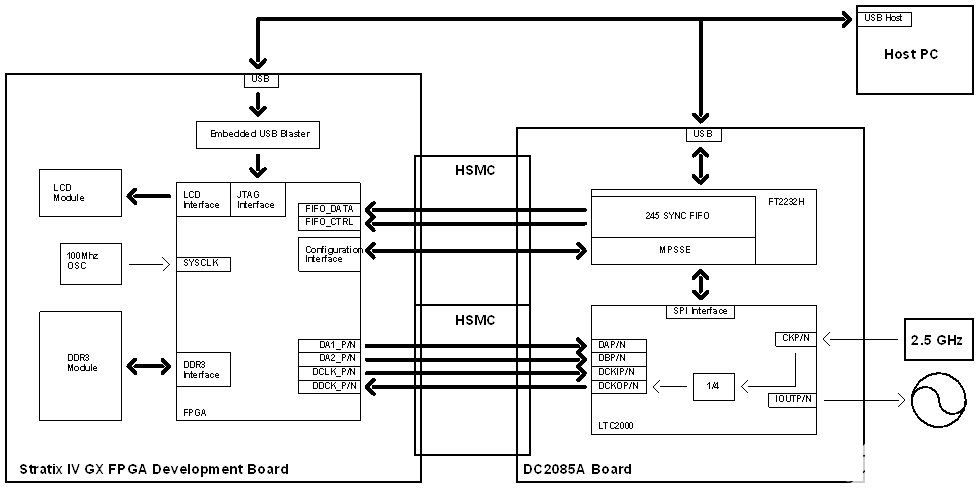

演示系统架构

STRATIX IV GX FPGA 开发板为低功耗、高性能和逻辑密集型设计的开发和原型设计提供了一个硬件平台。该板包含一个STRATIX IV GX FPGA EP4SGX230KF40(BGA 1517引脚),具有64位数据总线的512MBDDR3 SDRAM和具有16位数据总线的128MBDDR3 SDRAM。它还提供了广泛的外围设备和接口,以促进开发。由于FPGA设计对于此应用非常简单,因此器件和电路板使用率非常低。

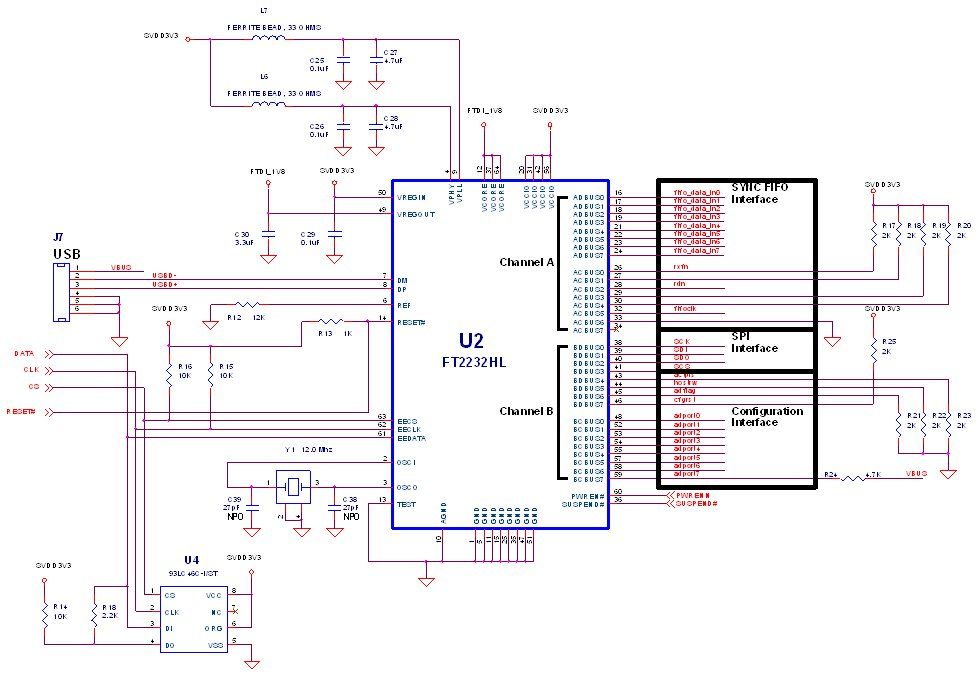

DC2085A 板包含 LTC2000、允许使用单 5V 电源的电源管理电路,以及一个提供用于数据传输和控制的 USB 接口的 FT2232H。FT2232是一款USB 2.0高速(480Mbps)控制器,可配置为双多协议同步串行引擎(MPSSE)模式或单高速同步FIFO模式。在 MPSSE 模式下,FT2232 的通道 B 实施了一个用于配置 LTC2000 的 SPI 接口。

LTC2000 需要施加到 CK 输入的低抖动 2.5GHz (MAX) 时钟。DC2085A 板通过两个高速夹层卡 (HSMC) 连接器与 FPGA 板配接。这些连接器承载来自 LTC2000 的 DCKO、两个 16 位数据流 (DA、DB) 和由 FPGA 生成的 DCKI 数据捕获时钟。DCKO 用作主 FPGA 时钟,内部分频器设置为双端口模式的 4 分频。所有高速信号都是LVDS,使用HSMC连接器的TX侧。多个HSMC RX信号配置为CMOS GPIO,连接到8位FT2232同步FIFO端口,主机通过该端口上传DAC码型数据。

FPGA 设计还控制 FPGA 板附带的 LCD 模块。它显示缓冲区大小配置、FPGA 状态和当前操作模式。LCD电路位于专用时钟域SYSCLK上,该时钟域来自100MHz板载振荡器。

FPGA位文件通过嵌入式“USB冲击波”JTAG适配器上传。位文件也可以加载到配置 EEPROM 中,该 EEPROM 在上电时加载 FPGA。

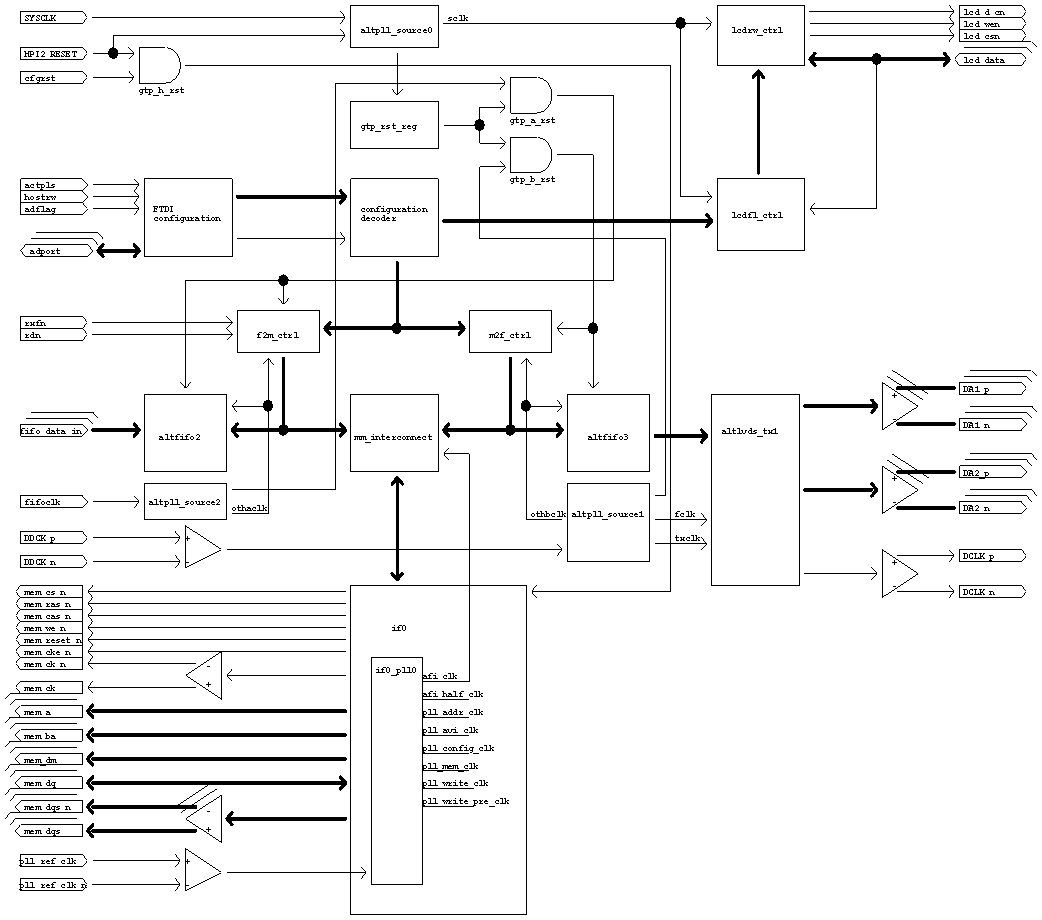

图 3:演示系统架构

STRATIX IV FPGA 的 I/O 架构

STRATIX 4 GX器件具有内置串行器/解串器(SERDES)电路,支持数据速率高达1.6Gbps的高速LVDS接口。引脚分配对于 STRATIX IV FPGA LVDS 应用非常重要,因为只有部分 I/O 模块支持完整的 LVDS 功能,只有部分 PLL 支持这些 I/O。STRATIX IV 器件系列支持行和列 I/O 组上的 LVDS。

柱输出缓冲器(位于顶部和底部)是单端的,需要外部端接方案来支持LVDS。

行输出缓冲器(位于左侧和右侧)是真正的LVD,只有位于左侧和右侧的PLL支持这些IO。

专用的SERDES电路在行I/O组上实现,以进一步增强器件中的LVDS接口性能。对于列 I/O 组,SERDES 在核心逻辑中实现,因为列 I/O 组上没有专用的 SERDES 电路。只有真正的LVDS缓冲器和SERDES才能用于此应用。SERDES电路中包含以下专用组件:

差分 I/O 缓冲器

发射器串行器

接收器解串器

数据重新对齐

DPA(动态相位对准)

同步器(先进先出缓冲器)

锁相环 (PLL)(位于器件的左侧和右侧)

真正的差分 I/O 缓冲区的方向不可配置。特定引脚仅支持单向数据流。

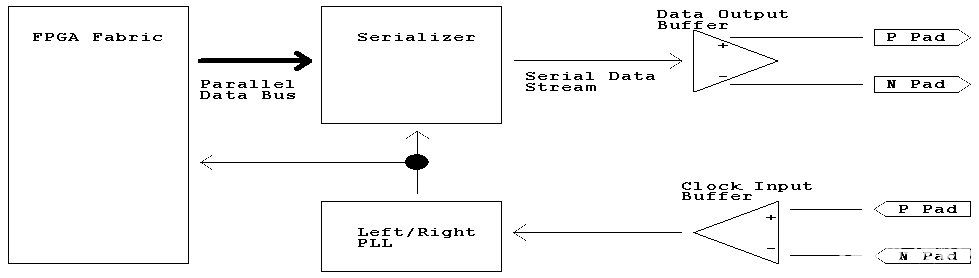

图 4:STRATIX IV 差分变送器

此应用仅使用差分变送器。其专用电路由差分缓冲器和串行器组成。时钟源来自左右PLL。差分输出缓冲器可以驱动LVDS、微型LVDS和RSDS信号电平。串行器从FPGA结构中获取多达10位宽的并行数据,将其时钟输入负载寄存器,并在将数据发送到差分缓冲器之前,使用左右PLL时钟的移位寄存器对其进行序列化。首先传输并行数据的MSB。

Quartus 软件可以设置 ×3、×4、×6、×7、×8 或×10 的序列化因子以及 SDR 和 DDR 模式。

包含 DAC 数据的 DDR3 存储器驱动慢速、易于约束的 256 位宽数据总线。FIFO处理存储器和LVDS发送器之间的时钟域交叉。发射器模块将并行数据总线串行化为32个超高速数据流,如图5所示。由于所有串行器都由一个PLL计时,因此会产生一个非常高速的32位并行数据总线。具有恒定并行输入的附加串行器可生成可调DAC数据输入时钟DCKI,并与数据流完美对齐。

图 5:LTC2000 FPGA 设计中的差分发射器

如表1和图5所示,如果输出数据流为1.25Gbps,则来自存储器的并行总线只需要1.25G/8 = 156.25MHz时钟。如果使用 64 位宽、533MHz 双倍数据速率 DDR3 模块作为 DAC 数据存储,则输出总线 256 位 Avalon-MM 总线的工作时钟可能会将速度降至 266.5MHhz。一个简单的FIFO电路可以将Avalon-MM总线转换为连接到差分发射器输入端口的相同宽度的156.25MHz并行总线。现在,超高速部件仅由FPGA专用SERDES模块处理。唯一关键的时序问题是32位输出数据流时序偏差。虽然I/O模块中没有用于真正的LVDS输出缓冲器偏斜调整的可编程延迟元件,但STRATIX声称通道间偏斜(TCCS)小于100ps:由同一PLL驱动的通道上最快和最慢输出边沿之间的时序差,包括时钟变化和时钟偏斜。数据速率从600Mbps到1.6Gbps的总抖动(txjitter)小于160ps。因此,如果我们完美地处理PCB走线匹配,1.25Gbps的数据采集窗口应如图6所示。有关更多详细信息,请参阅 http://www.altera.com/literature/hb/stratix-iv/stx4_siv54001.pdf。

图 6:数据流捕获窗口

STRATIX IV GX FPGA 开发板提供两个 DDR3 模块,512 MB DDR3 SDRAM,底部端口(Bank 3)上带有 64 位数据总线,128 MB DDR3 SDRAM 具有位于顶部端口的 16 位数据总线(Bank 8)。如果在顶部端口上使用 DDR3,则 64 位 Avalon-MM 总线没有足够的带宽来扩展到 256 位/156.26MHz 本地并行总线。因此,512 MB DDR3 模块是唯一的选择。

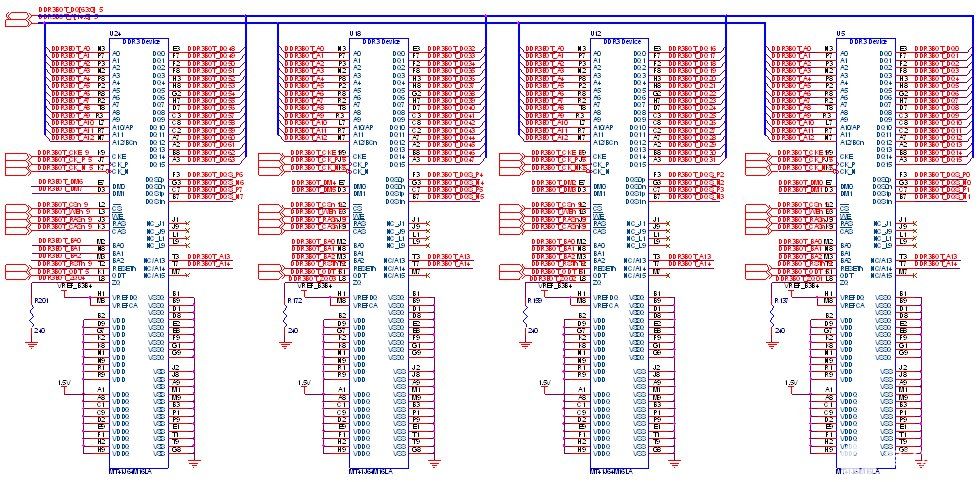

图 7:512MB DDR3 底部端口组织

DDR3 底部端口由四个 DDR3 设备美光 MT41J64M16LA-15E 组成,提供具有 64 位数据总线的单个 512 MB 接口。有关特定美光 DDR3 SDRAM 的详细信息,请参阅 http://www.micron.com/products/dram/ddr3-sdram#fullPart&236=0。

该内存接口设计为在 300MHz(DDR3 的最低频率)和 533MHz 之间运行,最大理论带宽超过 68.2GBps。FPGA 中的内部总线在全速率或半速率时通常分别为宽度的 2 倍或 4 倍。对于此应用,533MHz 64 位接口将变为 266.5MHz 256 位总线。

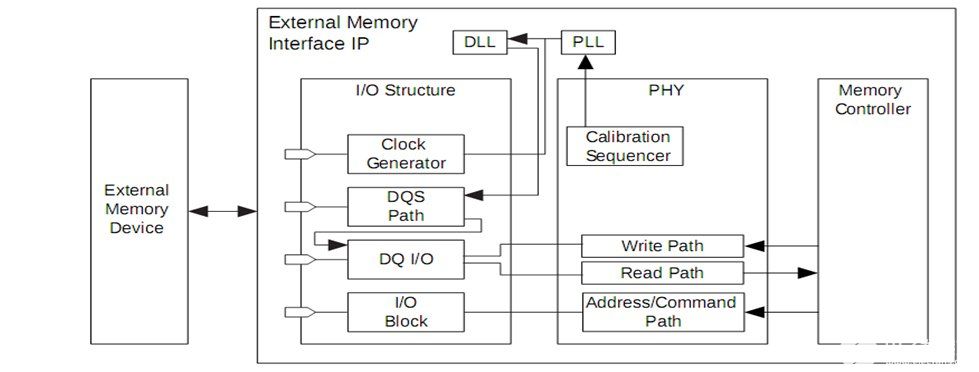

ALTERA FPGA 通过特定的 DDR3 接口 IP 实现最佳的 DDR3 接口性能。该 IP 提供以下组件:

物理层接口 (UniPHY),用于构建数据路径并管理FPGA和外部DDR3设备之间的定时传输。

DDR3 控制器 (HPCII),实现所有 DDR3 命令和协议级要求。

图 8:ALTERA DDR3 控制器和 UniPHY IP 框图

FT2232H 双通道 USB 控制器

DC2085A 板包含一个 FTDI 双通道 USB 控制器 FT2232,用于从主机上传 DAC 数据并配置 LTC2000。FT2232设置为同步FIFO模式以上传数据。传输速率高达25MB/秒,通过带有少量握手信号的8位宽总线。只有通道A可以配置为FT245式同步FIFO接口。设置此模式时,使用的引脚和信号说明如表2所示。在此模式下,通道 B 不可用,因为所有资源都已切换到通道 A。数据在 CLKOUT 的上升沿读取。

表 2:FT2232 同步 FIFO 接口说明

| 信号名称 | 方向 | 同步先进先出接口说明 |

| ADBUS[7:0] | 双向 | D7 到 D0 双向 FIFO 数据。此总线在此应用程序中配置为输出 |

| RXF# | 输出 | 如果为高,则不要从 FIFO 读取数据。当较低时,FIFO 中有可用的数据,可以通过将 RD# 驱动为低电平来读取这些数据。在同步模式下,当 RXF# 和 RD# 都处于低电平时,每个时钟上传输数据 |

| 研发# | 输入 | 允许将当前 FIFO 数据字节驱动到 D0...当 RD# 变为低电平时为 D7。在每个 CLKOUT 周期从接收 FIFO 缓冲区获取下一个 FIFO 数据字节(如果可用),直到 RD# 变为高电平。 |

| 克利库特 | 输出 | 由芯片驱动的60MHz时钟。所有信号都应同步到此时钟。 |

图 9:FT2232H 同步 FIFO 接口时序图

表 3:FT2232 同步 FIFO 接口信号时序

| 名字 | 最低 | 典型 | 最大 | 单位 | 描述 |

| T1 | 16.67 | 纳 | CLKOUT时期 | ||

| T2 | 7.5 | 8.33 | 纳 | CLKOUT高期 | |

| T3 | 7.5 | 8.33 | 纳 | CLKOUT低谷期 | |

| T4 | 1 | 7.15 | 纳 | CLKOUT 到 RXF# | |

| T5 | 1 | 7.15 | 纳 | 用于读取有效数据的 CLKOUT | |

| T6 | 1 | 7.15 | 纳 | OE# 读取数据有效 | |

| T7 | 1 | 7.15 | 纳 | CLKOUT 到 OE# | |

| T8 | 11 | 纳 | 到 CLKOUT 的 RD# 设置时间(RD# 低后 OE# 低) | ||

| T9 | 0 | 纳 | RD# 保持时间 |

为了配置 LTC2000 和 FPGA,FT2232 的通道 B 必须设置为多协议同步串行引擎 (MPSSE) 模式。MPSSE可以独立配置为许多行业标准串行接口协议,如JTAG,I2C 或 SPI,或者可用于实现专有总线协议。对于此应用程序,它被设置为SPI和GPIO接口和端口。

FPGA 设计

图 10:FPGA 设计框图

下表列出了顶级端口说明。

表 4:DDR3 接口

| 信号名称 | 方向 | 描述 |

| pll_ref_clk | 差分输入 | DDR3 控制器和 UniFHY 参考时钟输入 |

| mem_a | 输出 | 行地址 |

| mem_ba | 输出 | 银行地址 |

| mem_ck | 差分输出 | 提供给外部 DDR3 的时钟 |

| mem_cke | 输出 | 时钟使能 |

| mem_cs_n | 输出 | 芯片选择 |

| mem_ras_n | 输出 | 行地址可用 |

| mem_cas_n | 输出 | 列地址可用 |

| mem_we_n | 输出 | 写启用 |

| mem_dm | 输出 | DDR3 输入数据掩码 |

| mem_reset_n | 输出 | 重置 DDR3 |

| mem_dq | 双向 | 数据总线 |

| mem_dqs | 差分双向 | 数据选通 |

| mem_odt | 输出 | 启用 DDR3 片上端接 |

| mem_rdp | 输入 | FPGA 片上端接输入 |

| mem_rdn | 输入 | FPGA 片上端接输入 |

表 5:系统控制界面

| 信号名称 | 方向 | 描述 |

| 系统CLK | 差分输入 | 系统时钟输入 |

| MPI2_RESET | 输入 | 按钮复位输入 |

| 达普德 | 输出 | DAC 关断控制 |

表 6:配置界面

| 信号名称 | 方向 | 描述 |

| lcd_d_cn | 输出 | 液晶屏数据或命令选择 |

| lcd_wen | 输出 | 液晶屏写启用 |

| lcd_csn | 输出 | 液晶芯片选择 |

| lcd_data | 双向 | 液晶数据总线 |

表 7:配置界面

| 信号名称 | 方向 | 描述 |

| 菲福克 | 输入 | FT2232 先进先出时钟输入。它将通过HSMC连接到表8中的CLKOUT |

| RXFN | 输入 | 提供先进先出数据。它将通过 HSMC 连接到表 8 中的 RXF# |

| RDN | 输出 | 读取启用。它将通过 HSMC 连接到表 8 中的 RD# |

| fifo_data_in | 输入 | DAC转换数据输入端口。它将通过 HSMC 连接到表 8 中的 ADBUS[7:0] |

| 行动 | 输入 | FT2232通道B GPIO产生的脉冲。以下所有信号将被上升沿锁存 |

| 霍斯特鲁 | 输入 | FT2232通道B GPIO生成的读/写选择 |

| 广告标志 | 输入 | FT2232通道B GPIO生成的地址/数据选择 |

| CFGRST | 输入 | FT2232 通道 B GPIO 生成的配置复位输入 |

| 广告端口 | 双向 | 由FT2232通道B GPIO实现的8位配置数据/地址端口 |

表 8:LTC2000 接口

| 信号名称 | 方向 | 描述 |

| DDCK | 差分输入 | LTC2000 参考时钟输入 |

| 德利克 | 差分输出 | 数据采集时钟 |

| 伊普 | 差分输入 | 16 位数据流 |

| 大通 | 差分输入 | 16 位数据流 |

下表列出了设计中的主要时钟域。

表 9:FPGA 时钟树

| 时钟源 | 频率 | 锁 相 环 | 生成的时钟 | 装载 | 生成时钟的频率 |

| DDCK | 625兆赫 | altpll_source1 | 福克尔克 | altlvds_tx1 | 1.25千兆赫 |

| TXCLK | altlvds_tx1 | 625兆赫 | |||

| 其他 | m2f_ctrl, altfifo3 | 625兆赫 | |||

| 系统CLK | 100兆赫 | altpll_source0 | 渣滓 | lcdrw_ctrl, lcdfl_ctrl | 500kKHz |

| 菲福克 | 60兆赫 | altpll_source2 | 奥塔克尔克 | f2m_ctrl, altfifo2 | 60兆赫 |

| pll_ref_clk | 100兆赫 | altpll_source1If0_pll0 |

afi_clk、 afi_half、 pll_addr_clk、 pll_avi_clk、 pll_config_clk、 pll_mem_clk、 pll_write_clk pll_write_pre_clk |

Mm_intererconnect,if0 | 266.5兆赫 |

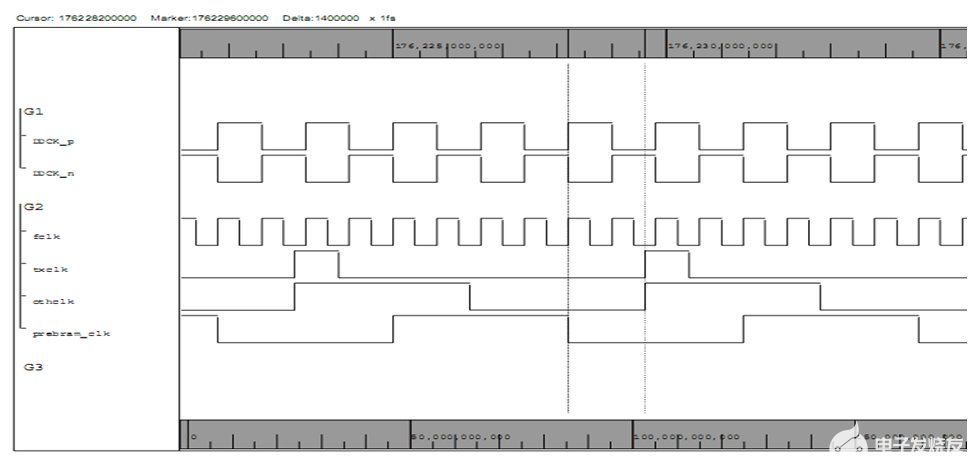

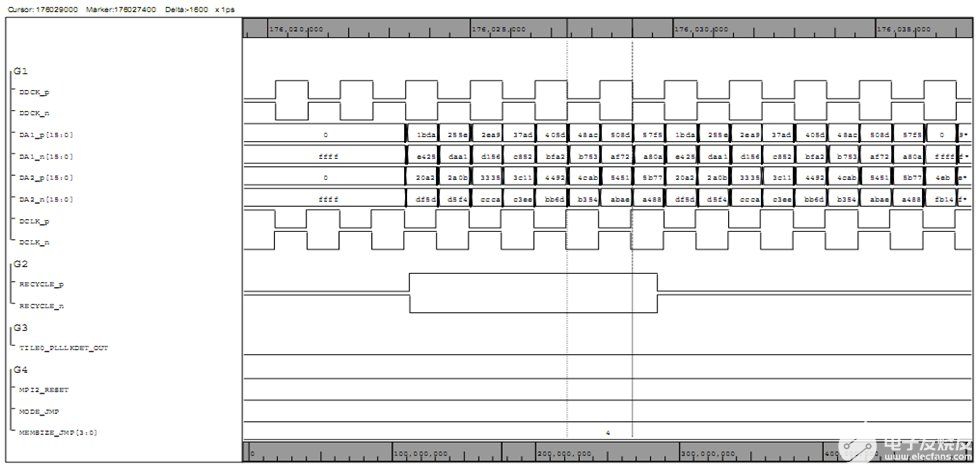

PLL的时钟altpll_source1时序关系如下图所示:

图 11:PLL altpll_source1 时序图

DCKO从LTC2000 DAC更新时钟除以4,频率高达625MHz的频率被馈入PLL(altpll_source1)作为发送器的参考时钟。fclk 和 txclk 被传送到差分发送器 (altlvds_tx1),以生成数据流 DA1、DA2 和 DAC 数据输入时钟 DCLK。txclk 占空比和 txclk、其他相位需要根据 FPGA 后放置和布线时序报告进行调整,以满足时序要求。当前设置为:13%、101.25 度、101.25 度。不同的FPGA器件、实现甚至不同的电路板制造都可能需要重新调整。

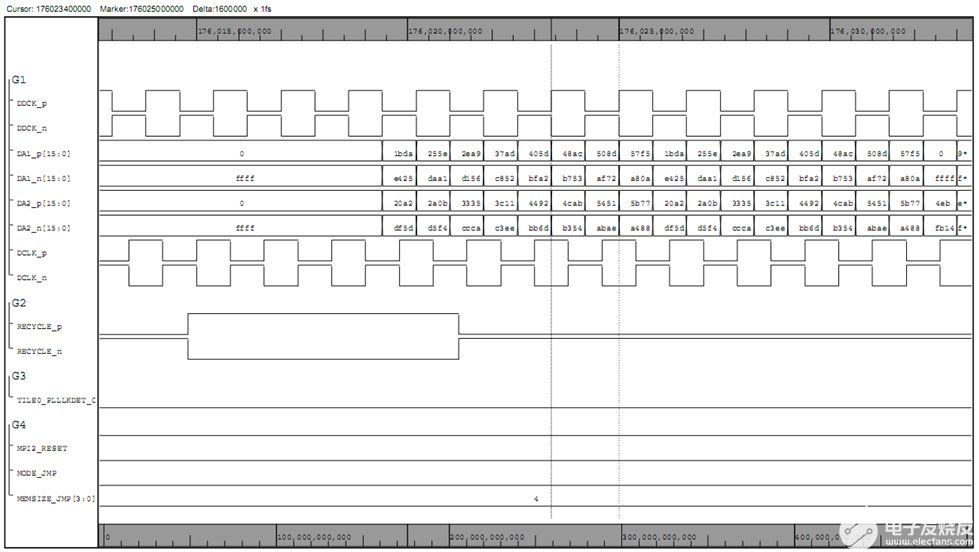

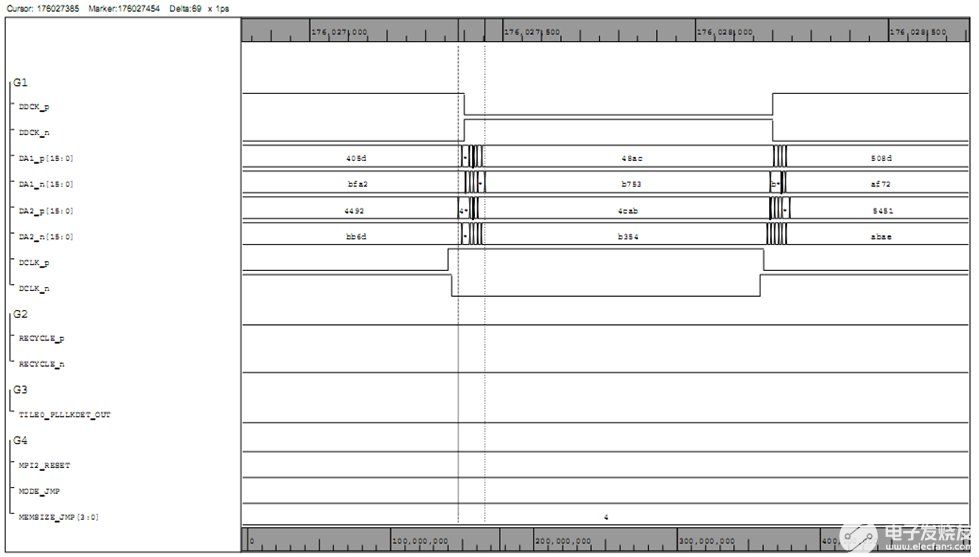

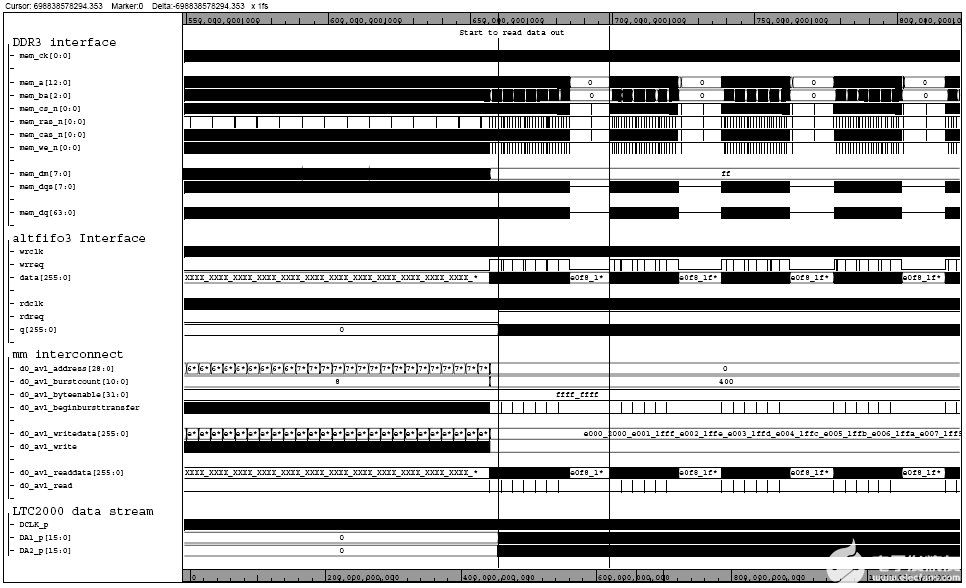

图 12:2.5Gsps 时的功能仿真

图 13:2.5Gsps 时的放置和布线仿真

图 14:2.5Gsps 数据线偏斜时的放置后和布线仿真

DAC数据存储在STRATIX FPGA板上的外部512MBTE DDR3 SDRAM模块中。DDR3内存控制器设计基于ALTERA IP,DDR3 SDRAM控制器和UniPHY v13.1。该IP由高性能控制器II(HPCII)和UniPHY组成,UniPHY是外部存储器接口的物理层。HPC II 提供高内存带宽、高时钟速率性能和运行时可编程性。控制器可以通过将读取和写入分组在一起来对数据进行重新排序,以减少行冲突和总线周转时间,从而实现高效的流量模式并减少延迟。该 IP 由 ALTERA 工具“超级向导管理器”生成。必须从 IP 中删除 ALTERA Avalon-MM 流量处理器。有关带 UniPHY 的 DDR3 SDRAM 控制器和 IP 生成流程的更多详细信息,请参阅 http://www.altera.com/literature/lit-external-内存接口.jsp。

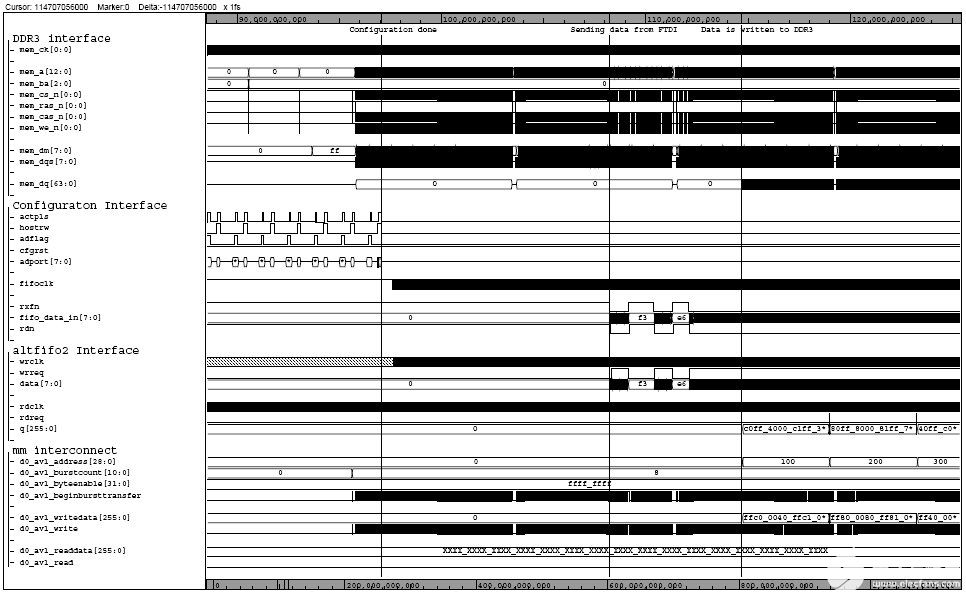

构建了一个特殊的接口,用于通过HSMC连接FT2232,以从主机PC上传DAC数据。在数据传输之前,FT2232必须设置为同步FIFO模式。DC2085A板中FPGA和FT2232之间的引脚连接关系如图15所示。

图 15:DC 2085A 板的 FT2232 部分

写入过程由 rxfn 触发,并由 FT2232 驱动。当低时,表示DAC数据在FT2232的FIFO中可用。FPGA通过驱动低电平RDN来响应它,以通过8位端口fifo_data_in捕获从FT2232的内部FIFO到altfifo2(FPGA的8位x 512 FIFO)的数据。此 FIFO 将数据总线扩展至 256 位宽,并写入 DDR3 控制器模块mm_interconnect。mm_interconnect发出命令以初始化外部 DDR3 SDRAM,将数据转换为 128 位格式,并通过 UniPYH if0 将数据发送到外部 DDR3 内存。如图16所示,写入流程完全由电路f2m_ctrol控制。当所有数据存储在存储器中时,f2m_ctrl向电路m2f_ctrl提交命令以启用读取流。数据从DDR3读取到FHY以及mm_interconnect。构建了一个电路,用于将 Avalon 总线连接到 256 位 x 4096 FIFO altfifo3。FIFO altfifo3将数据从266.5MHz突发传输总线缓冲到156.26MHz不间断传输总线,如图17所示。FIFO输出端口直接驱动差分变送器altlvds_tx1。差分发送器产生两个具有 1.6Gsps 带宽、16 位 LVDS SERDES 电路的数据流,并通过 HSMC 连接器传输到 LTC2000,如图 10 所示。读取流程完全由电路m2f_ctrol控制。DDR3 控制器的效率会影响 266.5MHz 总线操作。较低的效率会破坏156.26MHz不间断总线,需要使用更大的FIFO。影响效率的两个主要因素是内存供应商指定的接口标准以及传输数据的方式。

图 16:altfifo2 捕获的数据写入 DDR3

图 17:图 17:从 DDR3 读取的数据通过 altfifo3 和 LVDS SERDES 传输到 LTC2000

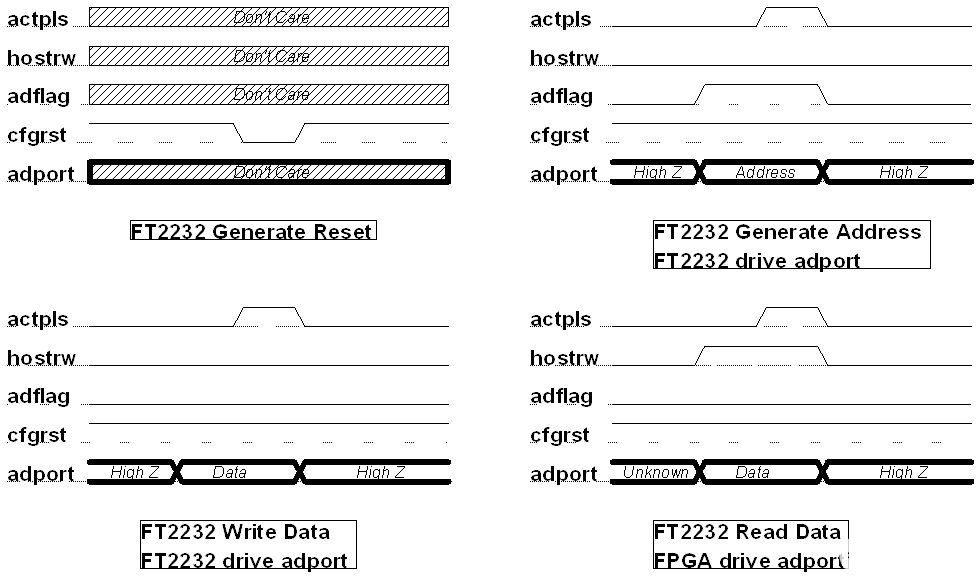

f2m_ctrl和m2f_ctrl由 FTDI 配置配置,FTDI 通道 B 访问该配置如图 15 所示。12 位 GPIO 按照以下协议构建寄存器映射访问总线:

图 18:FT2232 配置端口协议

下表列出了整个 FPGA 寄存器映射:

表 10:FPGA ID 寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 身份证 | |||||||

| 读/写 | 读/写 | |||||||

| 初始值 | 0x1a | |||||||

表 11:FPGA 控制寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 记忆大小 | 呼吸道合胞病毒 | 模式 | |||||

| 读/写 | 读/写 | |||||||

| 初始值 | 0x00 | |||||||

RSV:储备

模式:1:一帧,只发送缓冲区数据直到缓冲区结束 0:环回,从缓冲区的开始到结束连续发送缓冲区数据,直到时钟停止

内存大小:缓冲区大小选择

表 12:缓冲区大小配置

| 记忆大小 | 缓冲区大小 |

| 0 | 16K 样本 |

| 1 | 32K 样本 |

| 2 | 64K 样本 |

| 3 | 128K 样本 |

| 4 | 256K 样本 |

| 5 | 512K 样本 |

| 6 | 1M 样品 |

| 7 | 2M 样品 |

| 8 | 4M 样品 |

| 9 | 8M 样品 |

| 10 | 16M 样品 |

| 11 | 32M 样品 |

| 12 | 64M 样品 |

| 13 | 128M 样品 |

| 14 | 256M 样品 |

未知值将被识别为 16K 设置

表 13:FPGA 状态寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 呼吸道合胞病毒 | 弗拉夫 | 弗雷德富尔 | 德甲司 | 锁相环2 | 锁相板1 | 锁相点0 | 德普尔 |

| 读/写 | 读 | |||||||

| 初始值 | 0x00 | |||||||

FWRFUL:向外部 DDR3 写入数据的 FIFO 已满。

FRDFUL:从外部DDR3读取数据的FIFO已满。

DDRPLL:DDR 控制器的嵌入式 PLL 已锁定。

DDRRDY:外部 DDR 已准备好访问。

PLL0:接受系统CLK的PLL被锁定。

PLL1:接受 DDCK 的 PLL 已锁定。

PLL2:接受 fifoclk 的 PLL 被锁定。

表 14:DAC 关断寄存器

| 位 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 位名 | 呼吸道合胞病毒 | DACPD | ||||||

| 读/写 | 写 | |||||||

| 初始值 | 0x00 | |||||||

RSV:储备

DACPD:1:打开 DAC

0:关闭 DAC

FPGA 设计实现了用于 FPGA 配置和状态显示的全功能 LCD 驱动器。它支持连接到STRATIX IV GX FPGA开发板的Lumex LCD模块SML-LX1206GC-TR。

LCD驱动器电路lcdrw_ctrl,lcdfl_ctrl由FPGA板载100MHz振荡器的专用时钟域SYSCLK计时。下图是两行32个字符的液晶显示屏:

图 19:液晶显示屏

| F | P | G | 一个 | : | X | X | X | M | O | D | E | : | Y | Y | |

| B | U | F | S | 我 | Z | E | : | Z | Z | Z | Z | S | P | s |

表15:液晶屏显示信息

| 字符 | 显示 | 描述 |

| 三十 | ||

| FST | 配置重置 | |

| 英国夏令时 | 按钮复位 | |

| IF0 | DDR3 控制器未就绪 | |

| .CFG | 配置期间 | |

| 时钟 | 无 LTC2000 时钟输入 | |

| 跑 | 正常运行期间 | |

| YY | ||

| 中频 | 环回模式 | |

| 顺丰 | 单帧模式 | |

| 兹兹 | (样本计数) | 请参阅表3 缓冲区大小 |

参考设计

表 16:参考设计矩阵

| 参数 | 描述 |

| 常规 | |

| 开发者名称 | 俞斌 |

| 目标设备 | 斯特拉蒂克斯 IV GX FPGA EP4SGX230KF40 |

| 提供的源代码 | 是的 |

| 源代码格式 | 是的 |

| 设计使用现有参考中的代码或 IP 设计、应用说明、第三方或 超级向导™软件 | 是的 |

| 模拟 | |

| 执行功能模拟 | 是的 |

| 执行时序仿真 | 是的 |

| 为功能和时序仿真提供测试平台 | 是的 |

| 测试平台格式 | 威瑞洛格 |

| 模拟器软件和版本 | NCVerilog (64位) 08.20-s014 |

| 香料/宜必思模拟 | 不 |

| 实现 | |

| 合成软件工具和版本 | 四重奏 II v13.1.0 |

| 实施软件工具和版本 | 四重奏 II v13.1.0 |

| 执行静态时序分析 | 是的 |

| 硬件验证 | |

| 硬件验证 | 是的 |

| 用于验证的硬件平台 | 凌力尔特DC2085A板和STRATIX IV GX FPGA开发板 |

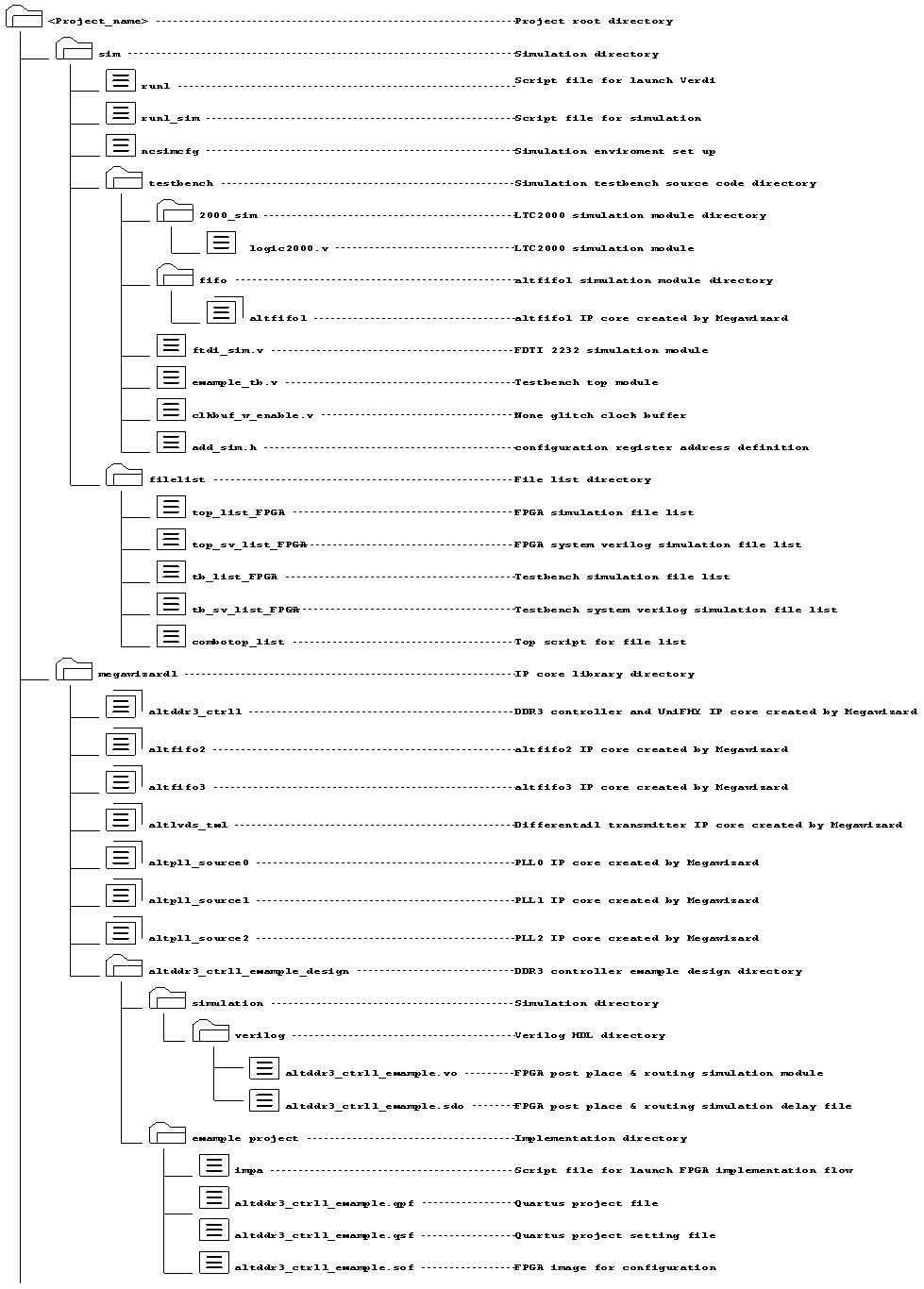

整个设计、仿真和实现环境在 redhat LINUX 操作系统上呈现。目录的设置如图 20 所示。

图 20:设计和仿真文件文件夹

系统配置流程

接通 LTC2000 更新时钟源。

打开 FPGA 板电源(系统时钟应存在)。

打开 FPGA 板电源(系统时钟应存在)。

打开 DC2085A 板电源。

加载 FPGA 映像。

将 FTDI 配置为 MPSSE 模式。

在FTDI的GPIOL3/BDBUS7上生成FPGA的复位脉冲。

通过 FTDI 配置端口检查 FPGA ID 寄存器,以验证 FPGA 映像是否正确。

设置 FPGA 控制寄存器位 MEMSIZE 和 MODE,以配置缓冲器大小和传输模式。

通过设置 DAC 关断寄存器位 DACPD 来接通 LTC2000。

通过 FTDI 配置 LTC2000 至 SPI。

通过FTDI配置端口检查FPGA时钟状态寄存器位DDRRDY,PLL0,PLL1,DDRPLL以验证系统时钟;检查 STRATIX FPGA 板和 LTC2000 的 DDR3 控制器参考时钟和 DDCK 是否可用。DDR3 初始化完成。

将 FTDI 配置为 FIFO 模式。

开始通过FTDI向FPGA发送DAC数据。

监视 LCD 显示和来自 LTC2000 输出的波形。

结论

Altera Stratix 4 GX FPGA系列具有许多有用的特性,允许设计一个与LTC2000的稳健接口。本应用笔记中的设计可直接用作DAC的评估工具。高速数据接口可用作客户设计的起点。

审核编辑:郭婷

-

FPGA

+关注

关注

1630文章

21759浏览量

604354 -

转换器

+关注

关注

27文章

8728浏览量

147445 -

lvds

+关注

关注

2文章

1043浏览量

65864

发布评论请先 登录

相关推荐

浅谈如何克服FPGA I/O引脚分配挑战

NMEA2000连接器的配电触点

NMEA2000_7/8连接器的电气规格

Lattice Avant-G FPGA的电源解决方案

RJ45连接器的优势知多少?解读LP系列RJ45连接器不止快更可靠

Xilinx 7系列FPGA功能特性介绍

如何利用FPGA系列的专用I/O功能将LTC2000连接至FPGA上

如何利用FPGA系列的专用I/O功能将LTC2000连接至FPGA上

评论