本文介绍开发组合逻辑电路时可能发生的意外开关事件,称为危险。

本文是关于使用逻辑门进行组合电路设计和仿真的介绍性系列文章的第二部分。在上一篇文章中,我们介绍了 组合逻辑电路 以及如何简化它们。

在这里,我们将探讨静态 0 危害、静态 1 危害和动态危害。

什么是逻辑危险?

在复杂的逻辑电路中,输出端可能会出现不需要的临时开关事件。图1显示了组合逻辑电路中可能发生的三种危险:

静态 0 危险: 输出在本应保持 0 时暂时更改为 1

静态 1 种危险: 输出在本应保持 1 时暂时更改为 0

动态危险: 输出在应该进行单个逻辑转换时会多次更改;从 0 到 1 或从 1 到 0

图1. 三种类型的组合逻辑危害

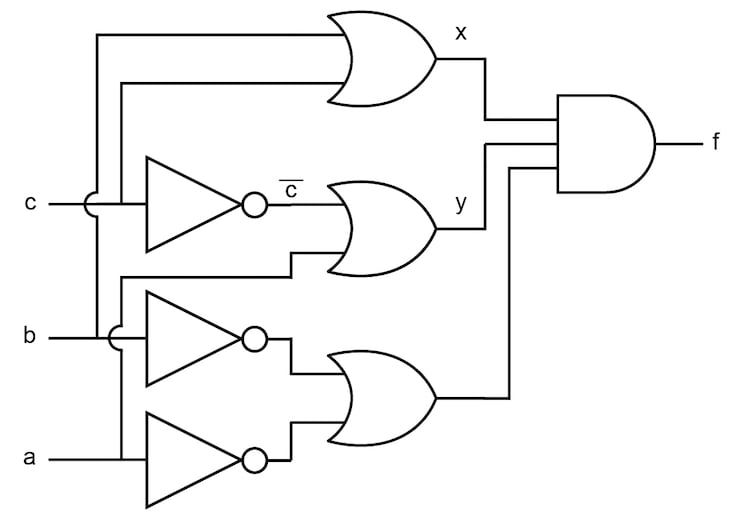

让我们检查图2中的简单电路,看看静态0危险是如何产生的。

图2. 具有静态0-危险的组合逻辑电路

我们假设所有门都具有相同的传播延迟时间常数 d。在图3的时序图中,输入a = b = 0。输入 c 从逻辑 0 变为 1 后的一个栅极延迟,输出 c‘

和 x 的状态也发生变化。由于 x 和 y 现在(暂时)都设置为 1,这会导致最终输出 f 从 0 变为 1 的后续变化。

但是,当输出 f 的状态发生变化时,其输入 y 也会发生变化,从 1 到 0。在 y 的这种变化通过最终门传播后,输出 f

返回到其最终状态零。

以下是静态 0 危害的示例:

图3. 显示静态 0 危险时的序图

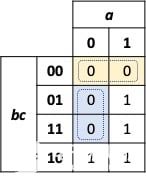

如果我们查看图2电路的Karnaugh图,我们可以看到静态0危险的机会。对于 0

输出,有两个相邻但不相交的最小项,由蓝色和棕褐色阴影突出显示。对于和逻辑函数的乘积,共享最小项未覆盖的任何两个相邻零都可能导致静态 0 危险。

图4. 显示静态-0危害的卡诺地图

使用和的乘积从中推导出的逻辑函数为:

当 a 和 b 均为 0 时,输入 c 可以在 0 和 1 状态之间更改,而无需更改 f

的“最终”值。但是,由于某些电路实现的传播延迟不同,因此可能存在静态0危险。

修复组合逻辑电路中的静电危害

我们可以消除图2电路中的静态-0危害,方法是在两个相邻项周围添加一个额外的分组,如图5中的红色突出显示框所示。

图5. 用于消除静态 0 危害的 Karnaugh 地图分组

新的逻辑函数是:

从纯数字逻辑的角度来看,序列中的第三个和项是不必要的。但是,当 a 和 b 均为 0 时,这个额外的总和  保持为 0。因此,它不受先前导致静态-0危害的c变化的影响。

保持为 0。因此,它不受先前导致静态-0危害的c变化的影响。

使用这种冗余逻辑,我们可以创建一个执行相同逻辑功能的新电路,但没有静态0危险。这个新电路如图6所示。

图6. 消除静态0危险的组合逻辑电路

发现并消除静态-1危害

识别和修复静态 1 危害与静态 0 危害基本相同。使用 Karnaugh 映射查找未被同一最小项覆盖的相邻逻辑 1 输出。对于发现的每个相邻的 1

组合,添加一个额外的分组以消除潜在危险。

异步逻辑与同步逻辑

与危险相关的瞬态脉冲问题在同步电路中很少成为问题。它们旨在在每个时钟周期内留出足够的时间来解决静态和动态危险的毛刺。

另一方面,可以立即响应信号变化的异步逻辑电路可能会受到很大影响。例如,等待响应正 0 到 1 逻辑转换的异步逻辑电路会在图 3

的时序图中错误地做出反应。即使在主要同步设计中,系统复位和当前信号通常也是异步的,因此容易受到危险的影响。

-

电路

+关注

关注

173文章

5994浏览量

173698 -

逻辑

+关注

关注

2文章

834浏览量

29575 -

组合逻辑电路

+关注

关注

6文章

71浏览量

14761

发布评论请先 登录

相关推荐

组合逻辑电路的分析与设计-逻辑代数

什么是组合逻辑电路 如何使用verilog描述组合逻辑电路

组合逻辑电路中的危害

组合逻辑电路中的危害

评论