LTC®6268 和 LTC6269 是一款单通道 / 双通道 500MHz FET 输入运算放大器,具有极低的输入偏置电流和低输入电容。 它还具有低输入参考电流噪声和电压噪声,使其成为高速跨阻放大器、CCD 输出缓冲器和高阻抗传感器放大器的理想选择。其低失真使得 LTC6268 / LTC6269 成为驱动 SAR ADC 的理想放大器。

跨阻放大器中的噪声

为了在广泛的应用中最大限度地降低 LTC6268 的噪声,我们仔细考虑了折合到输入端的电压噪声 (eN)、折合到输入端的电流噪声 (iN) 和输入电容 C在.

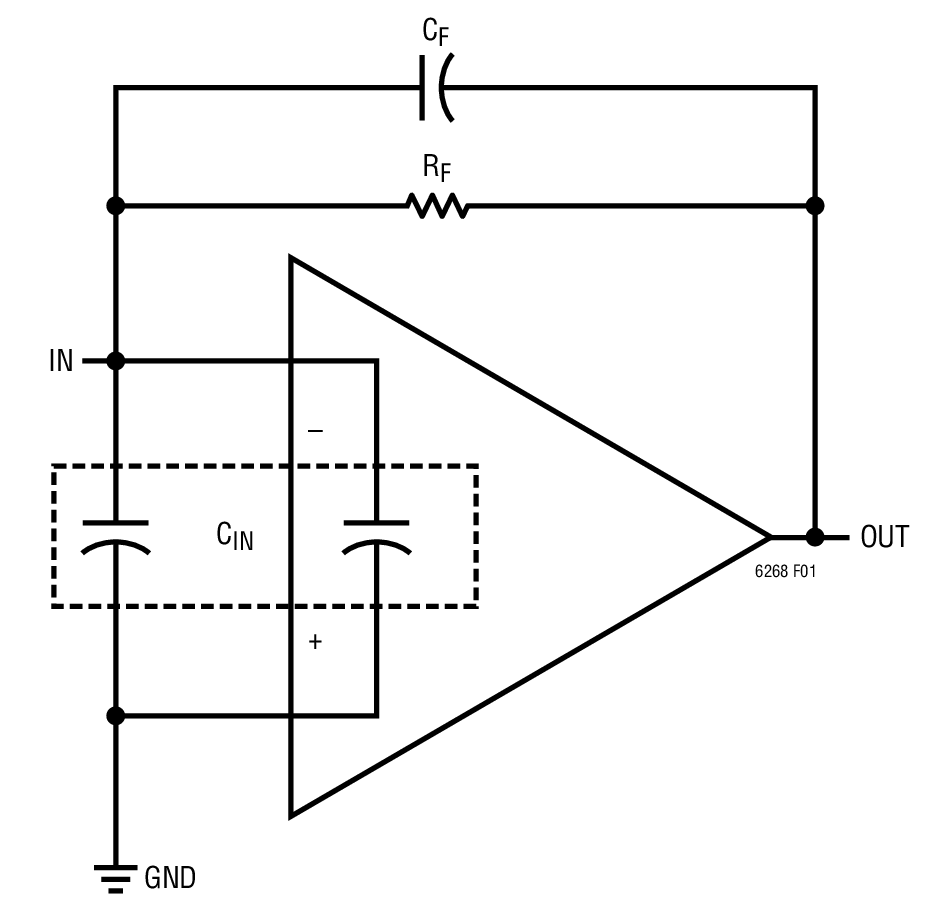

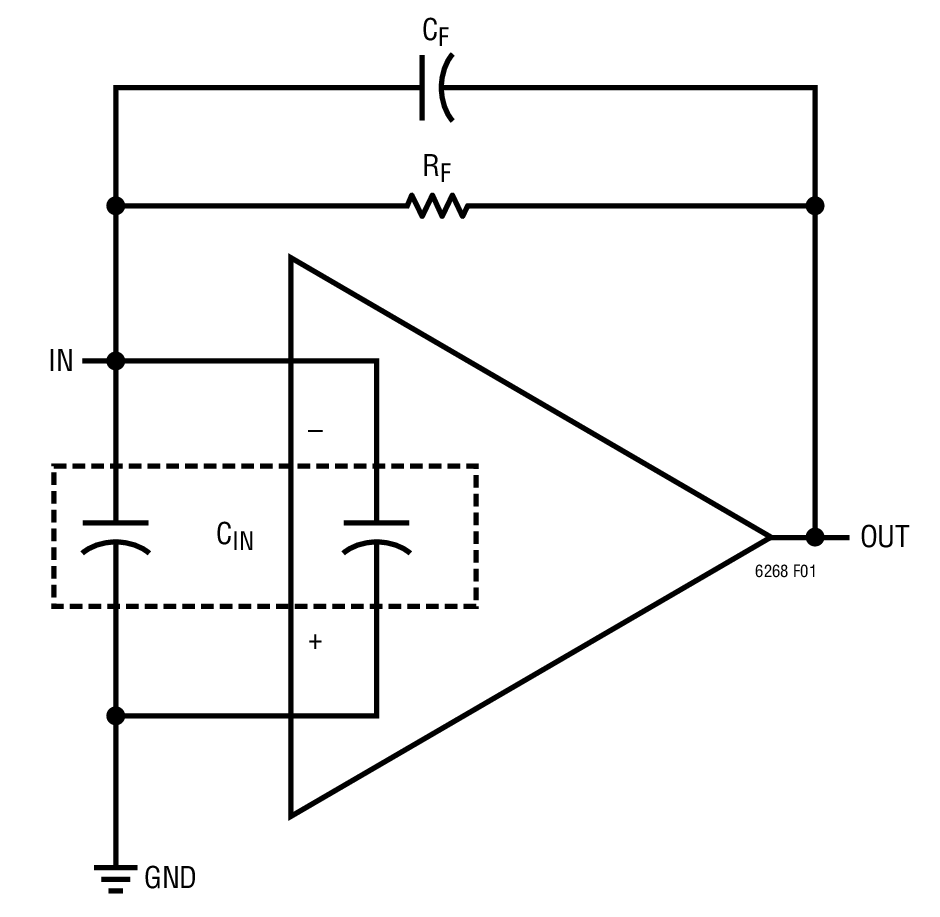

对于图1所示的跨阻放大器(TIA)应用,上述三个运算放大器参数加上反馈电阻值RF,以不同的方式影响噪声行为,外部组件和迹线将添加到C在.

图1.简化的 TIA 原理图

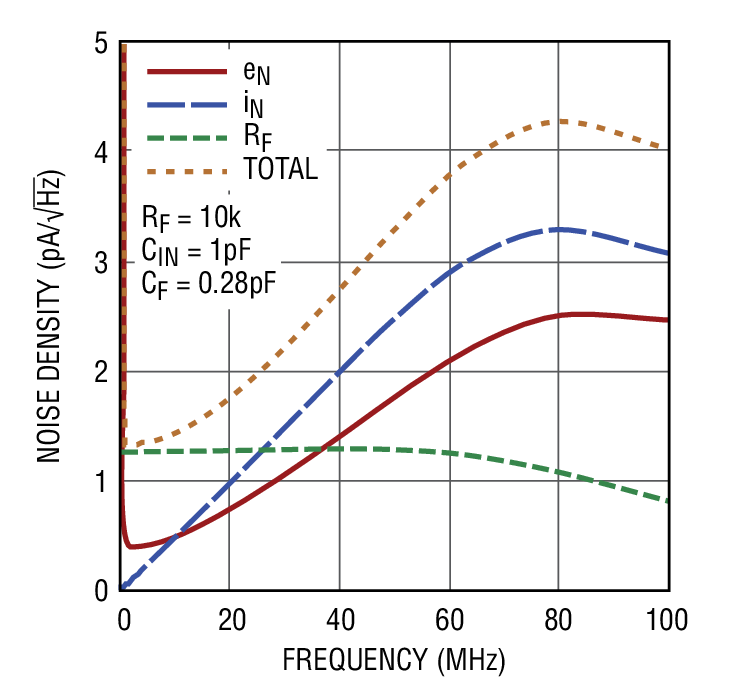

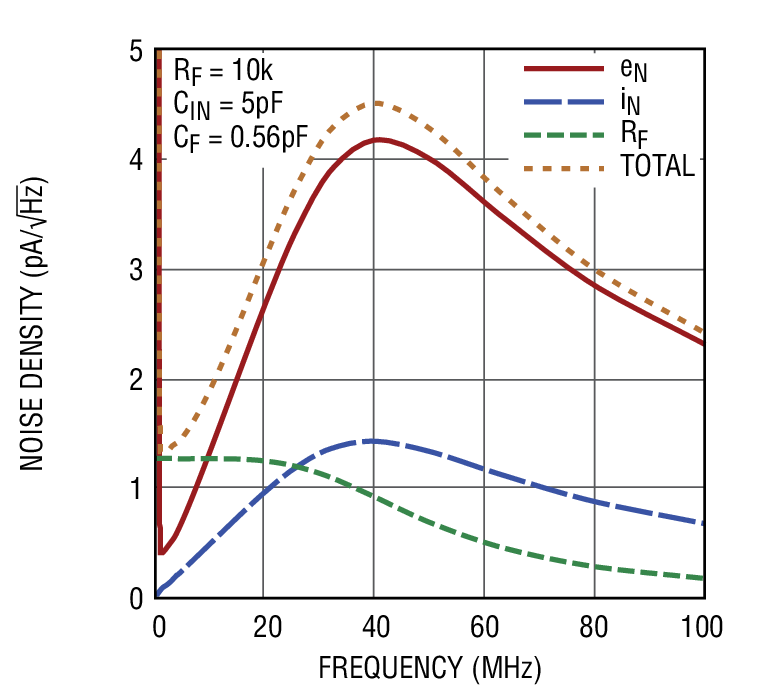

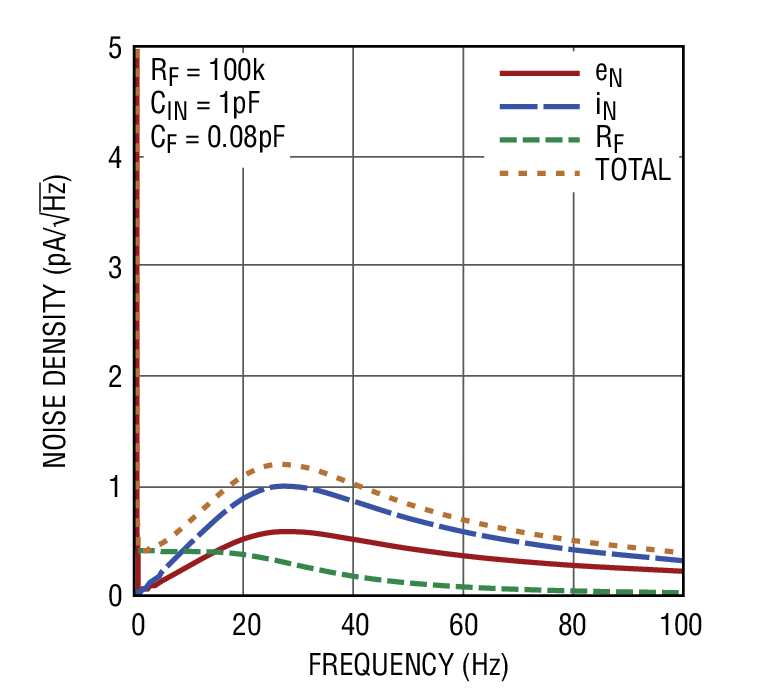

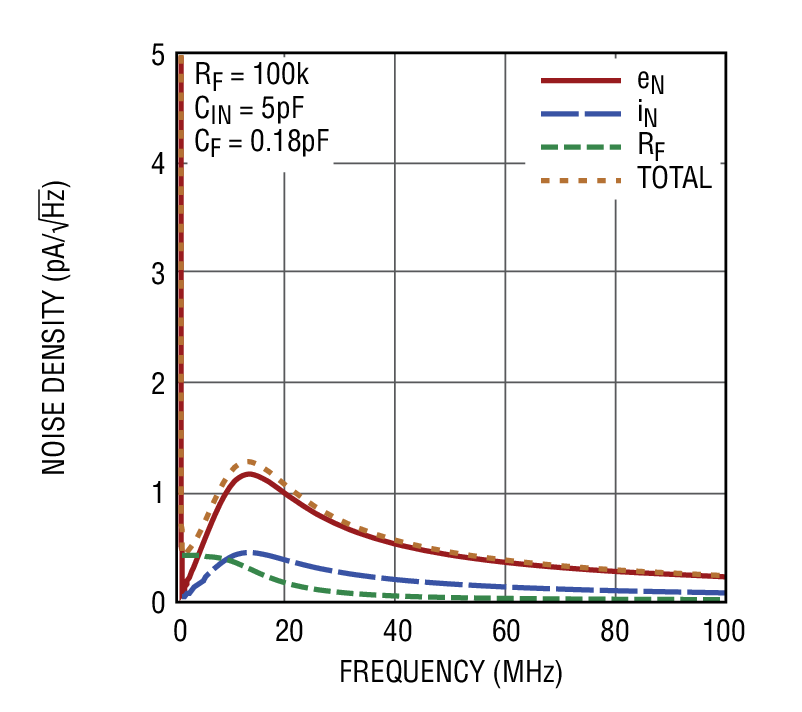

独立了解每个参数的影响非常重要。输入折合到的电压噪声(eN) 由在较低频率下占主导地位的闪烁噪声(或 1/f 噪声)和在较高频率下占主导地位的热噪声组成。对于 LTC6268,1/f 转折或 1/f 与热噪声之间的转换频率为 80kHz。该 iN在负输入端,RF对折合到输入端的噪声电流的贡献相对直接,而eN噪声增益会放大贡献。由于没有增益电阻,因此使用反馈电阻(RF) 结合 C 的阻抗在作为 (1 + 2π RF• C在• 频率),随频率增加。所有贡献都将受到闭环带宽的限制。等效输入电流噪声如图2-5所示,其中eN表示折合到输入端的电压噪声(eN), iN表示折合到输入端的电流噪声(iN),和 RF表示反馈电阻的贡献(RF).TIA 增益 (RF) 和输入电容 (C在) 也显示在每个图上。比较图2和图3,以及图4和5的更高频率,eN当 C在由于上述放大而高(5pF),而当C时iN占主导地位在低 (1pF)。

图2.噪声与频率 C在= 1pF, CF= 0.28pF, RF= 10kΩ

图3.噪声与频率 C在= 5pF, CF= 0.56pF, RF= 10kΩ

图4.噪声与频率 C在= 1pF, CF= 0.08pF, RF=100kΩ

图5.噪声与频率 C在= 5pF, CF= 0.18pF, RF= 100kΩ

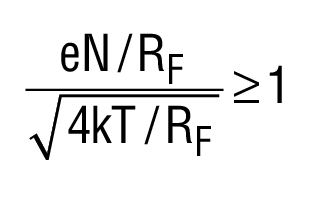

在较低频率下,RF贡献在 10k 和 100k 中占主导地位。由于宽带eN为 4.3nV/√Hz(参见典型性能特征),RF在较低频率下的贡献将成为一个较小的因素,如果 RF小于1.16kΩ,如下式所示:

优化 TIA 应用的带宽

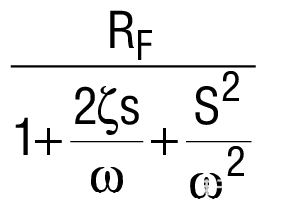

如果不加以控制,反相输入节点的电容可能会导致放大器稳定性问题。当运算放大器周围的反馈是阻性的(RF),将使用 R 创建一个极点F||C在.该极点会产生过多的相移和可能的振荡。参考图 1,输出端的响应为:

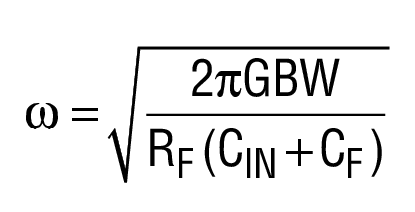

其中 RF是TIA的直流增益,ω是闭环的固有频率,可以表示为:

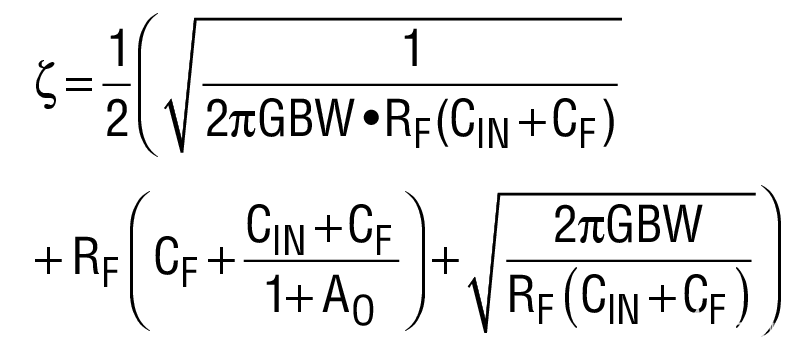

ζ是环路的阻尼系数,可以表示为

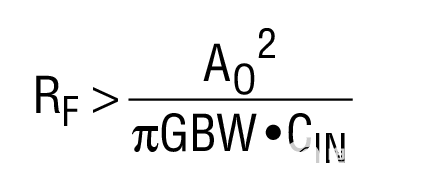

其中 C在是运算放大器反相输入节点处的总电容,GBW是运算放大器的增益带宽。无论 C 如何,系统在两个区域都是稳定的F.第一个区域是当 RF小于 1/(4π∙C在∙GBW)。在这个区域,极点由反馈电阻和C产生在频率很高,不会引起稳定性问题。第二个区域是:

其中 AO是运算放大器的直流开环增益,由R形成的极点FC在是主导极点。

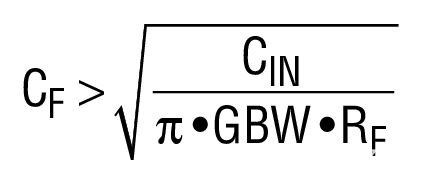

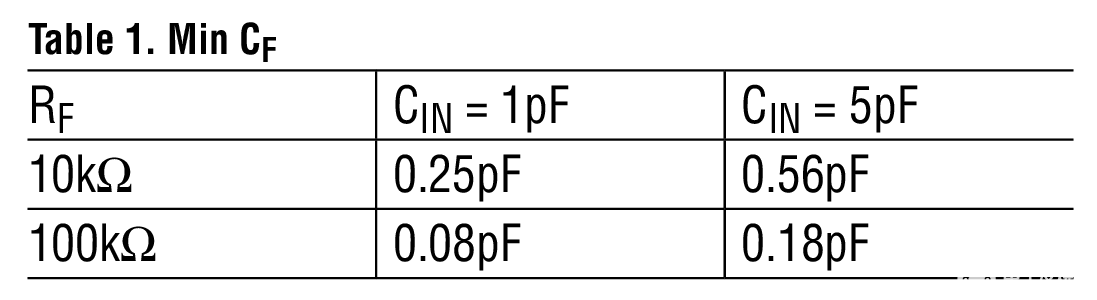

对于 RF在这两个区域之间,小电容CF与 R 并行F可以引入足够的阻尼来稳定回路。通过假设 C在>> CF,C 需要满足以下条件F,

上述条件意味着较高的GBW将需要较低的反馈电容CF,这将具有更高的环路带宽。表 1 显示了最佳 CF对于 RF10kΩ 和 100kΩ 和 C在1pF 和 5pF。

通过更高增益 TIA 实现更高的带宽

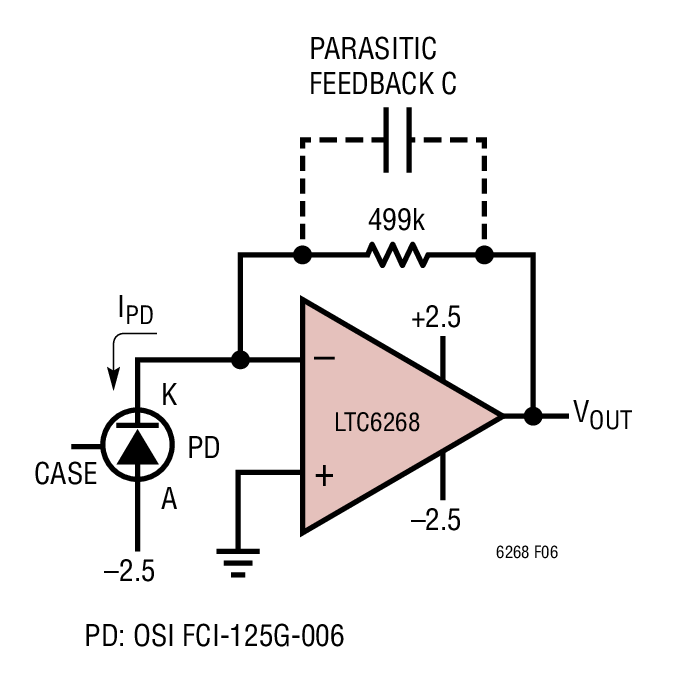

良好的布局实践对于从TIA电路获得最佳结果至关重要。以下两个示例显示了与 LTC6268 在 499kΩ TIA 中截然不同的结果。(请参阅图 6。第一个例子是在基本电路布局中使用0603电阻。在简单的布局中,无需花费大量精力来降低反馈电容,实现的带宽约为2.5MHz。在这种情况下,TIA 的带宽不受 LTC6268 的 GBW 的限制,而受反馈电容降低 TIA 的实际反馈阻抗 (TIA 增益本身)这一事实的限制。基本上,这是电阻带宽限制。499kΩ的阻抗在高频下被其自身的寄生电容降低。根据2.5MHz带宽和499kΩ低频增益,我们可以估计总反馈电容为C = 1/(2π • 2.5MHz • 499kΩ) = 0.13pF。这是相当低的,但可以进一步减少。

图6.LTC6268 和低电容光电二极管采用 499kΩ TIA

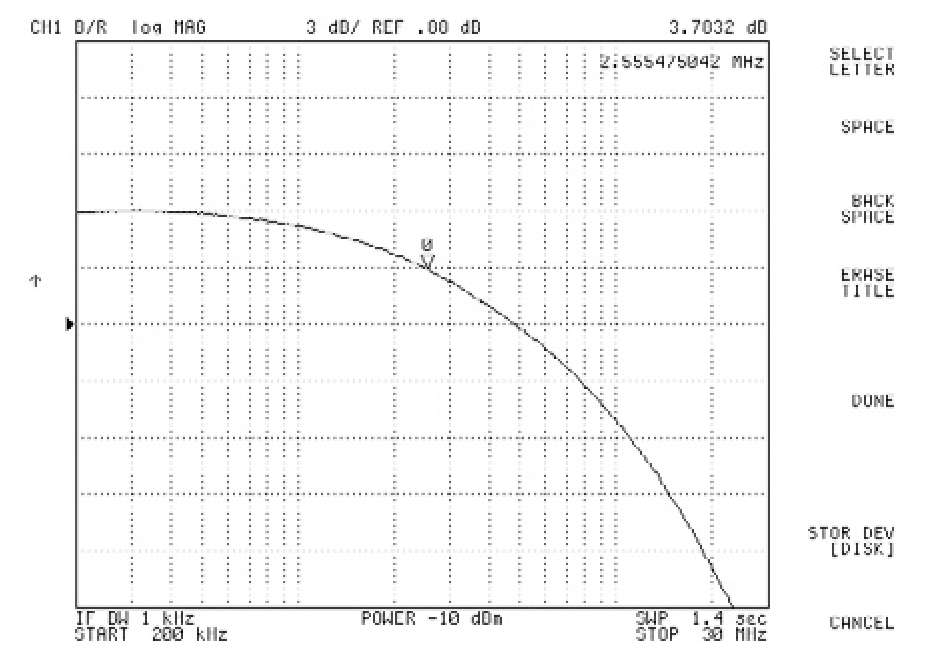

图7.频率响应为 499kΩ TIA,无需额外努力降低反馈电容为 2.5MHz

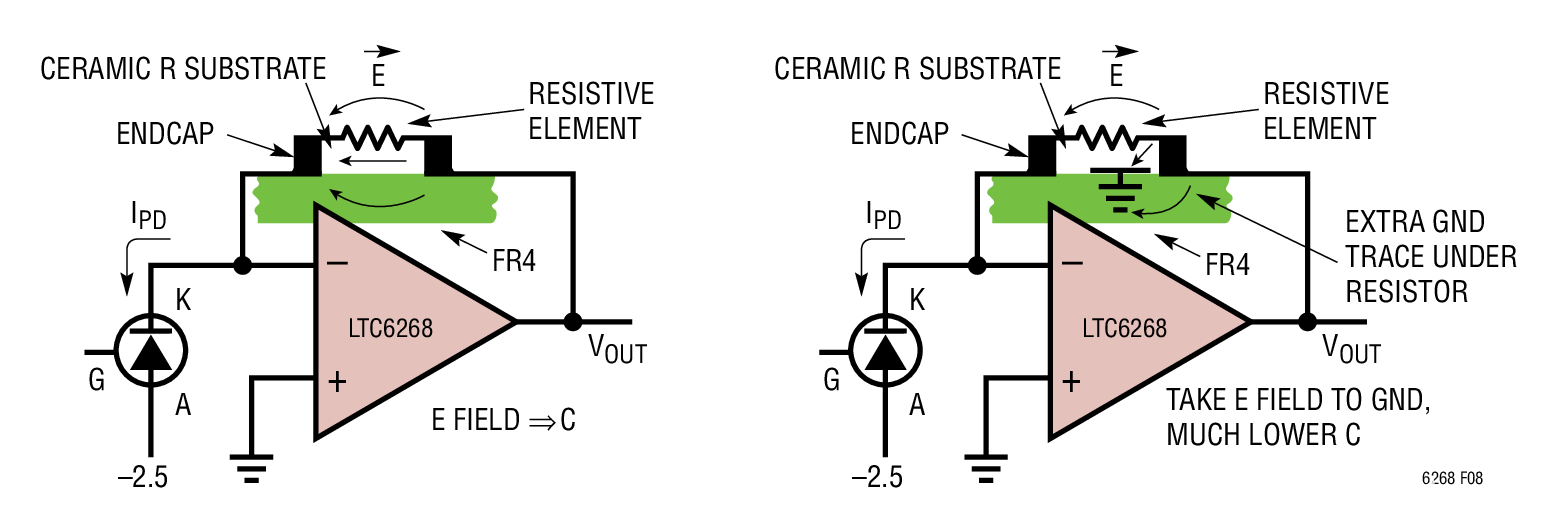

通过一些额外的布局技术来降低反馈电容,可以增加带宽。请注意,我们正在增加499kΩ电阻的有效“带宽”。降低电容的主要方法之一是增加极板之间的距离,在这种情况下,极板是分量电阻器的两个端盖。出于这个原因,使用更长的电阻器将服务于我们的目的。0805 比 0603 长,但其端盖面积也更大,电容再次增加。然而,增加端盖之间的距离并不是降低电容的唯一方法,电阻端盖之间的额外距离也允许轻松应用另一种技术来降低反馈电容。降低板间电容的一种非常有效的方法是屏蔽产生电容的E场路径。在这种特殊情况下,方法是在靠近TIA输出端的电阻焊盘之间放置一条短接地走线。

这种接地走线可防止输出场到达电阻的求和节点端,并有效地将磁场分流到地。使走线靠近输出端会略微增加输出负载电容。有关图形表示,请参见图 8。

图8.左侧为正常布局,右侧为字段调车布局。只需在反馈电阻下方添加一条接地走线,就可以将磁场从反馈侧分流并转储到地。请注意,Fr4和陶瓷的介电常数通常为4,因此大部分电容在固体中而不是通过空气。(右侧未显示缩小的焊盘尺寸。

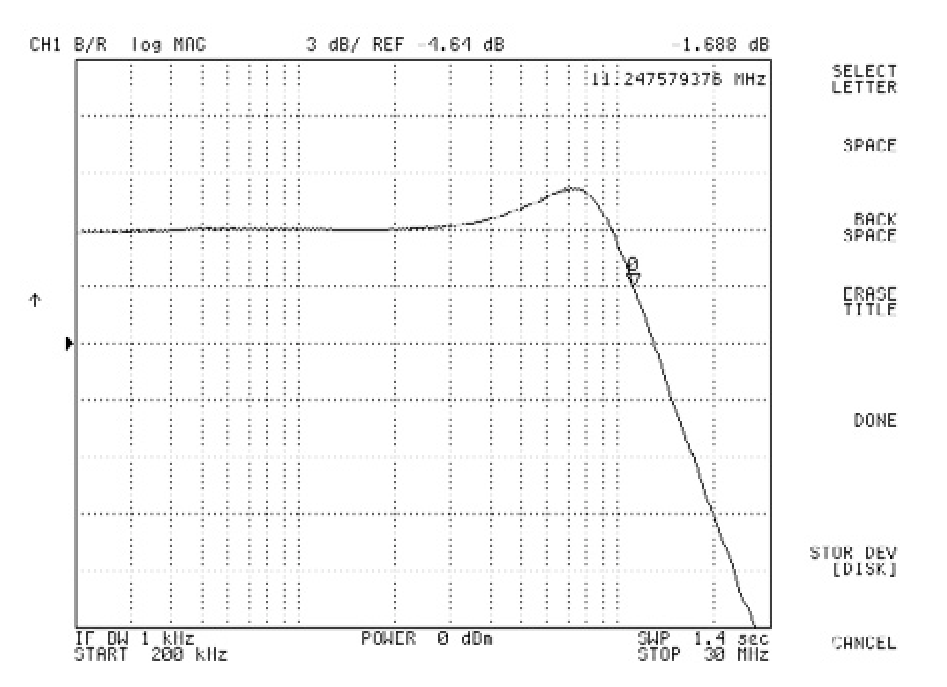

图9显示了带宽的急剧增加,只需仔细注意反馈电阻周围的低电容方法。带宽从2.5MHz提高到11.2MHz,系数大于4。实施的方法有两种:

最小的焊盘尺寸。请与您的电路板组装商联系,了解可接受的最小焊盘尺寸,或使用其他方法组装此电阻器,以及

使用靠近输出侧的反馈电阻下方的接地走线屏蔽反馈电容。

图9.LTC6268 采用 499kΩ TIA 封装,具有额外的布局工作以减小反馈电容,实现了 11.2MHz 带宽

审核编辑:郭婷

-

传感器

+关注

关注

2553文章

51511浏览量

757252 -

放大器

+关注

关注

143文章

13640浏览量

214395 -

运算放大器

+关注

关注

215文章

4974浏览量

173710

发布评论请先 登录

相关推荐

求助,求推荐超低噪声跨阻放大器

跨阻放大器的带宽扩展技术

跨阻放大器中的噪声参数及因素考虑

跨阻放大器噪声考虑因素

跨阻放大器噪声考虑因素

评论