前面几篇文章讲到了串行总线的预加重与均衡理论,概念性的东西比较多,大家如果不是从事信号完整性仿真等相关工作人员,理解起来会有一定的困难。很多关注高速先生公众号的都是从事高速PCB 设计(Layout)的小伙伴,信号处理的理论可能对这些朋友日常工作帮助不是太大,这些朋友可能更多关注的是与布线相关的话题。

经常会有PCB设计的同事问我,板子上PCIe或者10G光口这类走线最长不能超过多少?速率不是那么高的信号,例如USB2.0,是不是就可以走很长的线了?速率到达多高,就要特别注意走线的损耗的问题?这些问题核心还是涉及到高速信号速率与传输线损耗之间的关系,如果我们对不同速率的信号通过传输线后的衰减有一个基本认识,就可以对布线长度做一个基本的评估了。

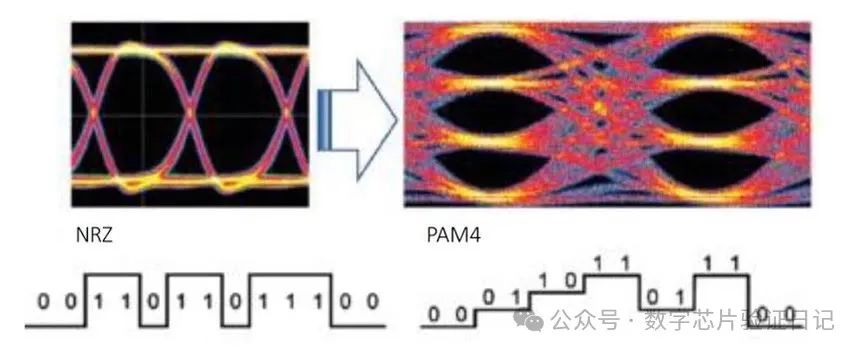

在回答这些问题之前,我们应该对不同频率的信号经过一段长度的传输线后损耗程度有一定的了解。大家觉得传输速率为5Gbps的数字信号(不经过任何预加重或者均衡处理),经过一段15inch的传输线后(普通板材),眼图还可以打开吗,8G呢?为了解开大家的疑惑,我做了如下仿真,如下图所示:

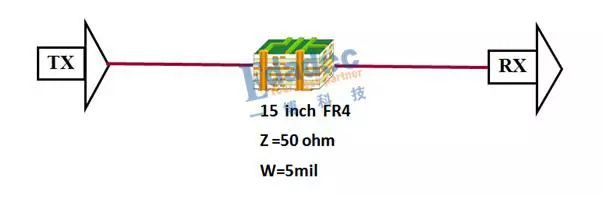

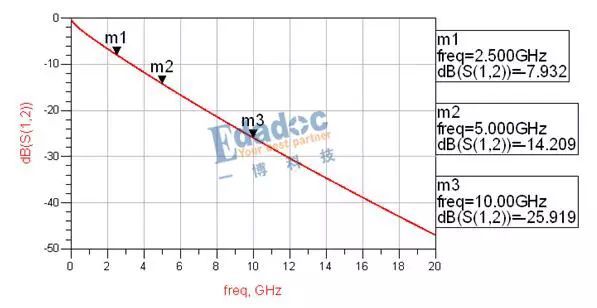

我们假设这个通信系统的驱动和接收器件都是理想模型,理想模型就意味着驱动和接收都是匹配较好,除了传输线的损耗之外,信号不受其他干扰项的影响。假设该传输线的介质为普通FR4,线宽为5mil,阻抗为50ohm,线长为15inch。首先我们来看下通道的插损曲线,如下图:

通过插损曲线我们可以看出,通道的损耗还是很大的,在2.5G的时候就达到了-7.9dB,转化成幅度,大概为0.4,也就是这个频率下,信号的幅度损耗了60%。我们来看看不同速率的信号在穿过这个通道后会变成什么样子。

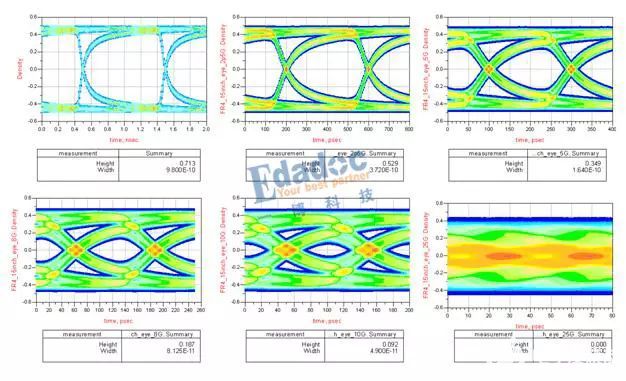

发送端为理想PRBS信号,发送端信号峰峰值为1V,上升和下降时间为10ps,我们分别仿真了速率为1G,2.5G,5G,8G,10G,25G的信号,通过15inch的传输线后,眼图对比如下:

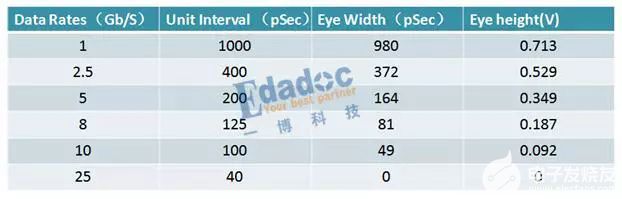

眼高和眼宽数据统计对比如下:

由上表我们可以看出,随着信号频率的提高,损耗的影响变得越来越大。至于这个影响到底有多大,我们可以参考上面的表格做一个大概的评估。

比较较真的网友可能又有疑惑了,你说了这么多,我只想知道我在布线的时候高速线到底最长可以走多长,你能不能给个准确的数值。遇到这些问题,高速先生也不能明确的给出答案。我只能说,it depends…..从传输通道来说,线长只是影响损耗的因素之一,还有很多关键的因素影响着通道的损耗,比如说我们选用的板材,换层孔的类型,数量,使用的铜箔类型,线宽线厚等等。对于高速串行信号来说,不同的芯片信号处理能力也不一样,也就是所谓的预加重和均衡能力不一样,既然芯片的性能有差异,我们对传输通道的评估也就不能一概而论了。最好的方法就是拿到芯片的模型进行仿真评估,综合考虑这些因素对信号的影响,这也是SI工程师存在的价值。

审核编辑 :李倩

-

PCB设计

+关注

关注

394文章

4670浏览量

85283 -

PCIe

+关注

关注

15文章

1217浏览量

82445

发布评论请先 登录

相关推荐

写 Verilog 如何做到心中有电路?

采用OPA656构成电压跟随器,测试信号通过BNC后的情况,1M开始往后衰减的就特别厉害怎么解决?

PCB设计与PCB制板的紧密关系

PCB设计基本原则总结,工程师必看

什么是PCB扇孔,PCB设计中对PCB扇孔有哪些要求

PCB设计阻抗不连续的原因及解决方法

PCB设计软件有哪些 pcb设计软件哪个好用

pcb设计布局布线原则及规则

PCB设计信号线跨分割会有什么影响

PCB设计检查规范指南

PCB设计成败应该要注意的问题分享

PCB设计:直观信号眼图,衰减心中有数

PCB设计:直观信号眼图,衰减心中有数

评论