随着FPGA的集成度越来越高,规模越来越大,设计越来越复杂,IC行业的竞争也越来越激烈,产品的交付周期越来越短,这与人类有限的设计能力形成了巨大矛盾。如果FPGA设计还是全部由设计者从最底层的代码写起,那么必然不能在越来越苛刻的开发周期内完成相关项目。

而IP核的出现,解决了这个问题。IP核是一段具有特定电路功能的硬件描述语言程序,该程序通常与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片。由于IP核将一些在数字电路中常用,但比较复杂的功能块设计成可修改参数的模块,因此FPGA的设计人员可以通过调用相关IP核来完成所需逻辑功能,从而节省了大量的开发时间。调用IP核能避免重复劳动,大大减轻设计人员的负担,因此使用IP核必然成为将来FPGA设计的一个发展趋势。

按IP核的硬件描述级实现程度,可将它分为三类:即软核、硬核、固核。

IP软核一般指的是用硬件描述语言描述的功能块,它并不涉及用什么具体电路元件实现这些功能,软核的代码直接参与设计的编译流程,就像我们自己编写的HDL代码一样,虽然一般会对软核的RTL代码进行加密,但是其保密性还是比较差。

IP硬核是以经过完全的布局布线的网表形式提供,由于不再参与设计的编译流程,因此它的性能具有很强的可预见性,并且保密性好,不过移植性差。

IP固核是软核与硬核的一个折中,它只对描述功能中一些比较关键的路径进行预先的布局布线,而其他部分仍然可以任由编译器进行相关优化处理。例如,当你使用IP核生成一个8x8的乘法器时,如果选择使用逻辑资源块来实现的话,那么此时的乘法器IP核就相当于一个软核;

如果你选择使用DSP资源来实现的话,那么此时的乘法器IP核就相当于一个硬核;如果你要用DSP资源生成一个36x36的乘法器时,那么FPGA恐怕需要若干DSP资源来实现,这时候,每个DSP核的布局布线是固定的,但是到底选择那几个DSP资源来实现是可以由编译器来决定的,因此此时的乘法器IP核就相当于一个固核。

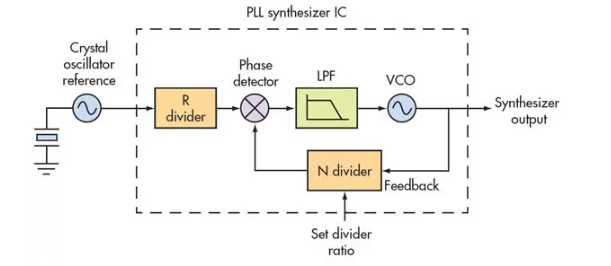

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。

一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成。

FIFO: 是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

FIFO的分类根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

FIFO的宽度: 也就是英文资料里常看到的THE WIDTH,它指的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的数据(如果宽度为N)。如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小,个人认为FIFO深度的计算并无一个固定的公式。

在FIFO实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。在一个具体的应用中不可能由一些参数精确算出所需的FIFO深度为多少,这在写速度大于读速度的理想状态下是可行的,但在实际中用到的FIFO深度往往要大于计算值。

一般来说根据电路的具体情况,在兼顾系统性能和FIFO成本的情况下估算一个大概的宽度和深度就可以了。而对于写速度慢于读速度的应用,FIFO的深度要根据读出的数据结构和读出数据由那些具体的要求来确定。

ADC/DAC: adc是analog-to-digital converter的缩写,指模拟/数字转换器。我们常用的模拟信号,如温度、压力、电流等,如果需要转换成更容易储存、处理的数字形式,用模/数转换器就可以实现这个功能。

adc将模拟输入信号转换成数字信号的电路或器件。模数转换器的实例有逐次逼近adc,电压-频率(v/f)转换器,双斜率adc和高速闪烁adc。模数转换器也称为数字化仪。a/d转换的作用是将时间连续、幅值也连续的模拟量转换为时间离散、幅值也离散的数字信号,因此,a/d转换一般要经过取样、保持、量化及编码4个过程。

在实际电路中,这些过程有的是合并进行的,例如,取样和保持,量化和编码往往都是在转换过程中同时实现的。dac是digital-to-analog converter的缩写,指数字/模拟转换器。数字量是用代码按数位组合起来表示的,对于有权码,每位代码都有一定的位权。

为了将数字量转换成模拟量,必须将每1位的代码按其位权的大小转换成相应的模拟量,然后将这些模拟量相加,即可得到与数字量成正比的总模拟量,从而实现了数字/模拟转换。dac主要由数字寄存器、模拟开关、位权网络、求和运算放大器和基准电压源(或恒流源)组成。用存于数字寄存器的数字量的各位数码,分别控制对应位的模拟电子开关,使数码为1 的位在位权网络上产生与其位权成正比的电流值,再由运算放大器对各电流值求和,并转换成电压值。

IP代表知识产权,从它的名字我们就能猜到IP核应该不是可以随便使用的。事实上,大部分IP核都是需要付费的,例如RS编码器、FIR滤波器、SDRAM控制器、PCI接口等。不过仍有很多免费的IP核资源,这其中最主要的就是每个FPGA厂商都会为自己的软件集成开发环境提供一些比较基本的免费的IP核来增加自家产品的行业竞争力。例如最最常用的FIFO模块、PLL模块等等。对于我们平常的设计来说,利用好这些免费的IP核就能达到事半功倍的效果。

-

FPGA

+关注

关注

1629文章

21748浏览量

604026 -

IC

+关注

关注

36文章

5957浏览量

175745

发布评论请先 登录

相关推荐

分享一些FPGA常见IP核

分享一些FPGA常见IP核

评论