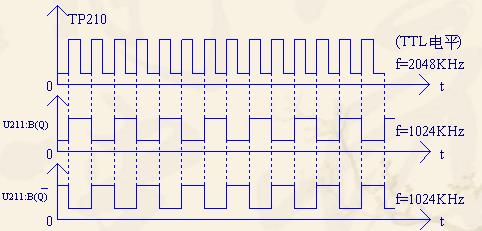

保持多个电信设备之间的时钟同步是任何大型安装的基本功能。一种常见的时钟分配方法由ITU-T G.703 2048kHz同步接口(T12)指定。虽然DS26303 E1/T1/J1八通道线路接口单元(LIU)完全支持该规范,但需要一些额外的配置设置才能正常工作。本应用笔记介绍如何使能2048kHz同步接口模式,并配置DS26303以用于时钟分配应用。

介绍

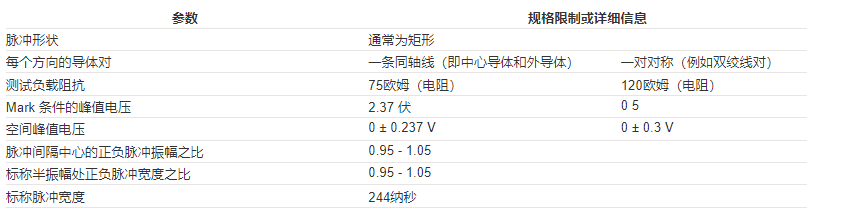

DS26303 E1/T1/J1八通道接口单元(LIU)鲜为人知的特性之一是它能够发送和接收符合国际电信联盟ITU-T建议书G.703(2001年11月)第13节2048kHz同步接口(T12)的信号。本应用笔记介绍如何正确编程DS26303,使能2048kHz同步接口模式,使器件可用于时钟分配应用,如建筑集成定时电源(BITS)或同步电源单元(SSU)。需要注意的是,DS26303有两种型号可供选择:DS26303-120和DS26303-75。两者之间的唯一区别是默认的E1线路阻抗设置。人们需要意识到这一事实,并确保在设计阶段使用的特定设备与用于制造的设备相同。

DS26303编程用于2048kHz同步接口模式

对DS26303进行编程以支持2048kHz同步接口是一个多步骤的过程,需要使用DS26303数据资料中未记录的一些寄存器。所有未记录登记册的完整说明可在下面的附录中找到。

在使能2048kHz同步接口模式之前,需要执行几个配置步骤来确保DS26303按预期工作。

第 1 步。更改内部时钟图以使用与LIU通道关联的发送时钟(通常是TCLK输入)而不是主时钟(MCLK输入)。默认情况下,当使能2048kHz同步接口模式时,DS26303使用公共MCLK输入作为时钟源。这将导致TTIP/TRING引脚上的输出信号频率锁定到MCLK输入,而不是TCLK输入。要对DS26303进行编程,以TCLK输入作为时钟源,使用以下软件配置。

将地址 0x1F 处的 ADDP 寄存器设置为值 0x03,这将选择全局测试寄存器库。

将地址 0x07 处的 TXDIG 寄存器设置为 0x10 值。通过将TXDIG寄存器的位4设置为1,2048kHz同步接口模式将使用TCLK输入而不是MCLK输入。需要注意的是,改变TXDIG寄存器的位4也会影响通常使用MCLK输入作为时钟的另外两个功能,特别是传输所有1(TAOE)和自动发送所有1(ATAOS)功能。因此,当禁用2048kHz同步接口模式时,需要将该位设置回0。但是,如果工程师希望在启用TAOE或ATAOS时使用TCLK输入作为时钟源,则TXDIG寄存器的第4位可以设置为1。

第 2 步。

更改短路检测电路 (SCDC) 的限流值,以防止禁用 TTIP/TRING 发送器输出。默认情况下,当使能2048kHz同步接口模式时,DS26303的限流值不正确。要用适当的短路电流值对DS26303进行编程,请使用以下软件配置。

将地址0x1F处的 ADDP 寄存器设置为 0x04 到 0x0B 之间的值,该值分别通过 LIU8 测试寄存器组选择 LIU1 测试。

将地址0x05处的TXCMDA寄存器设置为下面列出的值之一(表1)。这些值应与模板选择 (TS) 寄存器中选择的值同步。例如,当TS寄存器配置为E1 75Ω模式时,将TXCMDA寄存器设置为0x33值。此外,当启用 G.703 2048kHz 同步接口模式时,TS 寄存器中的发射阻抗终止设置不应关闭。请注意,TXCMDA 寄存器位 7:6 应始终保持在 0;位 5 控制 SCDC 覆盖启用;位 4:0 包含新的短路电流限制值。虽然可以对极限值进行调整,但不建议这样做,因为选择这些值是为了防止损坏设备。

表 1.TXCMDA 寄存器设置

| TS 模式设置 | TXCMDA 价值 |

| E1 75Ω | 0x33 |

| E1 120Ω | 0x2F |

完成这两个配置步骤后,DS26303被正确配置为支持2048kHz同步接口模式。

要为DS26303的一个或多个通道编程,以实现2048kHz同步接口模式,请使用以下软件配置。

将地址 0x1F 处的 ADDP 寄存器设置为 0x01 值,这将选择单个 LIU 寄存器库。

将地址0x08处的G703EN寄存器设置为为相应LIU通道启用2048kHz同步接口模式所需的值。

假设现在按照前面的建议禁用了 TTIP/TRING 发射器输出,请使用以下软件配置启用发射器输出。

将地址 0x1F 处的 ADDP 寄存器设置为 0x00 值,这将选择主寄存器库。

将地址0x12处的OEB寄存器设置为为G703EN寄存器中启用的相同LIU通道启用TTIP/TRING发射器输出所需的值。

结论

只需对DS26303的默认行为稍作改动,器件即可完全支持ITU-T G.703 2048kHz同步接口(T12)规范。本应用笔记描述了需要进行哪些更改,提供了有关这些更改的背景信息,并提供了详细的配置过程。这些信息和DS26303数据资料允许任何设计人员将2048kHz同步接口特性集成到BITS或SSU设计中。

附录:DS26303 所需寄存器信息

DS26303的寄存器空间跨越地址0x00到0x1F。它使用内存库模型,并包含所有 LIU 通道的配置和状态信息。地址0x1F处的ADDP寄存器是一个特殊的寄存器,用作访问不同寄存器库的指针。对于每个寄存器库,此寄存器的功能和值保持不变。但是,对 ADDP 寄存器的更改将更改当前寄存器组,从而更改跨越地址0x00到0x1E的寄存器的功能和值。

以下是有关寄存器的详细信息以及启用ITU-T G.703 2048kHz同步接口(T12)模式所需的每个位的说明。

寄存器名称:ADDP

寄存器银行:存在于所有寄存器库中

寄存器说明:地址指针

寄存器地址:1Fh

| 位# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名字 | ADDP7 | ADDP6 | ADDP5 | ADDP4 | ADDP3 | ADDP2 | ADDP1 | ADDP0 |

| 违约 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 0:地址指针 (ADDP)。

此值用作在主注册库、辅助注册库、个人 LIU 注册库、BERT 注册库和任何测试注册库之间进行选择和切换的指针。例如,软件必须将 ADDP 寄存器设置为 0x00 才能访问寄存器的主库;0xAA以访问二级登记册库;0x01访问个人刘氏登记册库;或0x02访问BERT注册库。有关正确的寄存器库选择,请参见

表 2

。

表 2.地址指针寄存器组选择

| ADDP Register Value | Register Bank Name |

| 0x00 | Primary |

| 0xAA | Secondary |

| 0x01 | Individual LIU |

| 0x02 | BERT |

| 0x03 | Global Test |

| 0x04 | LIU1 Test |

| 0x05 | LIU2 Test |

| 0x06 | LIU3 Test |

| 0x07 | LIU4 Test |

| 0x08 | LIU5 Test |

| 0x09 | LIU6 Test |

| 0x0A | LIU7 Test |

| 0x0B | LIU8 Test |

注册名称:

G703EN

注册银行:

个人 LIU 注册银行 注册说明

:

ITU-T G.703 2048kHz 同步接口启用

寄存器地址:

08h

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | G703EN7 | G703EN6 | G703EN5 | G703EN4 | G703EN3 | G703EN2 | G703EN1 | G703EN0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 0:G703 使能 (G703EN)。

当清除为 0 时,关联 LIU 通道的发射器和接收器处于正常 T1/E1/J1 模式。设置为 1 时,相关 LIU 通道的发射器和接收器将进入 ITU-T G.703 2048kHz 同步接口 (T12) 模式。

注意:此功能仅在设备修订版 A2 及更高版本中可用。

寄存器名称: TXCMDA

寄存器名称: LIU 测试 寄存器组 1 至 8 寄存器说明: 传输线驱动器自定义模式 A

寄存器地址: 05h

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | Reserved | Reserved | SCDCOR | SCC4 | SCC3 | SCC2 | SCC1 | SCC0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 6:保留。

此位应保持清除为 0。

位 5:短路检测电路覆盖 (SCDCOR)。当清除为 0 时,将启用默认线路驱动器电流限制。设置为 1 时,默认线路驱动器电流限制将被 SCC[4:0] 设置的值覆盖。

位 4 到 0:短路电流 (SCC[4:0])。当短路检测电路覆盖(SCDCOR)位设置为1时,这4位的二进制加权值设置短路检测电路电流限制。当线路驱动器电流超过此值时,发射器被禁用,驱动器故障监视器状态设置为1。

注意:此功能仅在设备修订版 A2 及更高版本中可用。

寄存器名称: TXDIG 寄存器名称: 全局测试 寄存器银行

寄存器说明: 传输数字测试模式

寄存器地址: 07h

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | Reserved | Reserved | Reserved | CLKS | Reserved | Reserved | Reserved | Reserved |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 7 到 5:保留。

此位应保持重置为 0。

位 5:时钟选择模式 (CLKS)。当清除为 0 时,当 LIU 通道处于以下模式时,每个 LIU 通道的发射时钟源是主时钟:发送所有 1、自动发送所有 1、ITU-T G.703 2048kHz 同步接口 (T12) 和出厂测试。当设置为 1 时,当 LIU 通道处于上述任何模式时,每个 LIU 通道的发送时钟源是关联的 TCLK 引脚(如果启用了远程环回,则恢复时钟)。

位 3 到 0:保留。这些位应保持清除为 0。

审核编辑:郭婷

-

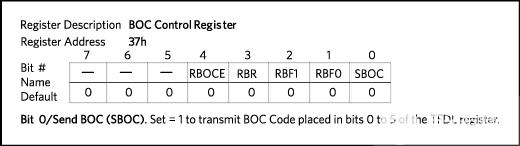

寄存器

+关注

关注

31文章

5622浏览量

130574 -

接口

+关注

关注

33文章

9630浏览量

157762

发布评论请先 登录

itu-t g.711标准介绍

DS26303中文资料

DS26303.pdf

MSM7581 pdf datasheet (ITU-T G

MSM7580 pdf datasheet (ITU-T G

DS26303 LIU的初始化和配置

DS26303短程线路接口单元与IDT82V2048的比较

DS26303短程线路接口单元与LXT384的比较

G.703通信接口转换器

如何在DS26303 LIU上启用ITU-T G.703 2048kHz同步接口

如何在DS26303 LIU上启用ITU-T G.703 2048kHz同步接口

评论