1 绪论

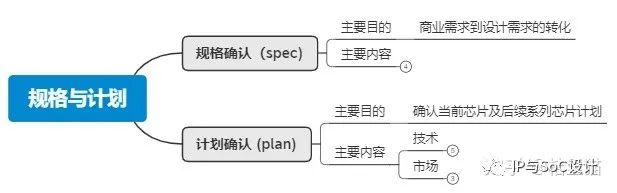

这是芯片设计的第二个步骤。规格(spec)与计划(plan)确定。我们在立项一文中讲过,当时要解决的问题是我们要不要做。如果我们确定了要做,接下来就是要解决怎么做的问题。

在这个阶段我们主要做两件事,规格的确定与计划的敲定。俗话说,凡事预则立,不预则废。由于芯片从立项到上市其实流程非常长,如果在真正动手设计芯片之前没有一个完善的spec和plan,最后做出来的东西必然走形严重。

主要内容如下。

其实看名字就知道这个步骤是干啥的。主要分为两个步骤,确定规格,以及确定计划。

确定规格:立项只是确认了芯片的商业需求,这个步骤就是把商业需求转换为设计需求。

计划确认:确认各种时间计划,以及后续的各种操作。详细内容见后文。

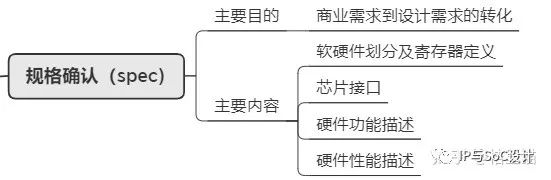

2 确定规格

我们先来讲第一个内容,规格的确认。规格决定了芯片未来的样子。

我们立项的时候的输出应该是商业上的需求。比如我们做个震动检测的AI芯片,支持CNN网络,要跑到多少帧。此处我们需要把这些商业上的东西分解成真正可以设计实现的规格。主要是四个方面内容。

2.1 软硬件划分及寄存器定义

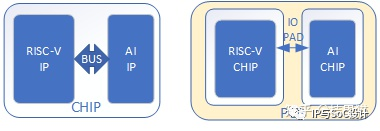

这个部分我理解应该是第一个要完成的,否则后续的功能点没办法确认下来。一般的芯片大致有以下组成方式。一种是SOC类型的,另一种是外挂外设型(套片)的。我们以RISC-V核和AI核组成的AI系统来举例子。

无论是哪种办法,都涉及到软硬件接口划分的问题。为什么要做软硬件划分以及寄存器定义呢?主要还是灵活性、工作量以及能效方面的权衡。任务用C语言写,在CPU上做性能和能效都比较低,但灵活性非常高,只要CPU本身不出错,软件出错了流片后依旧能改。相应的,用HDL(Verilog)实现的硬核能效是比较高的,但是一旦流片没有办法改,所以验证设计工作量都很大。

软硬件如何划分没有统一的章法,主要就是根据实际情况,选定芯片的灵活度。不过大致都是遵循以下几个规则:

·控制类的可以软件做,较为灵活。数据计算类的硬件做,能效较高。

·以后可能升级的组件软件做,灵活度大。以后大概率不动的功能硬件做。

·只能串行的功能可以软件做,可以很好并行化的任务硬件做

一般软件(CPU核)和硬件(我们的芯片)之间的交互是通过寄存器交互的。有了软硬件功能划分以后,下一个重要的步骤就是确定一个配置寄存器列表,也就是开放给软件的接口。这个东西后续是芯片datasheet最重要的组成部分。寄存器也分为几种。大致上以下五个类别。

·只写寄存器。只允许从CPU侧写。一般用于配置芯片。

·只读寄存器。只用于从芯片侧写,一般用于上报一些信息给CPU。

·读写寄存器。CPU和我们的芯片两侧都能写,用户CPU和芯片交互,用于CPU和芯片共同维护一个信息。

·自复位寄存器。配置一个值,然后生效后自动清零。这个主要用在软复位上,也可以叫脉冲或者W1寄存器。

·ROM寄存器。一个固定的值,一般用来标识一些版本信息什么的。

有了寄存器,再确定有几个中断即可。

设计好这几类寄存器,形成一个表,这一步骤就完成了。同时软硬件接口就定下来了。

2.2 芯片物理接口

上面说的软硬件接口其实是一个比较抽象的概念,把寄存器当做软硬件交流信息的媒介。这个地方介绍的接口属于物理接口,和外界的物理接口显然要好用。有了软硬件接口,设计需求以后芯片与外部的PAD基本就可以确定下来了,顶多后期可能会做一些小修小补。次出先把接口确定下来,方便后续PCB,测试方案等可以提前做起来。

2.3 硬件功能描述

有了芯片的软硬家划分和接口,芯片内部具体要实现什么功能在这个地方就能定下来。分门别类的将商业需求逐条翻译为硬件可实现的设计需求。这个地方可能就面临着第一次需求的变更。有可能某个需求硬件实在是不好实现,或者实现起来代价非常大。这个时候需要和产品的人拉扯一下,看看能不能简化需求,或者不做需求。总之,这一步以后会输出经过产品与设计认可的详细的芯片实现的功能表,后续设计人员直接按照这个表实现芯片。

这个步骤和2.2其实有点类似,属于对应的东西。特别是对于时延有较高要求的系统,比如通信系统等等,硬件性能要逐条列出来。举个简单的例子,处理224x224分辨率,使用3x3核心的Alexnet卷积网络需要1ms。总是就是把性能写清楚,避免设计人员出现误解。当然也有可能硬件功能描述和硬件性能描述的人员都是同一批设计人员,这样子的情况下仍然建议把这个描述写清楚,方便产品的小伙伴check一下是不是有问题。

至此,spec的确定大体上就结束了,写起来感觉几千字就写完了,但是实际上花的时间不少,相互拉扯也不少。此处spec的输入是市场提供的原始需求,我们把它拆解成设计需求。有时候这个地方spec确认也有营销人员的参与。比如某个特性,可能实际没什么用,但是就是能刷某个指标,对后期宣传或者拿到投资非常重要,营销人员希望把这个特性加入进去,这时候产品或者技术人员可能不愿意做,总觉得有点浪费时间和生命,又是无数个加班的夜,就为了整这些虚头巴脑的东西,有点想不通。但是其实有时候想想,从大局观上来讲,如果能做进去还是做进去吧,做市场的或者拉融资的也有自己的难处,也许短期目标不一致,但长期目标是一致的,芯片有噱头,能PK掉竞争对手,能卖出去或者能拉到投资,做技术的一帮人才能有资金一稿一稿实现心中的美好。

扯远了,接下来就开始确定计划了。

3 确定计划

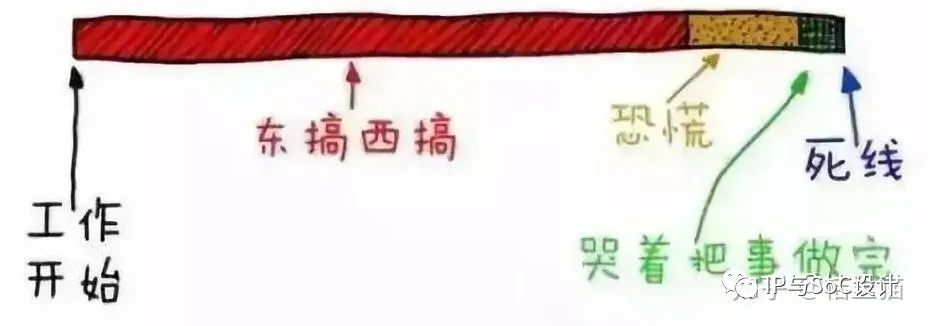

我们首先来回答一个问题,为什么要确定计划?我们用下面这个图来解释一下。这个图是当时写文章的时候最喜欢的一张图,生动形象又深以为戒。

即使有严密的deadline, 仍然在流片前不免赶工,不用说计划做不好实际会出现什么情况。

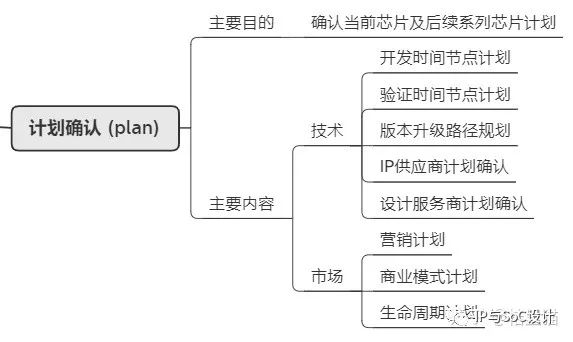

计划确认大约有这么些个流程,实际上应该更复杂,如果有什么缺的欢迎大家交流。主要目的就是确认当前芯片及后续系列芯片的计划。主要内容包含技术的计划与市场的计划两个方向。

3.1 技术计划

开发时间节点计划这个是最传统意义上的计划。芯片这种东西开发时间都很长,市场不可能无限的等,所以明确的时间节点计划是比较重要的。这个计划要标明各个节点的时间。RTL代码完成50%, 完成90%,完成100%(这个不同公司叫法不一样,比如有些公司多10%这个结点,还有公司叫85%,95%什么的,都指的一个意思,不要在意细节),DC完成, 验证完成,后端完成,TO时间。每个时间点都要明确,而且尽量不要让前端拖时间,因为TO的时间是确定的,意味着后端时间无法再拖,前端拖太久时间会导致后端时间不大够。这个时间节点不同公司应该要求的不一样,比如NVNIDA的卡,大约两年出一代新的,各个时间节点就要按照这个节奏来。比如高通或者苹果,一年出一代,也同样按照节奏来。

验证时间节点计划 验证计划要稍微比测试计划晚一点。但是还是有各种时间和策略需要在计划阶段就确定。EDA验证的时候设计几个UT, 几个IT。测试时间点是什么,UTITST各个时间节点是什么,要不要用FPGA验证,要不要用emulator验证等等。做验证的同事们应该非常专业,欢迎大家补充一下这块内容。

版本升级路径规划 这个也是一个比较重要内容。由于硬件设计的成本是巨大的,所以在设计开始前就要大致想好往后的道路,便于在一套架构上裁剪。比如intel就采用一种叫tick-tock的战略,一年演化架构,一年演化工艺。但是intel每年都会出新的芯片,这个时候做架构的时候考虑版本升级就非常重要。一般来讲,无非两种办法,可以做一个性能很强的平台架构,第一年裁剪一下,第二年放全量。第二种办法是做一个稍弱的版本,第二年扩充一下规格。intel采用哪个不得而知,但是无论采用哪个方式,在版本规划的时候就要明确以下一到N个版本的扩展计划。否则设计人员不清楚的话将RTL设计成不可扩展的结构往后版本升级就很被动。

IP供应商计划确认 这个部分主要是涉及到一些购买的IP,需要提前和各厂商确定好价格,功能是否都可以接受。一般包括数字IP和模拟IP。数字IP一般集成比较简单,例如AMBA总线, RISC-V Core等等,厂商会提供网表甚至源代码,直接继承就行。模拟IP就比较复杂,包括AD, DA ,PLL, DDR PHY, USB PHY等等一堆IP,一般是提供版图,有些甚至版图都不提供,由它们自己人merge版图的。所以每一个都要仔细评估,成熟度如何,好不好集成,会不会出问题。

设计服务商计划确认 这个最主要是要确认两拨人的时间有没有空。如果后端外包了的话要确认后端设计公司是否有足够的人力接单,提前约时间,避免前端最后了等着后端的尴尬。另一批人是代工厂。除非你是苹果这样的甲方爸爸,TSMC可以就着你的时间来,其他人的流片计划都要看看TSMC的计划。特别是投MPW的样片,要时刻注意代工厂的计划。他们自己形象的把这种计划叫做班车。。。你的项目能不能赶上班车是非常重要的事儿。否则轻则两周,重则上月的delay。

3.2 市场计划

市场计划原则上应该是和技术计划并行的。实际上可能会比技术计划要晚上不少。此处就列在这个地方统一说了。市场计划大致上有三方面内容。这个做市场的同学玩的溜,让做技术的来写确实有点勉为其难了,只能抛个砖头。

营销计划 这个主要是对芯片怎么卖出去做一定的计划。目标市场是什么样的,细分市场是哪个,细分市场以及市场的客户有什么痛点,愿意付多少钱,有没有市场机会,到时候市场占有率是什么情况。这个芯片的基础客户基本盘是谁,还能卖给谁。还要关注一下竞争对手,竞品分析,竞争对手什么特点,如何和竞争对手抢市场。等等这些与把芯片卖出去的问题。

商业模式计划 芯片做出来怎么赚到钱。这个主要涉及两方面内容,一个是定价销售策略。是贴牌卖了,还是自己卖,还是打包送了,或者送一部分,等客户赚到钱后再提成,或者芯片低价卖,交个朋友,主要卖配件,有不同的操作方式。只要财务和市场能算明白帐,有钱赚即可。第二个是市场准入策略。比如wifi芯片等等,这些芯片要拿到市场上卖是要符合一定的标准的,怎么拿到许可证,许可好不好拿,也要提前想清楚。

生命周期计划 除非非常经典的基础芯片,比如TI的一堆ADC,其他芯片总要有个生命周期。这个生命周期的计划会影响架构设计时的可扩展性,影响下一代芯片的演进等等。实际上,芯片大致有三个阶段,和其他东西一样。停止销售,停止生产,以及停止售后。和苹果IPAD其实类似,前不久还宣布几个IPAD是过时产品。。所以生命支持周期要把握好度。停止销售和停止生产好理解,芯片已经在市场上没有竞争力了。停止售后决策比较麻烦,太长了费钱不划算,太短了用户那儿没有口碑。不能客户的产品刚用一两年你就不支持了,总归不大好。

4 总结

至此,规格和计划阶段的事情基本上就搞清楚了。这个阶段我们的输入是立项时的商业需求,输出是由设计人员分解的设计需求,以及各类计划。

审核编辑 :李倩

-

寄存器

+关注

关注

31文章

5357浏览量

120665 -

芯片设计

+关注

关注

15文章

1023浏览量

54933

原文标题:一颗芯片的前世今生:概念计划

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用一颗5G的204B接口DA芯片,DA芯片的输入时钟大小和输入数据的速率是怎么样的关系?

深入了解Java泛型——从前世今生到PECS原则

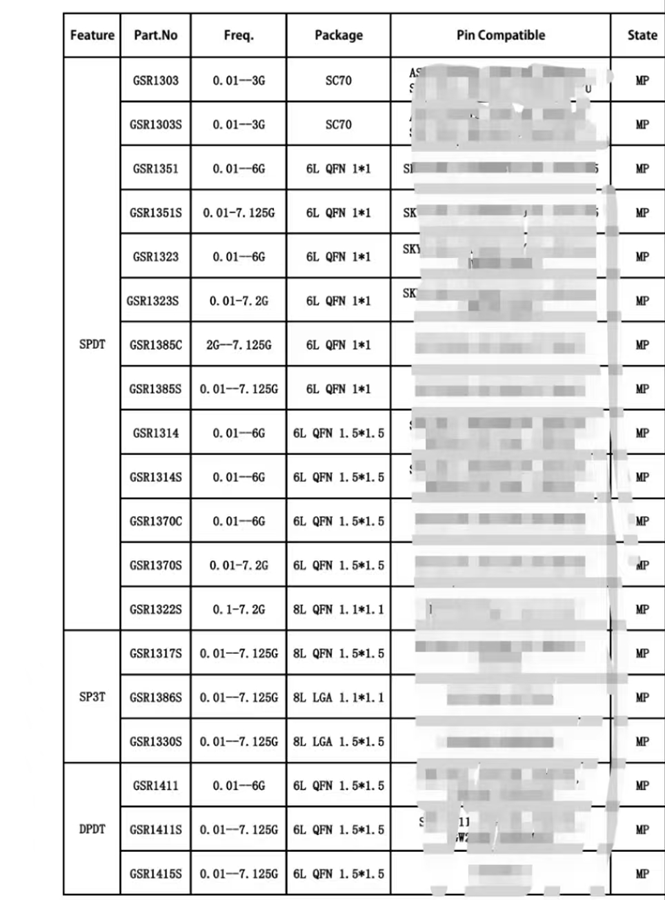

一颗射频开关的独白

两颗TAS5711,一颗作2.0输出,一颗作PBTL输出,共用一个I2S_DATA时发现失真增大,为什么?

OPA197如果使用多阶,用一颗跟随器提供基准电压是否可行?

NASA:在十年内将一颗模仿恒星的微小卫星发射到太空

HT7017 是一颗带 UART 通讯接口的高精度单相多功能计量芯片

一颗改变了世界的芯片

一颗芯片的前世今生:概念计划

一颗芯片的前世今生:概念计划

评论