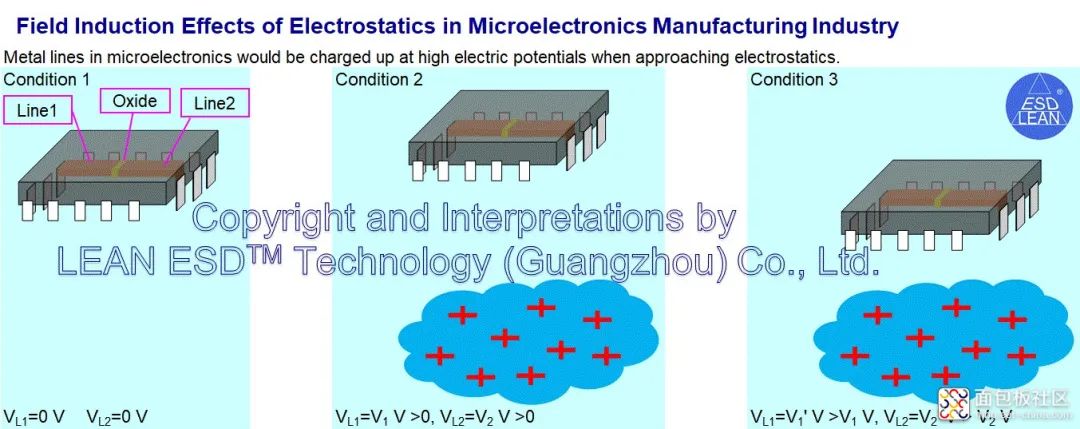

微电子制造中的静电问题都是存在于众多微小的细节之中。 微电子制造中存在大量的生产工序会产生并累积静电。 静电的直接影响之一就是通过静电感应作用将临近的微电子器件(确切而言,是其中的大量金属线路)充电至高静电位。

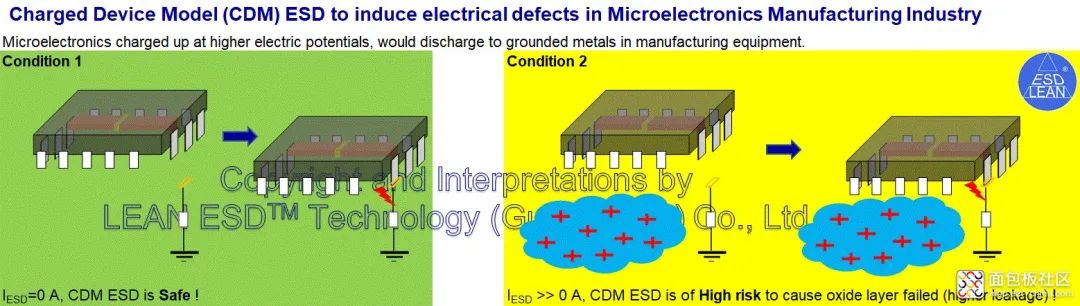

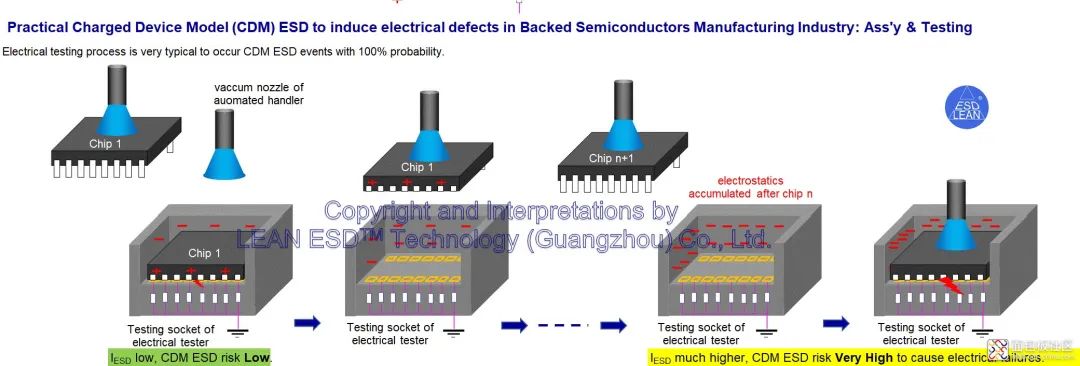

而微电子制造中涉及的许多电气测试机台(IC封测工厂就含有大量的电测工序),就是典型的CDM(Charged Device Model,器件带电放电模型) ESD关键工序(100%会发生CDM ESD),由此导致微电子器件的电性不良风险(主要是器件中的绝缘膜层漏电流过大,如gate oxide)必须得到重视并采取有效的管控措施;

而电气测试机台中的testing socket(测试插座)尤其是其中的器件装载导引机构大都采用绝缘塑胶或陶瓷材质,每颗器件的测试过程都会发生器件封装体与testing socket导引机构件之间的摩擦静电起电,随着测试机台测试越来越多的器件,如果testing socket上累积的静电得不到及时的有效消除,越到后面测试的器件发生CDM ESD导致的电气失效不良风险就越高。

当前基于28nm制程及以下的IC已经占比将近50%,其最高承受的CDM ESD电压大部分不超过100V。其中,最新的7nm、5nm制程的5G IC,CDM耐压更是降至50V以下,这种IC的设计与制程变化,给集成电路前段制造-Wafer Fab、集成电路后段制造-封装与测试、以及SMT工厂的生产工艺中的ESD防护带来了非常大的挑战。

审核编辑 :李倩

-

ESD

+关注

关注

49文章

2036浏览量

173084 -

静电

+关注

关注

1文章

507浏览量

36402 -

微电子

+关注

关注

18文章

382浏览量

41211

原文标题:现实中微电子制造领域的静电问题[20230111]

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

求问帖!静电消除器在电子半导体领域的具体应用与需求!

静电对敏感电子元件的影响

静电对电子设备的影响

微电子制造中的FIB-SEM双束系统:技术应用与进展

方正微电子:2025年将实现16.8万片/年车规SiC MOS产能

长电微电子晶圆级微系统集成高端制造项目即将投产

虚拟现实技术的应用领域有哪些

深圳比创达电子EMC|人体静电对精密电子器件的伤害如何避免.

微电子领域技术趋势(2024)

美国启动“微电子战略”,力推国内半导体制造

宙讯微电子正式对外发布压电MEMS代工平台

现实中微电子制造领域的静电问题

现实中微电子制造领域的静电问题

评论