DS1624的2线时序规格与I²C不同。本应用笔记详细介绍了其中的区别。SDA不由DS1624内部保持。总线主站有责任保持SDA,直到SCL的下降沿完成。

介绍

本应用笔记详细介绍了DS1624通信时序与I²C规格之间的差异。在I²C下,允许SCL和SDA线路同时转换,因为SDA被从器件在内部延迟至少300ns。DS1624不会延迟相对于SCL的SDA信号,因此总线主机必须将SDA保持在正确的逻辑状态,直到SCL完全转换到逻辑低电平,以防止错误生成START或STOP操作。

适当的时机

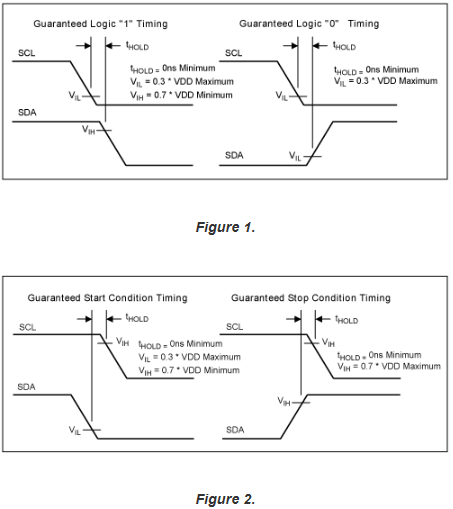

DS1624的SDA线相对于SCL没有内部延迟。因此,SDA逻辑电平必须保持在DS1624外部,直到写入数据时SCL转换到逻辑低电平;否则,可能会识别启动或停止条件。在2线总线上写入逻辑“1”时,SCL必须达到保证逻辑低阈值V伊利诺伊州(0.3 x VDD 最大值),SDA 转换到保证逻辑高阈值 V 以下之前IH(最小 0.7 x VDD)。写入逻辑“0”时,SCL 必须达到 V伊利诺伊州在 SDA 转换到 V 以上之前伊利诺伊州.生成启动条件时,SDA 必须达到 V伊利诺伊州在 SCL 过渡到 V 以下之前IH.生成停止条件时,SDA 必须达到 VIH在 SCL 过渡到 V 以下之前IH.两个 V伊利诺伊州和 VIH关卡在每个设备上都经过生产测试。这保证了在整个电压和温度范围内(包括器件制造公差)使用此时序的正常运行。

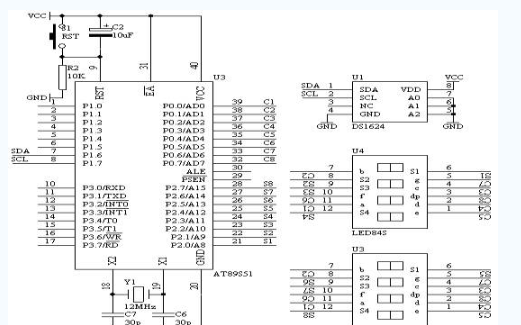

图1.

图2.

总结

DS1624的时序和I²C规格存在差异。DS1624不会在内部延迟SDA相对于SCL。因此,系统主机需要在 SCL 的下降沿期间维护 SDA,以防止逻辑“1”被解释为 START 条件,而逻辑“0”被解释为 STOP 条件。

审核编辑:郭婷

-

总线

+关注

关注

10文章

2878浏览量

88051 -

时序

+关注

关注

5文章

387浏览量

37318 -

SCL

+关注

关注

1文章

239浏览量

17057 -

Start

+关注

关注

0文章

73浏览量

10281

发布评论请先 登录

相关推荐

带有存储器功能的数字温度计-DS1624技术应用

请问大神我的ds1624程序芯片为什么不行

基于数字温度计和256字节的E2存储器组成的DS1624

DS1624 pdf datasheet (digital

带有存储器功能的数字温度计-DS1624技术应用

美信推出DS1624数字温度计

DS1624数字温度计的资料简介和应用源代码概述

DS1624+ DS1624+ - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

DS1624 DS1624 - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

DS1624S DS1624S - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

DS1624通信时序与I²C规格之间的差异

DS1624通信时序与I²C规格之间的差异

评论