本文主要介绍DRAM的存储原理、存储电容、存储结构等内容,后续会针对SDRAM和DDR等具体类型进行详细介绍。

1、概述

DRAM包括:SDRAM、DDRx、SDR、LPDDRx、LPSDR、GDDR、RLDRAMx(Reduced Latency DRAM)、EDO DRAM、FPM DRAM、Mobile DRAM等等。

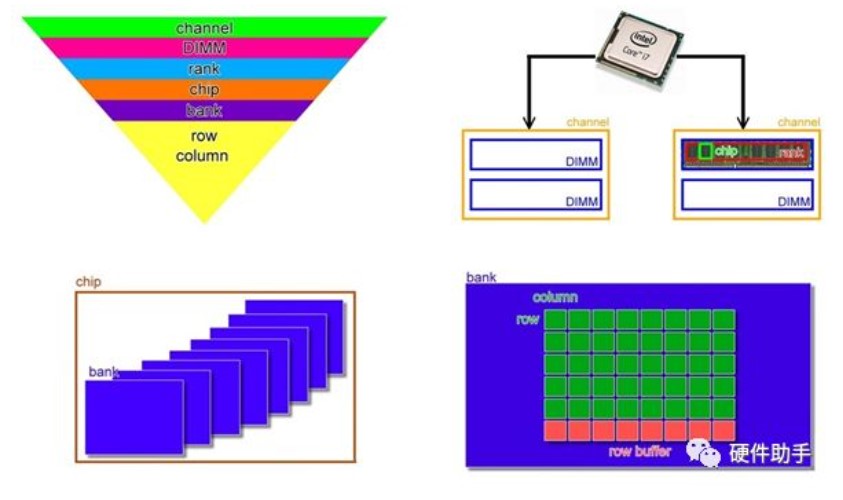

主存DRAM由大至小,由上往下可做以下拆分:channel→DIMM→rank→chip→bank→row/column。

2、DRAM存储原理

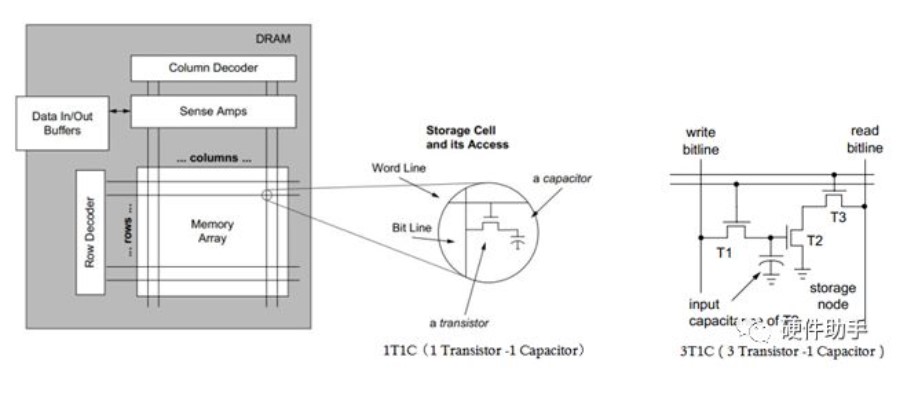

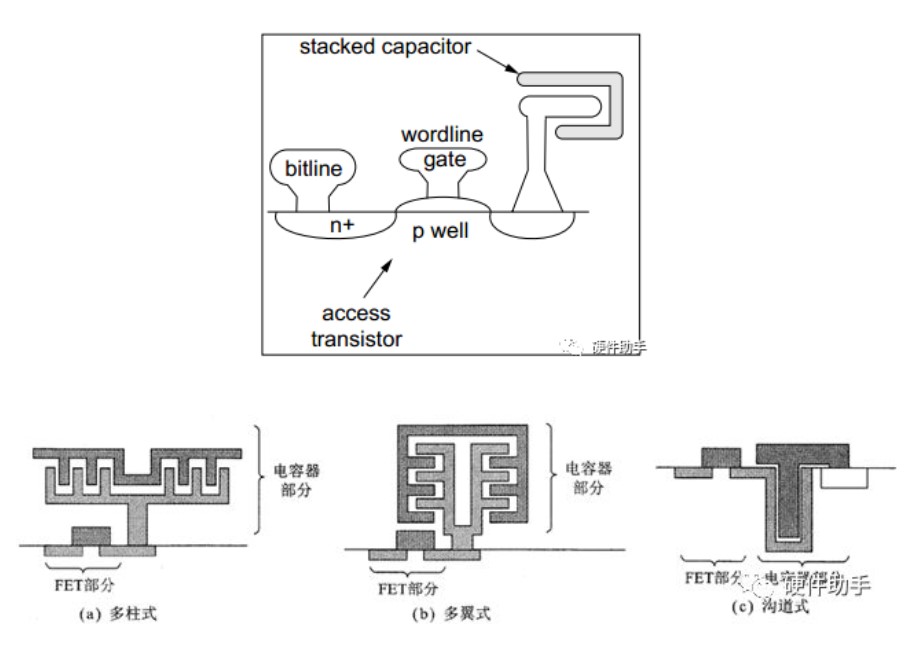

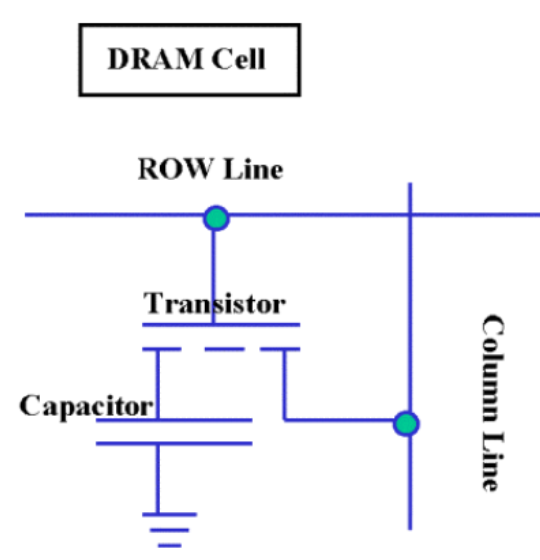

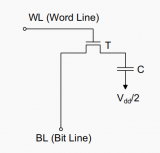

DRAM的结构大致分为两种:1T1C和3T1C,详见下图。

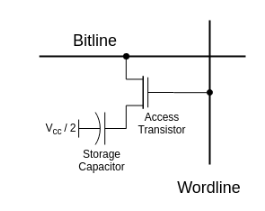

1T1C(1 Transistor -1 Capacitor)的大致原理是:当Word Line选通时,晶体管导通,从而可以从Bit Line上读取存储在电容上的位信息。

3T1C(3 Transistor -1 Capacitor)使用三个晶体管作为开关,这样设计的优点是:当读取存储在电容上的位信息时,不会影响电容上的电荷,从而读后不需要对单元进行precharge。但是由于1T1C的结构比3T1C的结构面积节省很多,因此现代DRAM中常用的还是1T1C结构。

DRAM的信息是存储在电容当中的,而电容中的电荷会因为漏电流的存在而逐渐漏掉,因此需要不断refresh(刷新),这也是DRAM称为动态的原因。例如,90nm工艺下,DRAM的cell单元的电容量是30pF,它的漏电流是1fA,漏光的时间是随着温度的变化而变化的。现在的DRAM的刷新时间一般是32ms或者64ms。

3、DRAM存储电容

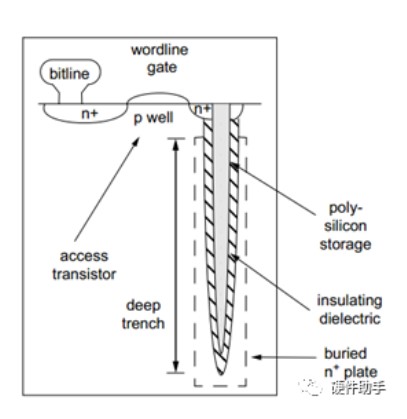

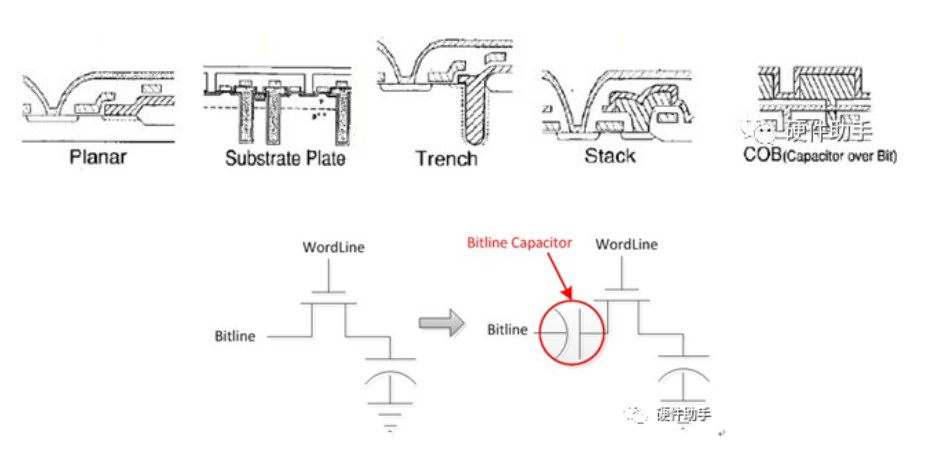

关于存储电容在现代业界也没有统一,存在两大阵营,分别是堆电容(Stacked Capacitor)与沟电容(Trench Capacitor),像三星这样的公司使用前者。因为这两种电容在任何DRAM中都是存在的而且是需要考虑到的。trench电容是存在于深入到硅下面的,而stacked电容是存在于不同的多晶硅层中间。这两种电容分别有自己的优缺点:

trench电容是深入到硅下面的,相当于从二维到三维的拓展,可以保证在相同的电荷容量下,面积小,成本低,由于其表面平坦更易制造,使它更易集成到逻辑优化工艺技术里。由于深入到硅下面的,在上层的逻辑电路结构形成之前就存在,与上层电路无关,有利于电路优化。

堆电容是在硅表面形成像高层建筑那样的结构,可以有效地利用芯片面积,但工艺复杂,成本较高。关于stacked电容,由于是存在不同的多晶硅层之间的,因此bitline与多晶硅之间也会存在电容,且这种电容属于stacked电容。

沟电容(Trench Capacitor)的示意如下图所示:

堆电容(Stacked Capacitor)的示意如下图所示:

平面型、衬底基板深槽型、深槽型、堆叠型、电容器在位线上方堆叠型的具体示意如下图所示:

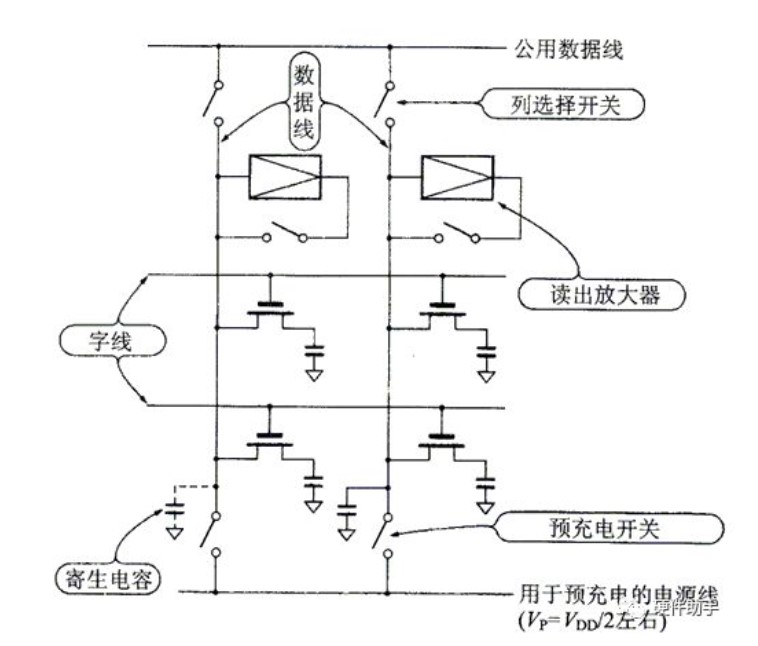

由于每个Bitline上连着很多并联的Bitline Capacitor,因此存储电容大小远比Bitline电容小,大约只有1/10。所以当transistor选通时,存储在存储电容上的电荷传输到Bitline时,Bitline上的电压变化很小,需要使用差分比较放大器(此差分比较放大器非模拟集成电路中的差放,而是通过跟参考电压作对比)。

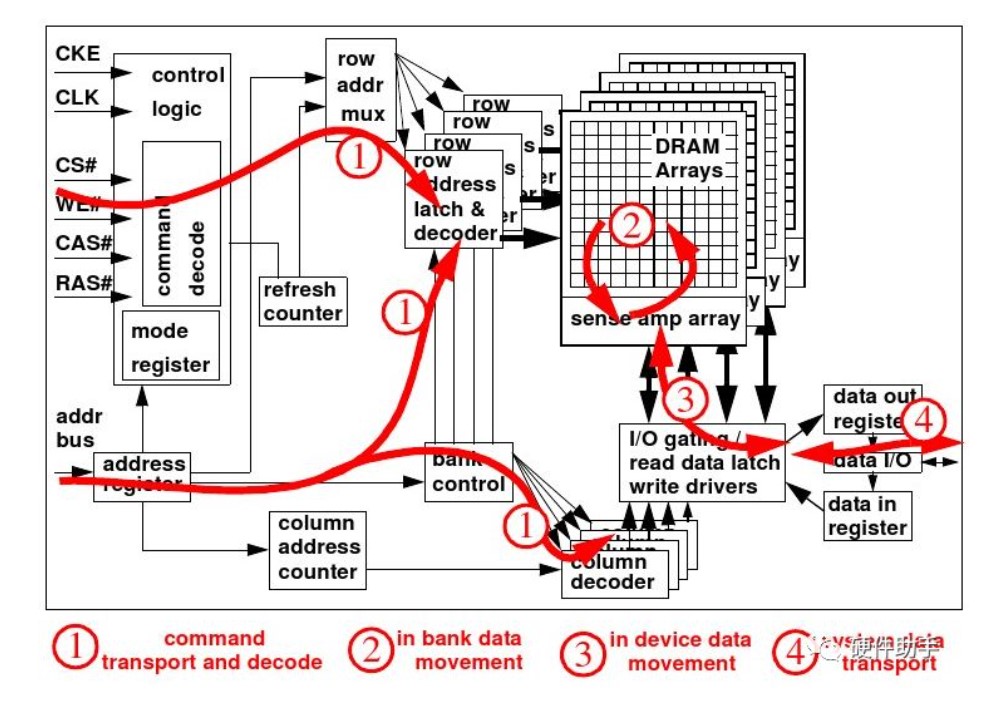

DRAM的行选通和列选通信号将使存储电容与外界间的传输电路导通,从而可进行放电(读取)和充电(写入)。

在高密度的DRAM中,存储器的单元电容决定了读出信号电压、读出速度、数据保持时间和抗软错误容限。每一个存储单元堆电容或沟电容容量为fF级(一般认为必须大于25fF)。增加单元电容的一个主要策略是增加存储器单元电容器的面积和降低介质薄膜厚度(单位为F:FeatureLength,F2:Feature Dimension)。

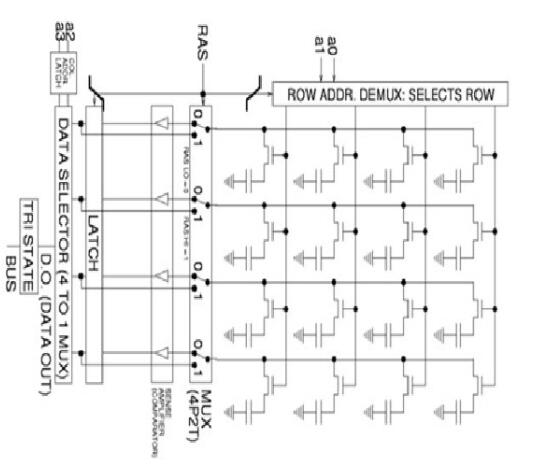

DRAM内部结构如下图所示:

4、L-Bank&P-Bank

4.1、逻辑BANK

在芯片的内部,DRAM的数据是以bit为单位写入一张大的矩阵中,每个单元我们称为CELL,只要指定一个行(Row),再指定一个列(Column),就可以准确地定位到某个CELL,这就是内存芯片寻址的基本原理。这个阵列我们就称为内存芯片的BANK,也称之为逻辑BANK(Logical BANK)。由于工艺上的原因,这个阵列不可能做得太大,所以一般内存芯片中都是将内存容量分成几个阵列来制造,也就是说内存芯片中存在多个逻辑BANK,随着芯片容量的不断增加,逻辑BANK数量也在不断增加,目前从32MB到1GB的芯片基本都是4个,只有早期的16Mbit和32Mbit的芯片采用的还是2个逻辑BANK的设计,譬如三星的两种16MB芯片:K4S161622D(512K×16Bit×2 BANK)和K4S160822DT(1M×8bit×2 BANK)。芯片组本身设计时在一个时钟周期内只允许对一个逻辑BANK进行操作(实际上芯片的位宽就是逻辑BANK的位宽),而不是芯片组对内存芯片内所有逻辑BANK同时操作。逻辑BANK的地址线是通用的,只要再有一个逻辑BANK编号加以区别就可以了(BANK0到BANK3)。但是这个芯片的位宽决定了一次能从芯片内部读出多少数据,并不是内存芯片里所有单元的数据一次全部能够读出。

每个逻辑BANK有8M个单元格(CELL),一些厂商(比如现代/三星)就把每个逻辑BANK的单元格数称为数据深度(Data Depth),每个单元由8bit组成,那么一个逻辑BANK的总容量就是64Mbit(8M×8bit),4个逻辑BANK就是256Mbit,因此这颗芯片的总容量就是256Mbit(32MB)。

内存芯片的容量是一般以bit为单位的。可以根据芯片上的标识知道,这个芯片有几个逻辑BANK,每个逻辑bank的位宽是多少,每个逻辑BANK内有多少单元格(CELL),比如64MB和128MB内存条常用的64Mbit的芯片就有如下三种结构形式:

16M×4bit=4M×4bit×4banks

8M×8bit=2M×8bit×4banks

4M×16bit=1M×16bit×4banks

存储单元数量=行数×列数(一个L-Bank的存储单元数量)×L-Bank的数量。芯片逻辑BANK位宽目前的工艺水平只能最多做到16位,因此大家看到几乎所有的芯片逻辑BANK位宽只可能4/8/16三者之一。以前16Mbit的芯片基本采用的单个芯片两个逻辑BANK,但是到了64Mbit基本就都是4个逻辑BANK设计了。

4.2、物理BANK

内存系统为了保证CPU正常工作,必须一次传输完CPU在一个传输周期内所需要的数据,而CPU在一个传输周期能接收的数据容量就是CPU数据总线的位宽,这个位宽就称为物理BANK的位宽。

本文主要介绍DRAM的存储原理、存储电容、存储结构等内容。后续会针对SDRAM和DDR等具体类型进行详细介绍。

审核编辑:刘清

-

DRAM

+关注

关注

40文章

2325浏览量

183834 -

逻辑电路

+关注

关注

13文章

494浏览量

42696 -

GDDR

+关注

关注

0文章

27浏览量

4687

原文标题:MEMORY系列之“DRAM概述”

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DRAM设计原理:DRAM Storage Cell 的结构分析

浅析DRAM和Nand flash

DRAM与NAND概述及差别

易失性存储DRAM是什么,它的主要原理是怎样的

DRAM存储电容概述

DRAM存储电容概述

评论