同步设计和异步设计的特点

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。

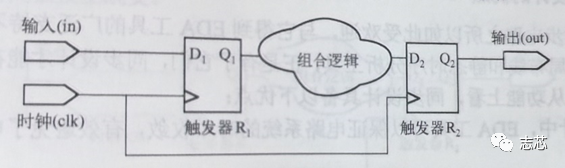

同步电路特点:时钟个数只有一个,电路中触发器的时钟输入端连接同一个时钟脉冲源,所有触发器的状态变化都与所加的时钟脉冲信号同步;由于只有一个时钟,所以整个电路所有时钟应该是同源同相的;一般会滤掉毛刺,不需要特别考虑竞争与冒险;有利于静态时序分析;设计的电路具有强耦合关系,不利于面积优化与低功耗优化,不灵活;存在时钟偏斜问题。

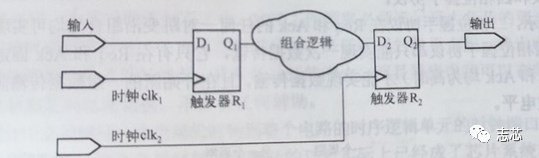

异步电路特点:电路中没有统一的时钟(可以有多个时钟),有些触发器的时钟输入端与时钟脉冲源相连(与时钟脉冲源同步),其余触发器状态变化不与时钟脉冲源同步;由于有多个时钟,因此有些时钟是同源不同相的,有些是不同源的;很大概率存在竞争与冒险;一般无法对异步电路进行静态时序分析;电路耦合关系很弱,设计比较灵活,相同条件下比同步电路功耗低;不存在时钟偏斜问题。

做模块划分时应该考虑哪些问题

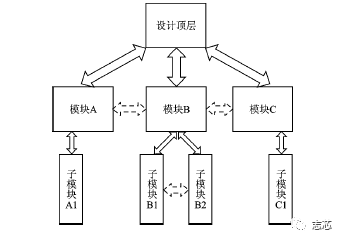

结构层次化是设计的一种基本思想,需要注意:结构不宜太深,否则综合时面积过大,综合工具会默认做扁平化处理;顶层设置不宜过于复杂,主要完成诸如输入输出,模块调用与实例化,全局时钟,三态总线,全局复位等等简单的功能;双向的信号最好只在顶层出现;子模块之间最好不要有跨层次的接口;合理考虑子模块的功能、结构、时序等。

模块划分的技巧:对每个同步时序设计的子模块的输出使用寄存器处理;将相关的逻辑或者可以复用的逻辑写在一起;将不同优化目标的部分分开,时序的和面积的分开处理;将时序宽松的分到同一个模块;将存储器件独立划分;合理规划模块的规模。

图1模块划分示意图

组合逻辑设计有哪些考虑点

根据逻辑功能的不同特点,可以将数字电路分成两大类,一类称为组合逻辑电路(简称组合电路),另一类称为时序逻辑电路(简称时序电路)。

常见组合逻辑电路包括编码器、译码器、数据选择器、数值比较器、加法器、函数发生器、奇偶校验器/发生器等。

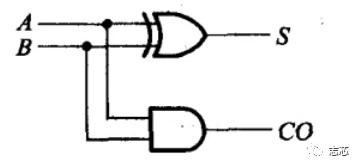

图2组合逻辑之半加器

组合逻辑设计注意事项包括:避免组合逻辑反馈环路(容易毛刺、振荡、时序违规等);替换延迟链,用倍频、分频或者同步计数器完成;替换异步脉冲产生单元(毛刺生成器),用同步时序设计脉冲电路;慎用锁存器,锁存器容易产生毛刺。

RTL代码优化有哪些技巧

Pipelining,即流水线时序优化方法,其本质是调整一个较长的组合逻辑路径中的寄存器位置,用寄存器合理分割该组合逻辑路径,从而降低了对路径的Clock-To-Output和Setup等时间参数的要求,达到提高设计频率的目的。但是必须要注意的是,使用Pipelining优化技术只能合理地调整寄存器位置。

模块复用与Resource Sharing,Sharing模块复用和Resource Sharing是一种节约面积的思想,在设计电路中,在不影响性能的情况下,实现最少的逻辑资源开销。

逻辑复制是一种通过增加面积而改善时序条件的优化手段。逻辑复制最常使用的场合是调整信号的扇出。如果某个信号需要驱动后级的很多单元,换句话说,也就是其扇出非常大,那么为了增加这个信号的驱动能力,必须插入很多级Buffer,这样就在一定程度上增加了这个信号路径的延时。这时可以复制生成这个信号的逻辑,使多路同频同相的信号驱动后续电路,平均到每路的扇出变低,不需要加Buffer也能满足驱动能力的要求,这样就节约了该信号的路径时延。

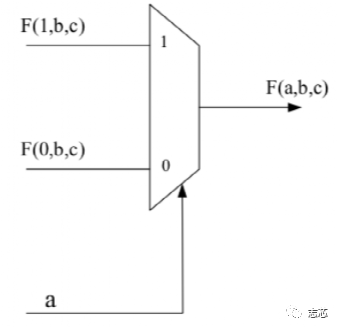

香农扩展(Shannon Expansion)也是一种逻辑复制、增加面积、提高频率的时序优化手段。香农扩展通过逻辑复制、增加MUX(多路选择器)来缩短某个优先级高但组合路径长的信号的路径延时(信号a),从而提高该关键路径的工作频率,以增加面积换取电路时序性能的优化。其扩展运算公式为:Fa,b,c=aF1,b,c+aF(0,b,c)。

END

审核编辑 :李倩

-

编码

+关注

关注

6文章

957浏览量

54940 -

RTL

+关注

关注

1文章

385浏览量

59931 -

同步电路

+关注

关注

1文章

60浏览量

13338

原文标题:RTL设计编码原则

文章出处:【微信号:IC学习,微信公众号:IC学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

编码器类型详解:探索不同编码技术的奥秘

磁电编码器和光电编码器的区别

差动保护动作电流整定原则

RTL8187L和802.11n

RTL8201F 10兆可以连接,100兆无法连接是什么问题

基于树莓派5的RTL仿真体验

如何通过优化RTL减少功耗

编码器如何选择合适的脉冲数

RTL设计编码原则

RTL设计编码原则

评论