1. 斜体和粗体

使用 * 和 ** 表示斜体和粗体。

示例:

这是 斜体 ,这是 粗体 。

2. 分级标题

使用 === 表示一级标题,使用 --- 表示二级标题。

示例:

这是一个一级标题

============================

这是一个二级标题

--------------------------------------------------

### 这是一个三级标题

你也可以选择在行首加井号表示不同级别的标题 (H1-H6),例如:# H1, ## H2, ### H3,#### H4。

3. 外链接

使用 描述 为文字增加外链接。

示例:

这是去往 本人帐号 的链接。

4. 无序列表

使用 *,+,- 表示无序列表。

示例:

- 无序列表项 一

- 无序列表项 二

- 无序列表项 三

5. 有序列表

使用数字和点表示有序列表。

示例:

- 有序列表项 一

- 有序列表项 二

- 有序列表项 三

6. 文字引用

使用 > 表示文字引用。

示例:

野火烧不尽,春风吹又生。

7. 行内代码块

使用 代码 表示行内代码块。

示例:

让我们聊聊 html。

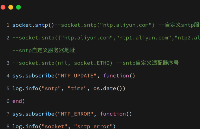

8. 代码块

使用 四个缩进空格 表示代码块。

示例:

这是一个代码块,此行左侧有四个不可见的空格。

9. 插入图像

使用 !\\[描述](图片链接地址) 插入图像。

10.空白行

(1)html换行标签:

在任意的位置输入即可以实现换行效果。

<br/>

(2)使用nbsp:

只有在空白行才能换行,否则只能作为一个空格。

更多MarkDown语法请参见 :

学习更多编程知识,请关注我的公众号:

[代码的路]

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

编程

+关注

关注

88文章

3616浏览量

93763 -

代码

+关注

关注

30文章

4790浏览量

68654 -

语法

+关注

关注

0文章

44浏览量

9827 -

MarkDown

+关注

关注

0文章

46浏览量

275

发布评论请先 登录

相关推荐

Verilog硬件描述语言参考手册

一. 关于 IEEE 1364 标准二. Verilog简介三. 语法总结四. 编写Verilog HDL源代码的标准五. 设计流程

发表于 11-04 10:12

•0次下载

Lua语法基础教程(下篇)

今天我们继续学习Lua语法基础教程,下篇。 九、函数 9.1 初识函数 函数是指一段在一起的、可以做某一件事儿的程序,也叫做子程序。 在前面的内容中,我们已经接触过了函数的调用,这个函数就是前面用到

Lua语法基础教程(中篇)

今天我们继续学习Lua语法基础教程,中篇。 五、变量 5.1 number变量 变量,可以看作是一个桶,在里面装你想要装的内容。这些内容可以是Lua包含的所有合法类型。 例如:我想要新建一个桶,名叫

Lua语法基础教程(上篇)

今天我们来学习Lua语法基础教程。由于篇幅过长,将分为上中下三篇进行讲解,本篇为上篇。 一、初识Lua Lua 是一种轻量小巧的脚本语言,它用标准C语言编写并以源代码形式开放。这意味着什么呢?这

《DNK210使用指南 -CanMV版 V1.0》第七章 基于CanMV的MicroPython语法开发环境搭建

第七章 基于CanMV的MicroPython语法开发环境搭建 前面章节中已经介绍了如何编译CanMV固件,并将编译好的CanMV固件烧录至Kendryte K210,本章将介绍如何在Windows

发表于 09-13 09:30

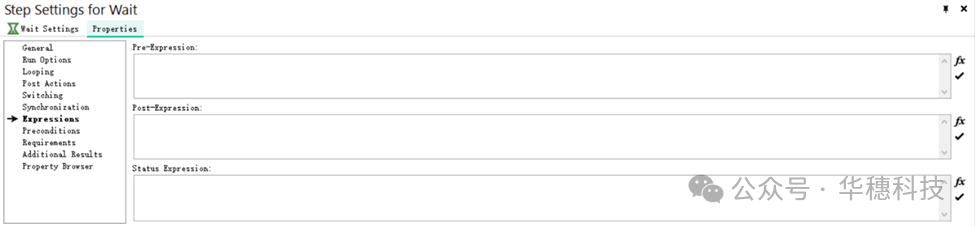

TestStand表达式中常用的语法规则和运算符使用

TestStand也有自己的语言嘛?在回答这个问题之前大家可以想一下在使用TestStand时有一个和语言密切相关的属性。没错那就是表达式(Expressions),在这篇文章中,小编将以Q&A的方式来带着大家来理解并熟悉TestStand表达式中较为常用的一些语法规则以及运算符使用。

鸿蒙原生应用元服务开发-初识仓颉开发语言

仓颉编程语言是一种面向全场景应用开发的通用编程语言,可以兼顾开发效率和运行性能,并提供良好的编程体验,主要具有如下特点:

语法简明高效 :仓颉编程语言提供了一系列简明高效的语法,旨在减

发表于 08-15 10:00

鸿蒙原生应用元服务开发-初识仓颉开发语言

仓颉编程语言是一种面向全场景应用开发的通用编程语言,可以兼顾开发效率和运行性能,并提供良好的编程体验,主要具有如下特点:

语法简明高效 :仓颉编程语言提供了一系列简明高效的语法,旨在减

发表于 07-30 17:49

HarmonyOS Next 原生应用开发-ArkTS语法适配背景说明

ArkTS在保持TypeScript(简称TS)基本语法风格的基础上,进一步通过规范强化静态检查和分析,使得在程序开发期能检测更多错误,提升程序稳定性,并实现更好的运行性能。本文将进一步解释为

发表于 07-01 16:49

FPGA学习笔记---基本语法

Verilog语法是指硬件能够实现的语法。它的子集很小。常用的RTL语法结构如下:

1、模块声明:module ... end module

2、端口声明:input, output, inout

发表于 06-23 14:58

MarkDown简明语法手册

MarkDown简明语法手册

评论