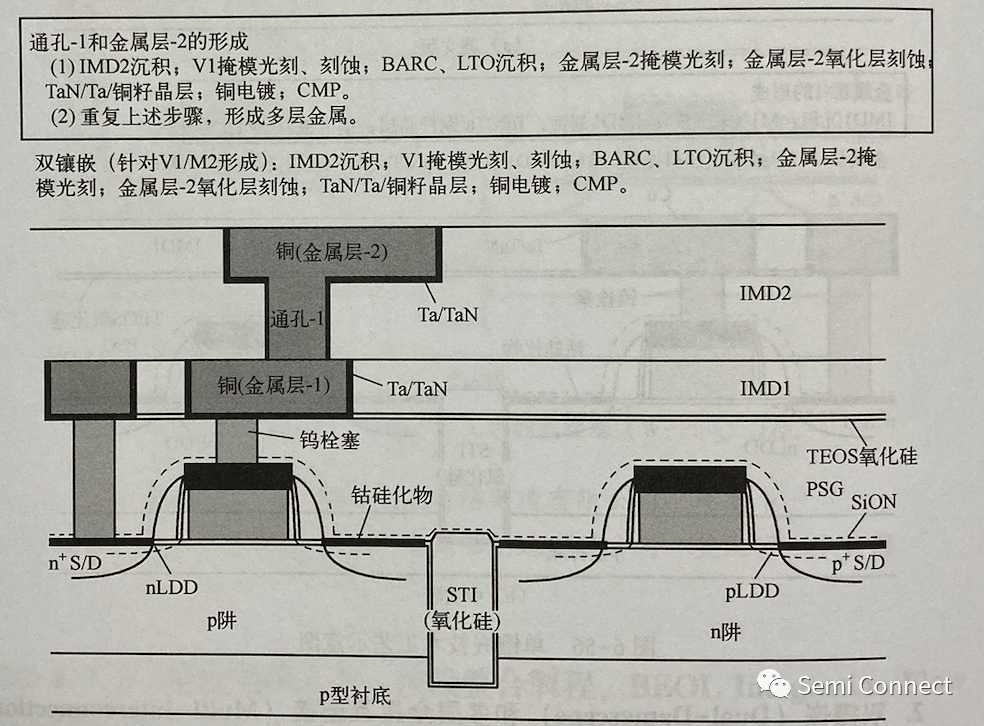

双镶嵌 (Dual-Damascene)和多层金属互连接 (Multi-Interconnection)通孔-1(V1)和金属-2 (M2)互连的形成是通过双镶嵌 (Dual -Damascene)工艺实现的,如图所示。

双镶嵌工艺分为先通孔 (Via-First) 和先沟槽(Trench-First)两种技术。以先通孔技术为例,首先沉积IMD2层(如 SiCN层,厚度约为 50nm,含碳低kPECVD 氧化硅黑金刚石层厚度约为 600nm),然后形成V1的图形并进行刻蚀。多层IMD1 的主要作用是提供良好的密封和覆盖更加多孔的低k介质。 为了平坦化,需要在通孔中填充底部抗反射涂层 (Bottom-Ani-Rellective Coatings, BARC),并沉积一层 LTO (Low Temperature Oxide)。随后形成M2 的图形并刻蚀氧化物,去除 BARC 并清洗后,沉积 Ta / TaN 阻挡层和 Cu 籽晶层,随后进行 Cu 填充(使用 ECP 法),并进行 CMP 平坦化,这样 M2 互连就形成了。 通过重复上述步骤,可以实现多层铜互连。相应的,先沟槽技术的双镶嵌工艺就是先实施 M2 沟槽制备再形成 V1 的图形并刻蚀氧化物,然后沉积阻挡层和籽晶层,最后进行 Cu 填充和 CMP 平坦化。

审核编辑 :李倩

-

工艺

+关注

关注

4文章

598浏览量

28858 -

金属

+关注

关注

1文章

604浏览量

24338

原文标题:后段集成工艺(BEOL Integration Flow)- 2

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FinFet Process Flow-源漏极是怎样形成的

AMD Versal自适应SoC器件Advanced Flow概览(上)

后段刻蚀工艺(BEOL ETCH)详解

大马士革铜互连工艺详解

U50的AMD Vivado Design Tool flow设置

晶合集成28纳米逻辑工艺通过验证

集成电路工艺学习之路:从零基础到专业水平的蜕变

ERAY (FlexRay) 模块卡在INTEGRATION_LISTEN状态,为什么?

什么数据集成(Data Integration):如何将业务数据集成到云平台?

通过工艺建模进行后段制程金属方案分析

后段集成工艺(BEOL Integration Flow)- 2

后段集成工艺(BEOL Integration Flow)- 2

评论