据Ameya360电子元器件采购网报导:防静电和浪涌TVS layout设计要点

电子产品精密化

刚看过了CES2023,雷卯的外贸伙伴们看了新的AR,VR,5G产品,新的电子产品更智能、更复杂,嵌入了脆弱和敏感的集成电路。这些设备的环境往往很恶劣,产生高水平静电和快速瞬态浪涌。这些ESD事件可能会干扰设备,从故障到集成电路的破坏。

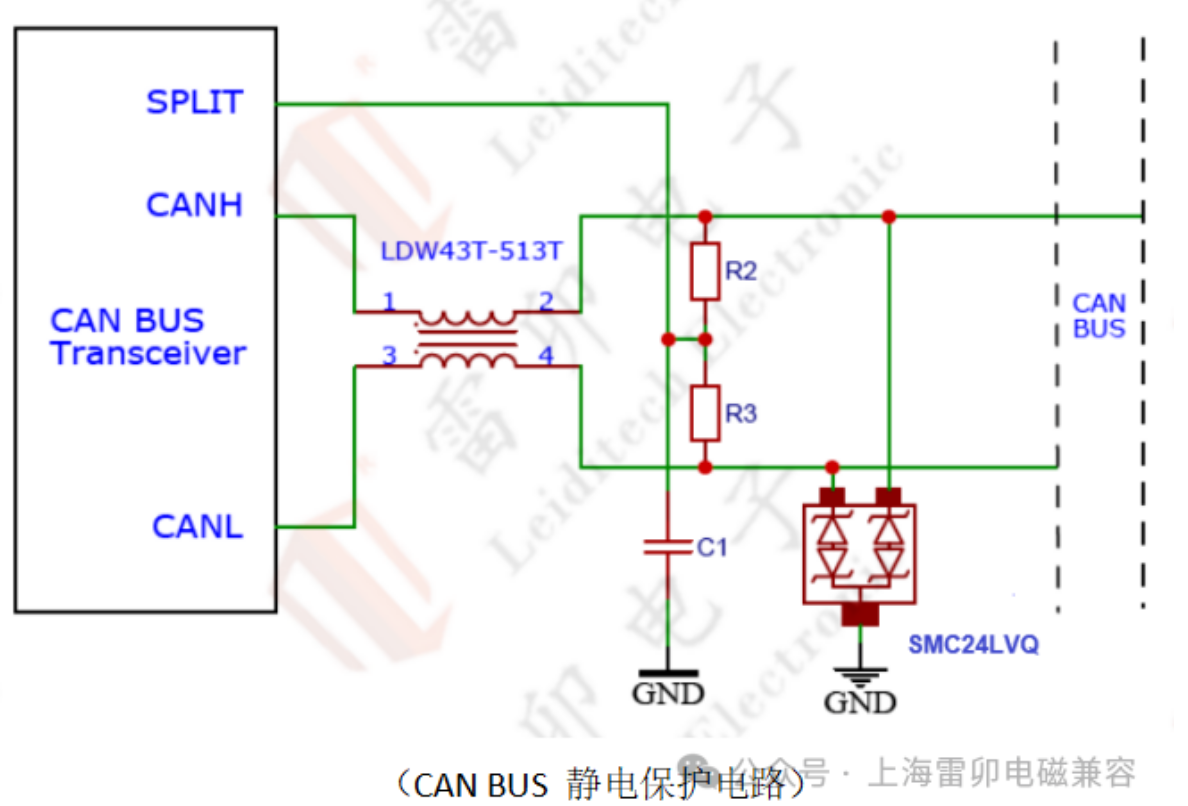

将这些问题的好方法是从PCB入口放置瞬态电压抑制器(TVS),放置在可能出现浪涌的地方;但在选择这些组件PCB布局必须小心,以确保很好的保护。

电磁兼容可靠性要求

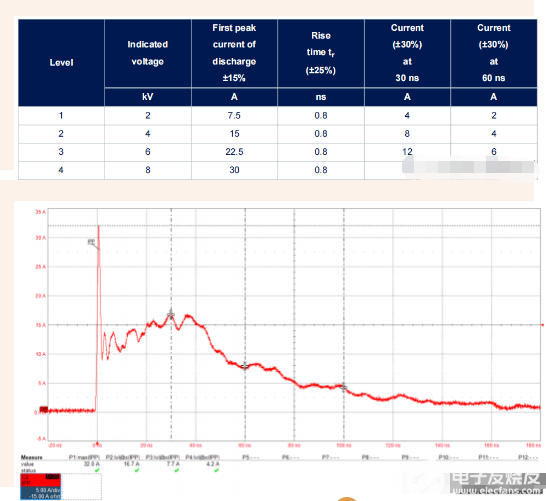

很明显,敏感部件可能会出现静电损坏风险。国际电工委员会IEC委员会定义了标准,该标准定义了四种严重等级,对应于四种电压等级,有两种放电、接触和空气类型。对接触放电的类别与电压水平和电流波形的定义显示了对接触放电的这些类别的定义以及与不同电压水平的波形的定义。

下表是IEC61000-4-2规定的接触静电放电的波形4级测试要求,附带测试标准波形的具体时间和电压图。

线路中TVS设置

大家都知道要在接口处设置TVS保护器件,但有时候达不到理想的测试效果,这里要分析一下原因:

1 TVS型号选型不当

2 PCB设计不合理,导致TVS保护效果不佳

这里主要讨论在PCB上怎么合理设计让TVS发挥优异的保护功效。

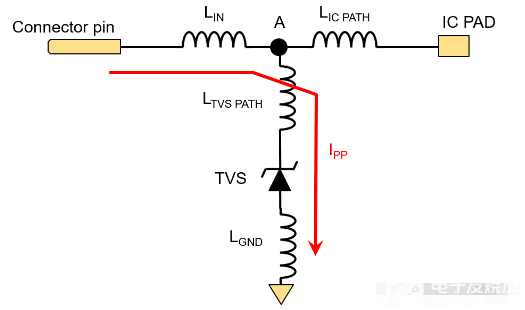

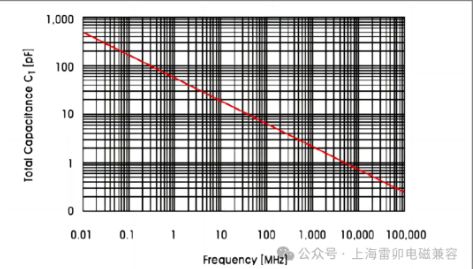

这里就要考虑线路上的各种寄生电感,包括TVS管脚自身的寄生感值。这会影响静电或浪涌发生时后端IC处的箝位电压Vc值。

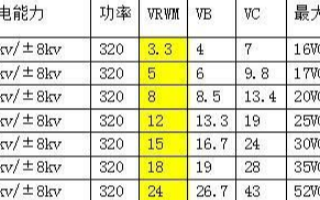

TVS本身遵从以下公式

VCL = VBR + RD × IPP

R为TVS本身的寄生电容值,越小的产品他的箝位电压会更好,更有效保护IC,IPP是测试瞬间通过TVS本身的电流值。

在测试图中,A点的电压并不是Vc值,Va电压需要加上TVS 两端的电压。

LIN和LIC由PATH通常由线路的控制阻抗(例如50Ω或100 Ω差分)驱动。为了迫使浪涌电流通过保护电路,我们必须确保LGND和LTVS路径尽可能低。此外,为了减少PCB上的辐射,好的方法是将保护电路尽可能靠近连接器针脚。

总结

以上我们看到,为了限制各种寄生电路的布局,必须注意产生的过电压和电磁干扰。注意接地连接和将TVS放置在正确的方式上,保证一个成功的电路,以确保设备的高可靠性水平的关键。综上所述,以下要点:确保保护装置连接到地面尽可能短,尽量减少寄生电感路径从静电电源到保护组件,然后从保护组件到芯片保护(而不是从静电电源到芯片保护,然后保护连接到该路径)。这也是一种避免寄生电感,将保护组件尽可能接近ESD源:这将PCB上的EMI,与其他路径耦合化PCB上的EMI,与其他路径耦合。

审核编辑:汤梓红

-

TVS

+关注

关注

8文章

805浏览量

60951 -

Layout

+关注

关注

14文章

408浏览量

62086 -

浪涌

+关注

关注

3文章

263浏览量

28628 -

防静电

+关注

关注

3文章

154浏览量

13089 -

雷卯电子

+关注

关注

0文章

57浏览量

163

发布评论请先 登录

相关推荐

Ameya360数字温度计解决方案概述

汽车电子瞬态浪涌保护用TVS如何选型?

5G!AMEYA360签约芯讯通授权代理商

防静电ESD功率可以更大了

AMEYA360:位移传感器安装要点及使用注意事项

雷卯推荐万兆、千兆、百兆网口防静电ESD

AMEYA360:上海雷卯电子推出小封装高压防静电二极管SD60C

AMEYA360:上海雷卯电子CAN BUS芯片静电浪涌击穿整改方案

Ameya360雷卯电子:防静电和浪涌TVS layout设计要点

Ameya360雷卯电子:防静电和浪涌TVS layout设计要点

评论