射频前端(RFFE,Radio Frequency Front-End)模组国内外手机终端中广泛应用。它将功率放大器(PA,Power Amplifier)、开关(Switch)、低噪声放大器LNA(Low Noise Amplifier)、滤波器(Filter)、无源器件等集成为一个模组,从而提高性能,并减小封装体积。然而,受限于国外专利以及设计水平等因素,国产滤波器的份额相当低。在模块集成化的趋势下,国内射频巨头在布局和生产滤波器。声学滤波器可分为声表面滤波器和体声波滤波器,其中声表面滤波器可根据适用的频率细分为SAW、TC-SAW和IHP-SAW。体声波滤波器适用于较高的频段,可细分为BAW、FBAR、XBAR等。无论是SAW(Surface Acoustic Wave filter)还是BAW(Bulk Acoustic Wave Filter),均是在晶圆级封测后以倒装芯片的工艺贴装在模组上。在晶圆级封装工艺中,Bump制造是相当重要的一道工序,因此本文将浅谈滤波器晶圆级封装(Wafer Level package)中Bump制造的关键点。

当前业内常见的几种SAW filter Wafer Bumping工艺如下:

1.通过打线工艺在晶圆的UBM(Under Bump Metal)上植金球。

2.通过钢网印刷工艺在UBM上印刷锡膏,再经过回流焊成球。

3.先在晶圆的UBM上印刷助焊剂,将锡球放到UBM上,再经过回流焊完成植球。

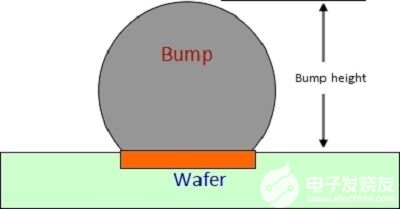

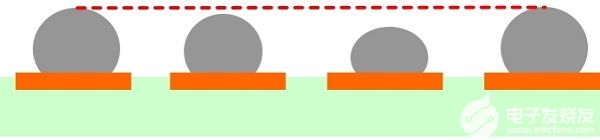

本文重点介绍第二种工艺。通过对印刷锡膏方案的剖析发现,在Bumping工艺中Bump的高度和共面度(同一颗芯片上Bump高度最大值最小值之差,差值越低越好)是最重要的关键指标(如图1.1、图1.2)。下面从钢网的工艺和设计、锡膏的特性等方面进行分析。

图1.1 球高

图1.2 共面度

钢网印刷

钢网印刷的目的是使锡膏材料通过特定的图案孔沉积到正确的位置上。首先,将锡膏放到钢网上,再用刮刀使其通过钢网开孔沉积到焊盘上。钢网与晶圆之间的距离(印刷间隙)、印刷角度、压力、速度和膏体的流变特性是确保锡膏印刷的关键参数。一旦钢网开孔被膏体填满,脱模后膏体留在每个焊盘上,沉积在焊盘上的体积取决于钢网的孔距和孔壁的质量、焊盘的表面特性和膏体的流变性能。

钢网的加工工艺与开孔设计

钢网孔壁质量、尺寸一致性、定位精度和钢网生产成本是钢网生产工艺的选择标准。考虑到带有Bump的滤波器是以倒装芯片的工艺应用在前端射频模组里,其特点是Bump的尺寸小(bump高度在50~100μm之间)、间距小、对Bump高度的一致性要求高(共面度在10μm以内)。为了满足以上要求,业内最常选用的是纳米涂层钢网和电铸钢网。

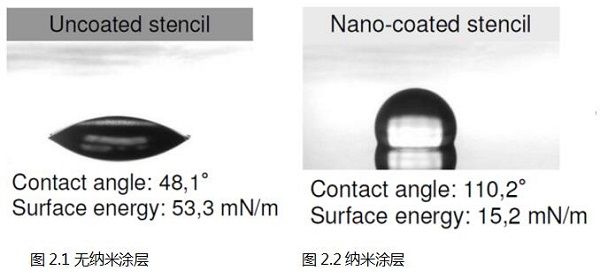

纳米涂层钢网的工艺是:在激光切割的基础上对钢网进行清洗,然后在钢网内壁进行打磨抛光以降低粗糙度,最后涂覆纳米涂层。纳米涂层使接触角显著增加,从而降低钢网材料的表面能,有利于锡膏脱模。

Source: Laser Job

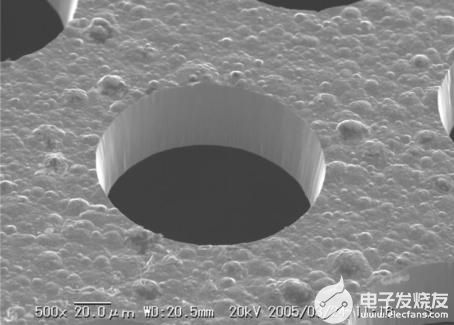

电铸钢网的制作方法是:先在导电基板上用光刻技术制备模板,然后在阻胶膜周围进行直流电铸,最后从光刻胶孔上剥离。电铸钢网的质量和印刷性能取决于光刻胶的灵敏度、所用光刻工具的类型、导电基材的光学性能和电铸工艺。电铸钢网的开孔内壁非常光滑(如图3所示),其印刷脱模的表现也最好最稳定。

图3 电铸钢网孔壁

Source: Bon Mark

小结,纳米涂层钢网的印刷表现略逊于电铸钢网,其涂层在批量生产一段时间后可能会脱落,但是纳米涂层钢网的价格远低于电铸钢网;电铸钢网的侧壁非常光滑,其印刷表现最好,是超细间距应用的最佳选择,但电铸钢网的价格相当昂贵。钢网的选择取决于客户对产品特性和成本的综合考量。

开孔面积比

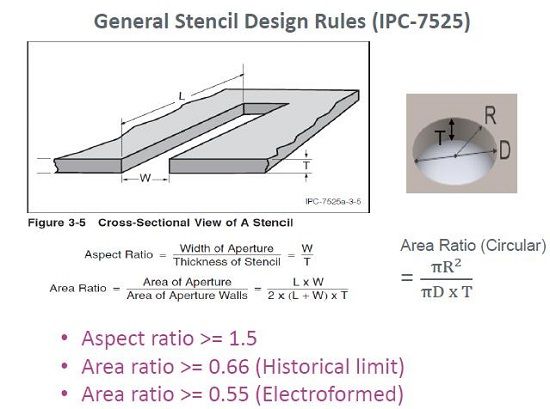

由于CTE不匹配会影响封装的可靠性,符合高度要求的Bump在这方面会起到积极的作用。这就要求钢网印刷过程可靠地沉积稳定的锡膏量,以产生坚固的互连。锡膏从钢网孔的释放是由锡膏在钢网孔侧壁和晶圆焊盘之间的相互作用决定的。据文献记载,为了从钢网印刷中获得良好的膏体释放效率,模板开孔面积比[开孔面积比=开口面积/孔壁面积]应大于0.66。该比率限制了给定孔径大小的模板厚度,并要求使用更薄的模板来印刷更细的间距。随着钢网制作工艺的提升,钢网开孔的面积比可以适当降低,如下图4所示。

图4 钢网开孔规则

锡膏

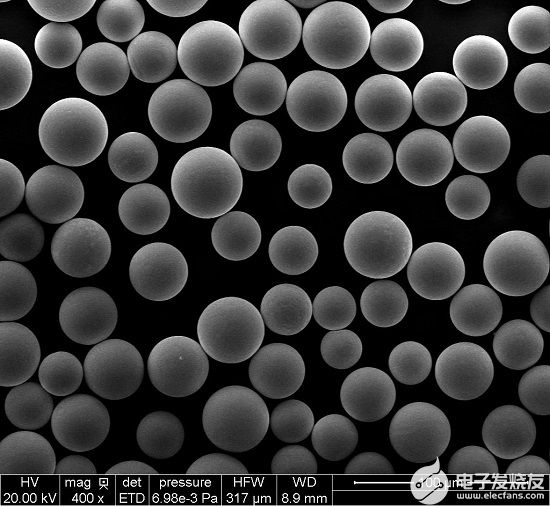

锡膏是由焊粉和助焊剂均匀混合而成的膏体,其中锡球的形状、颗粒大小、尺寸分布、氧化程度以及助焊剂载体的流变性能和配方体系,都对锡膏的印刷和回流性能起着重要作用。细间距印刷用的焊粉一直是贺利氏电子的优势,因为Welco® technology(一种在油介质中分散熔融合金的制造技术)利用两种不同介质的表面张力存在差异的原理,用工艺配方控制粉末尺寸范围,摒弃了传统的网筛工序,避免了粉末颗粒因网筛而导致的形变(表面积变大)。再者,粉末在油介质中得到充分保护,减少了粉末表面的氧化。Welco®焊粉搭配贺利氏独特的助焊剂配方体系,使印刷锡膏的转化率能够得到保证。

图5 Welco 焊粉 SEM 图片

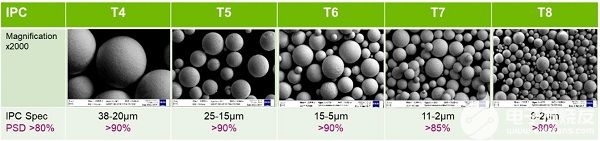

当前市场上SAW/BAW滤波器的应用中常见的Bump高度为50-100μm,结合单个芯片的layout,即相邻bump的最小间距,以及相邻芯片的bump的最小间距,6号粉和7号粉锡膏是匹配的选择。粒径的定义是基于IPC的标准(如图6),即6号粉有80%的焊粉粒径分布在5-15μm的区间。

图6 IPC粒径规格

选择合适粒径的锡膏非常重要,助焊剂体系的选择也是非常关键。因为一些SAW 的IDT 位置是裸露的,焊锡膏或助焊剂的飞溅都有可能影响IDT 的信号和声波之间的转换。对此,贺利氏开发的AP5112和AP520系列产品在开发时均在飞溅方面做了深入的研究,从而尽可能避免飞溅问题。Bump 中空洞的表现也是非常重要的质量指标,尤其是在模组中经过多次回流焊之后。

案例分享

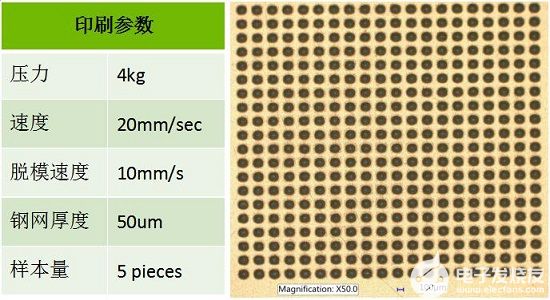

应用:SAW filter

6 inch 钽酸锂晶圆(印刷测试以铜板代替钽酸锂晶圆)

Bump 高度=72±8μm;共面度<10μm

钢网开孔尺寸:130*140*50μm

锡膏:AP5112 SAC305 T6

图7 印刷后

印刷稳定性是影响bump高度一致性的关键因素。印刷窗口的定义通常受印刷设备的能力、钢网的加工工艺、产品设计等因素的影响,通常通过实验验证获得。如图7所示,6号粉锡膏的连续印刷表现优异,没有发现连锡和大小点的问题。Bump的高度数据能够更好地说明。

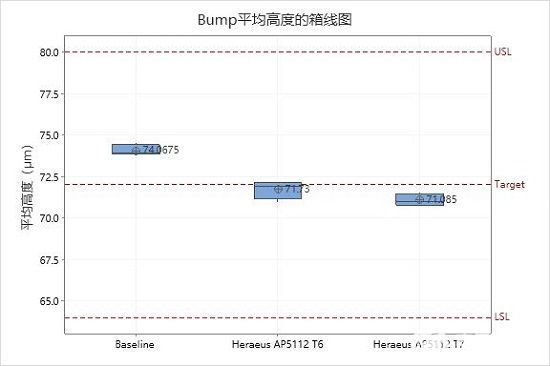

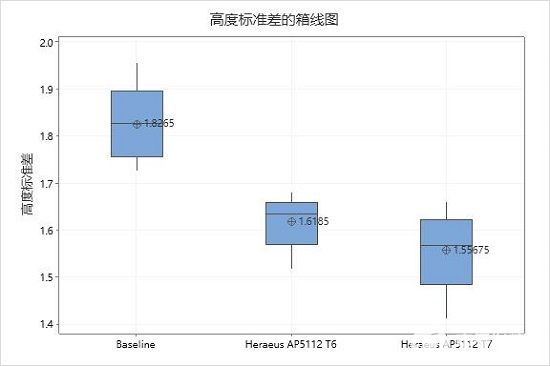

在回流焊过程中,已印刷在UBM区域的锡膏逐步熔化,助焊剂流至焊锡四周,而焊料熔化后回流到UBM上并在界面之间形成金属间化合物(Intermetallic layer),冷却后形成一定高度的Bump。Bump的平均高度非常靠近目标值,且标准差相对较小,如图8、图9所示。

图8 Bump高度数据

图9 Bump高度标准差

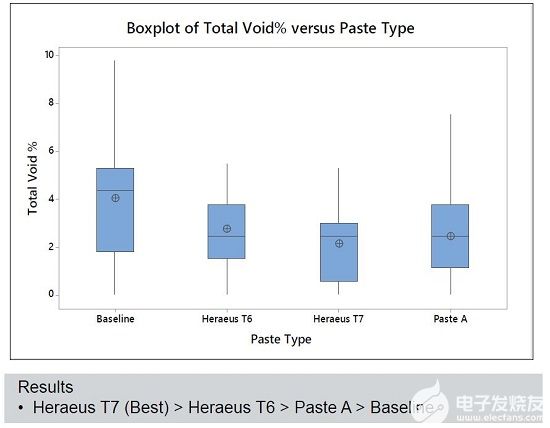

Bump 高度的指标非常关键,Bump中的空洞也至关重要。在SAW filter上面的结果显示,贺利氏的6号粉和7号粉具有良好的表现,如图10所示。

图10 Bump void 数据

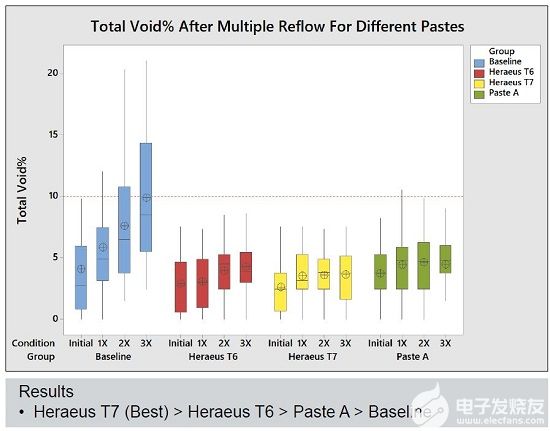

晶圆级封装最终会以芯片级应用到系统封装,即以倒装芯片的工艺集成到模组里。在此过程中会经历多次回流焊工艺,那么回流焊之后bump内部的空洞会发生怎样的变化?对此,我们测试了3次回流焊之后bump内部空洞的变化,结果如图11所示。

图11 多次回流焊后空洞变化的数据

贺利氏的6号和7号粉锡膏对应的Bump,在经过3次回流焊之后仍然能够保持在比较好的水平。

总结,本文简单阐述了晶圆级封装的关键技术点。贺利氏Welco焊粉和独有的助焊剂配方体系能够匹配SAW、BAW 等滤波器的晶圆封装需求。更深层次的技术细节,如Bump高度的设计和球高与锡膏量的关系,敬请期待下一篇文章。不论是晶圆级封装还是先进封装贺利氏都能提供成熟的解决方案。

审核编辑黄昊

-

芯片

+关注

关注

456文章

50873浏览量

424118 -

射频

+关注

关注

104文章

5589浏览量

167811 -

晶圆

+关注

关注

52文章

4920浏览量

128038

发布评论请先 登录

相关推荐

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺

不同材料在晶圆级封装中的作用

晶圆级封装Bump制造工艺关键点解析

晶圆级封装Bump制造工艺关键点解析

评论