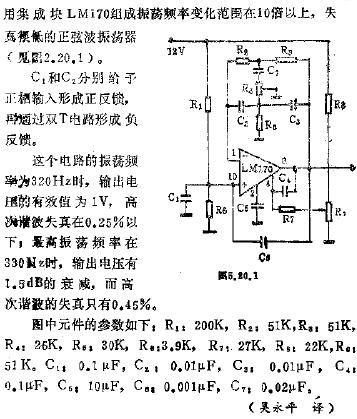

该电路利用环形计数器去除振幅最高的无用谐波,并用8阶低通、开关电容椭圆滤波器(MAX7400)滤波,从晶体控制的时钟源获得纯正弦波。

简单、低成本的电路(图1)使用数字系统中的现有时钟来生成低失真音频信号。由于大多数数字系统时钟源自晶体振荡器,因此这些时钟产生稳定而准确的正弦波。

图1.这种廉价电路从占空比为50%的时钟信号中获得低失真正弦波。

最明显的方法是将时钟频率划分为所需的音频频率,然后滤除谐波。例如,占空比为 50% 的方波仅包含奇次谐波 (3RD, 5千, 7千等),并且它们的振幅随频率而减小。3RD-谐波幅度是基波的1/3,5千是基本面的 1/5,依此类推。

如果首先衰减输入信号的最高幅度不需要的谐波,滤波电路会提供更好的结果。使用环形计数器 (U2) 和简单的加权电阻网络可以轻松完成这项工作,该网络可衰减 9 以下的所有谐波千至少 70dB(图 2)。安 8千阶低通、开关电容椭圆滤波器(U3,MAX7400)可消除大部分剩余谐波。U3的转折频率由输入时钟设置为f时钟/100.

图2.图1电路(R1–R4)中的简单电阻网络大大降低了低于9千谐波。

环形计数器U1将输入的CMOS级时钟信号除以10。第二个环形计数器(U2)也将时钟除以10,但其输出由加权电阻网络相加,产生正弦波的9步近似值。该波形由U3进一步滤波,从而衰减低于噪声水平的所有谐波。电路的输入信号(clk in)用作U3的时钟。为了达到最低失真,U3的输入应偏置至VDD/2,其输入信号衰减至2.2V峰值。这种衰减是通过一个分压器实现的,分压器由加权网络的输出电阻和滤波器IC的输入电阻(R5和R6并联)组成。在10kHz以下,所示电路的失真水平低于0.01%。

审核编辑:郭婷

-

滤波器

+关注

关注

161文章

7795浏览量

177993 -

振荡器

+关注

关注

28文章

3832浏览量

139033 -

计数器

+关注

关注

32文章

2256浏览量

94476

发布评论请先 登录

相关推荐

如何将VCO输出TTL信号转换为具有固定幅度的正弦波?

如何将0~-12v正弦波转换为±12v正弦波

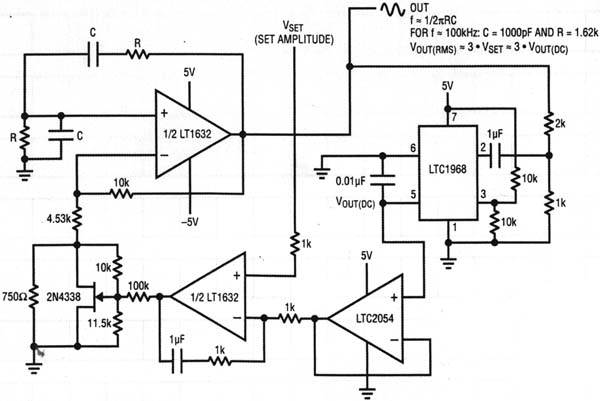

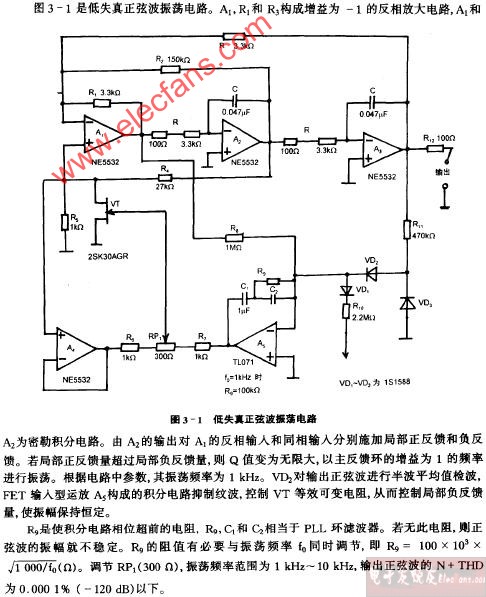

精密幅度稳定的低失真正弦波振荡器的设计

低成本电路将时钟转换为低失真正弦波

低成本电路将时钟转换为低失真正弦波

评论