Address collision 指的是RAM的两个port同时访问相同的地址可能导致数据发生错误的情况。在Xilinx中,不同的RAM,不同的RAM配置会导致address collision时不同的数据结果。

Distributed RAM

对于DRAM,写数据是 synchronous write,需要一个时钟周期, 读数据是 asynchronous read,当前时钟周期就能读出数据。因此当在某一个cycle读写同时访问同一地址时,读数据是 old data,即该地址原存放的数据而不是新要写入的数据。

Block RAM

BRAM的读写都是 synchronous。BRAM的两个Port分别为 PortA 和 PortB。

我们可以将 BRAM address collision 分为以下三类。

PortA 和 PortB 同时读数据

两个Port都会正确读出该地址中的数据。

PortA 和 PortB 同时写入数据

该地址最终被写入的数据是 non-deterministic。因此设计中要避免两个port同时写数据的address collision。

PortA 写数据同时 PortB 读数据,或者是 PortA 读数据同时 PortB 写数据

在这种情况下,数据总是会被正确写入到RAM中,但是读出的数据内容则依赖于BRAM的配置。BRAM的write mode可以配置为三种模式,write first,read first 和 no change。

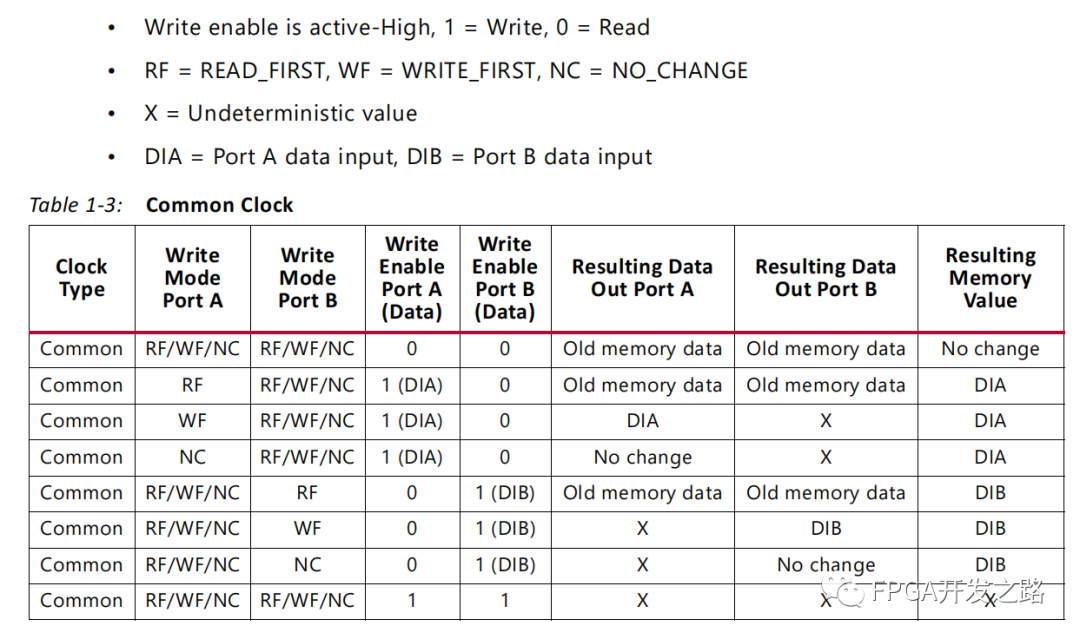

下图为不同配置下的数据读写结果。可以看到当 write port 配置为 READ_FIRST时,不管 read port 如何配置,都会读出 old data。而当 write port 配置为 WRITE_FIRST 或 NO_CHANGE时,不管 read port 如何配置,读数据都是 X,即 undeterministic。因此在可能发生address collision 的BRAM,一般将两个 port都配置为 READ_FIRST,以确保数据读出的正确。

Ultra RAM

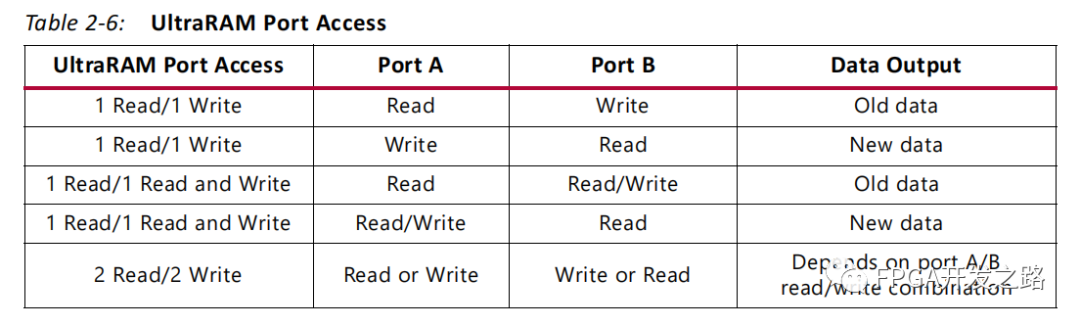

URAM的读写也都是 synchronous。URAM比较有意思的一点是,PortA 总是先于 PortB 执行操作,因此在 address collision 我们会看到不同于BRAM的结果。

PortA写,PortB读。PortB 会读出new data。(因为PortA先执行,所以在PortB读执行时,new data已经写入RAM中了)

PortA读,PortB写。PortA 会读出old data。(同样的,这也是因为PortA先执行)

PortA写,PortB写。最终该地址写入的值是PortB的值。(PortB因为后执行会覆盖PortA写的值)

Reference

《UltraScale Architecture Configurable Logic Block》

《UltraScale Architecture Memory Resources》

审核编辑 :李倩

-

数据

+关注

关注

8文章

7014浏览量

88982 -

RAM

+关注

关注

8文章

1368浏览量

114659 -

Xilinx

+关注

关注

71文章

2167浏览量

121353

原文标题:Xilinx RAM Address Collision

文章出处:【微信号:FPGA开发之路,微信公众号:FPGA开发之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么原因会导致IP地址冲突?

一般ram芯片上的引脚有哪些

工业设备IP地址冲突如何通过NAT网关解决

IP地址冲突解决方法图示

两个路由器ip地址冲突怎么解决

NAT网关实现工业设备网段隔离,解决IP冲突问题

如何解决工厂中相同IP设备冲突故障问题

stm8l中断控制串口收发,提示串口地址和变量地址冲突了怎么解决?

产线设备联网过程中的IP冲突(NAT转换)问题如何解决

你以为的RAM不是你以为的RAM~

在远程访问设备如果PLC的IP地址冲突如何解决

Xilinx RAM地址冲突

Xilinx RAM地址冲突

评论