包含2-Wire总线的应用(如I²C或SMBus™)需要在上升时间、功耗和抗扰度之间进行权衡。由于这种漏极开路总线上从低到高转换的上升时间由上拉电阻和总线电容决定,因此在添加外设、布线走线和连接器时,很难保持干净、快速的边沿。为了解决这些上升时间问题,本应用笔记介绍了一种上升时间加速器电路,该电路提供了一种加快上升时间、提高抗扰度和最小化功耗的简单方法。

电路说明

在某些2-Wire总线应用中,正确尺寸的上拉电阻可提供足够快的上升时间,以实现良好的抗噪性以及可接受的功耗。然而,具有高总线电容的大型系统或具有严格功率要求的便携式系统可能需要有源电路来实现更短的漏极开路信号上升时间。

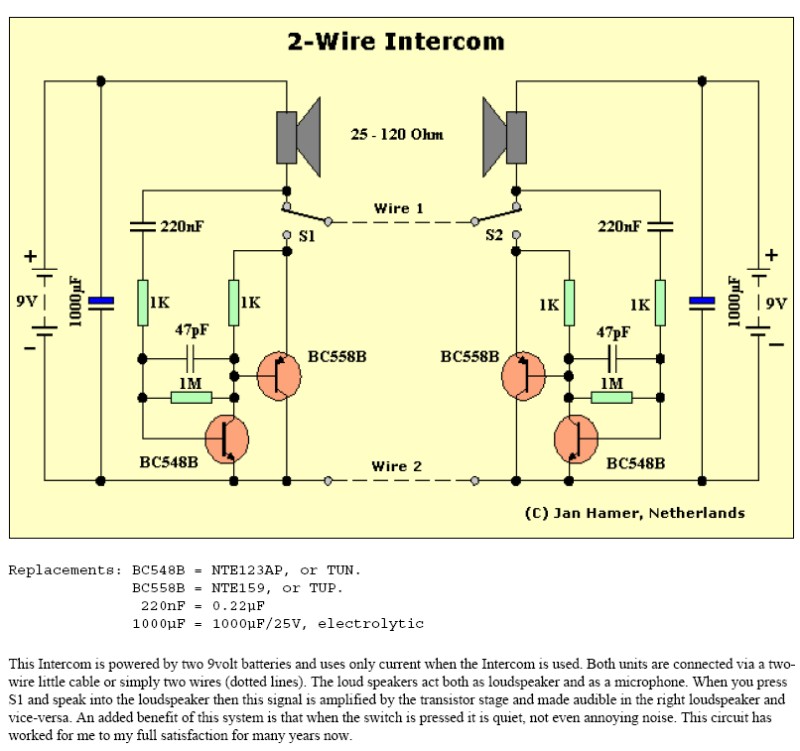

图1所示为上升时间加速器电路,该电路利用MAX3373加快上升时间,同时提高抗扰度并降低功耗。这里使用MAX3373低压电平转换器,是因为它具有加速上升时间的能力,而不是作为转换器的能力。当该IC检测到I/O引脚上的电压上升时,它会短暂开启内部强上拉(pFET),从而快速为寄生总线电容充电。然后,加速器电路在短时间后被禁用,仅留下内部10kΩ上拉电阻(加上任何外部上拉电阻)来维持高逻辑电平。

图1.MAX3373利用上升时间加速电路在快速总线上驱动高电容。

绩效评估

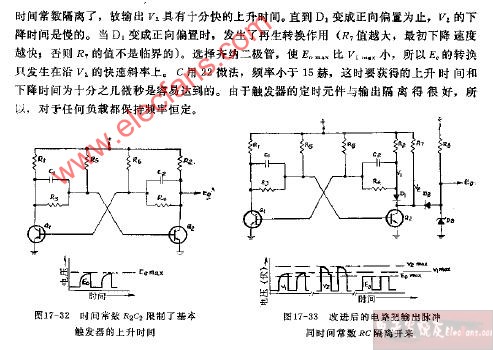

MAX3373作为上升时间加速器的有效性使用图2所示电路进行测试,其中分立式漏极开路FET同时驱动两条独立的线路。通道1由MAX3373加速,通道2端接简单的上拉电阻和寄生电容(两条线路的C相同)。MAX3373的有效上拉电阻仅为5kΩ,因为其输入和输出包括内部10kΩ上拉电阻(I/O V抄送和 I/O VL引脚)。结果显示了110pF的良性情况(图3)和I²C总线上允许的最大400pF(图4)。(请注意这些图中不同的时间尺度。

图2.该电路用于评估MAX3373电路的上升时间、电容和时钟速率。通道1利用MAX3373加速上升时间,而通道2的上升时间由简单的上拉电阻和寄生电容决定。

为了判断MAX3373电路的优势,可以考虑2线总线常见的时钟速度:100kHz和400kHz。在100kHz时,周期为10μs,高电平状态仅为5μs。因此,~110pF电容和5kΩ上拉电阻(图3)的上升时间为~1.25μs,仅为周期的12%。对于这些条件,在没有上升时间加速的情况下,性能应该是可以接受的。

图3.图解MAX3373电路(通道1)与非加速电路(通道2)在5kΩ上拉、100kHz时钟和110pF寄生电容下的上升时间。

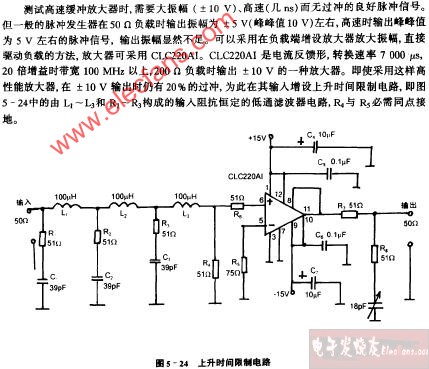

然而,对于400pF的寄生电容,上升时间为~4μs,这是周期的40%,在许多100kHz系统中是不可接受的。在400pF系统中,使用MAX3373加快上升时间可在500ns内上升90%,仅为10μs周期的5%(图4)。

图4.图解MAX3373电路(通道1)与非加速电路(通道2)在5kΩ上拉、100kHz时钟和400pF寄生电容下的上升时间。

对于400kHz总线(在2.5μs周期内提供1.25μs的高状态),上述5kΩ和~110pF条件提供的上升时间仅为1.25μs,这是周期的50%,通常不可接受。将电容提高到400pF会产生5μs的上升时间,这是周期的两倍,显然是不可接受的。然而,使用具有~110pF负载电容的MAX3373电路可提供250ns的90%上升时间,仅为2.5μs周期的10%;在400pF时,它的上升时间仅为~500ns,或周期的20%。

总结

使用MAX3373电路作为上升时间加速器是解决2线总线上升时间与时钟问题的几种方法之一。在某些情况下,只需降低上拉电阻即可加快上升时间。然而,MAX3373提供了一种简单的方法来加快上升时间,同时提高抗扰度并最大限度地降低功耗。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8701浏览量

147150 -

总线

+关注

关注

10文章

2879浏览量

88070 -

I²C总线

+关注

关注

0文章

14浏览量

2127

发布评论请先 登录

相关推荐

I²C等双线总线上升时间加速电路

上升时间加速器LTC4311相关资料下载

2线总线上升时间加速电路

浅谈振荡上升时间及影响

上升时间加速器LTC4311的作用及性能分析

LTC4311 - 400kHz 上升时间加速器改善了重负载 I<sup>2</sup>C/SMBus 系统可靠性

信号频率和上升时间的关系

TCA39416具有上升时间加速器的超低电压I3C转换器数据表

具有上升时间加速器的TCA9416超低电压I2C转换器数据表

用于2-Wire总线应用的上升时间加速器电路

用于2-Wire总线应用的上升时间加速器电路

评论