周末正好撸到了芯片的DFT设计,特此分享两个案例。

DFT经典案例1:

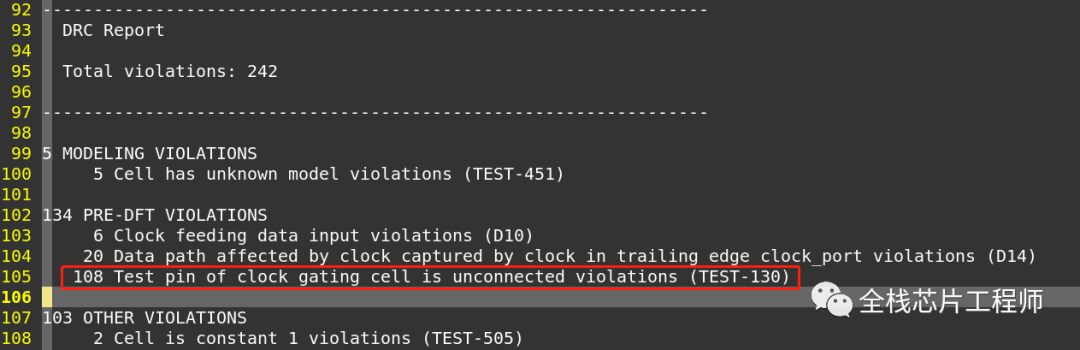

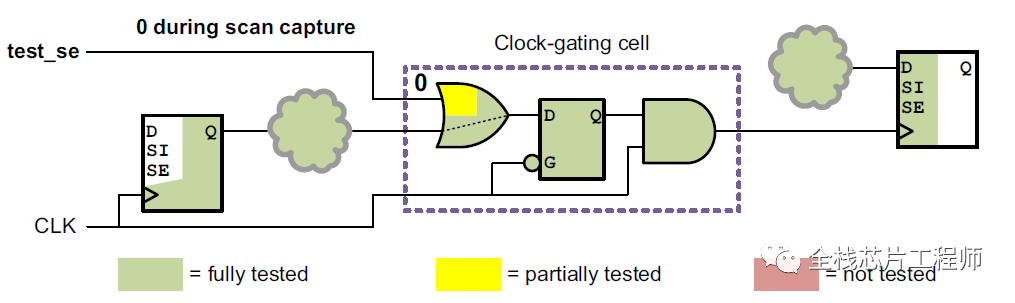

clock gating cell报警如下:Test pin unconnected。当工具运行pre-DFT DRC检查时,每个clock gating cell都会有TEST-130 message报出来,不管clock gating cell是discrete-logic还是integrated ICG。

如下图:108 Test pin of clock gating cell is unconnected violations (TEST-130)

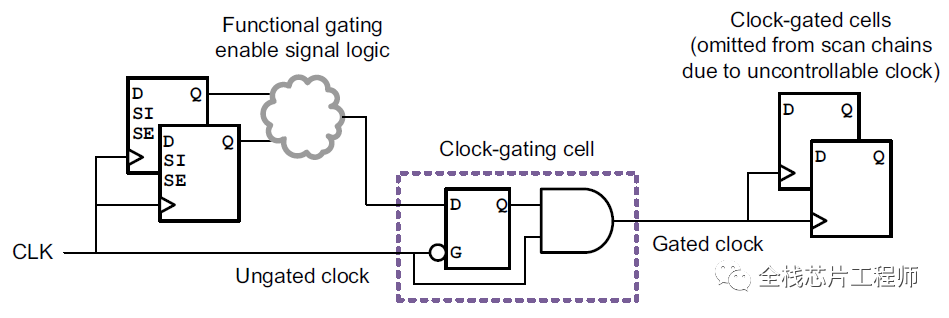

我们知道门控时钟会造成DFT scan时钟不可控,因此需要特殊处理,比如加入control point。

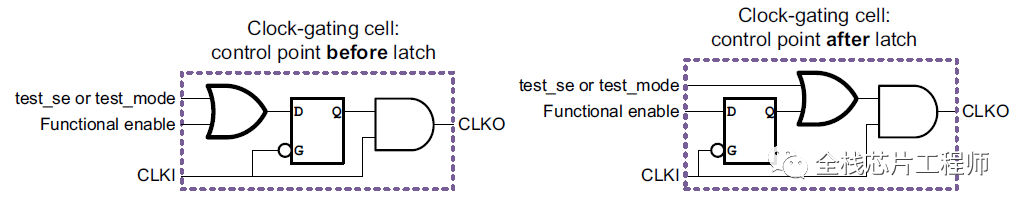

control point可以放在ICG latch的前面或者后面,为了避免毛刺,推荐control point放在latch前面,业界ICG都是将control point放在latch前面的。

另一个经典问题就是,用test_mode还是scan_enable来驱动Clock-gating cell的TE端口?

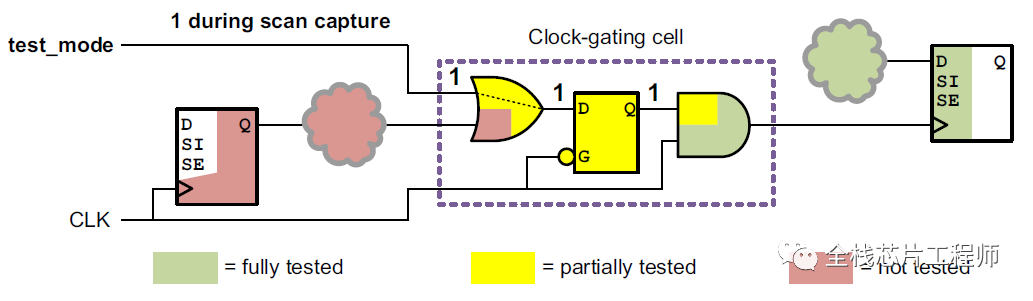

scan_enable只是在scan shift运行时候才有效,capture时候scan_enable是无效的。test_mode是整个测试期间都有效,即scan shift和scan capture阶段test_mode都有效。

test_mode接TE的缺点是capture mode下无法测试到functional clock-gatinglogic,就是functional clock-gating logic完全被bypass了。此外test-mode 仅能被测试stuck-at-0 faults (假设test-mode 信号为高有效情况下)。

那么用test_mode还是scan_enable来驱动Clock-gating cell的TE端口?自然是scan_enable,可以提高测试覆盖率。

因此我们可以在dft的约束中加入如下脚本:

set_clock_gating_style -control_point before -control_signal scan_enable

对于CRG模块RTL里面手动例化的ICG而言,TE接test_mode的话,那么ICG在test_mode下一直是transparent,后面的flip-flop在shift in和capture时都有clock。TE接scan_enable,那么在capture 时一定要保证ICG后面的flip-flop都有clock,此时用scan_enable可以提高一些DFT的覆盖率。

DFT经典案例2:

rst_n_pad作为芯片function的复位信号,也作为DFT Scan的复位信号,命令如下:

set_dft_signal -view existing_dft -type Reset -port rst_n_pad -active 0

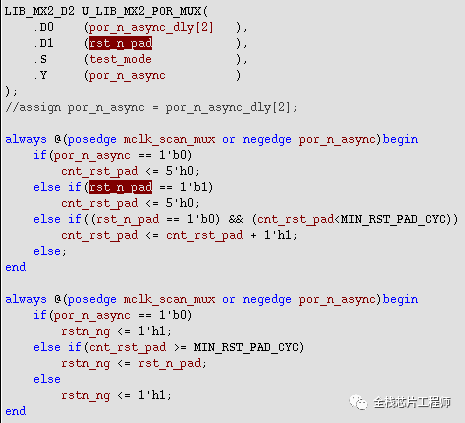

在设计的func中,有对rst_n_pad复位信号做毛刺过滤功能,代码如下图:

这段代码在DFT设计中,会有什么问题呢?很精彩!

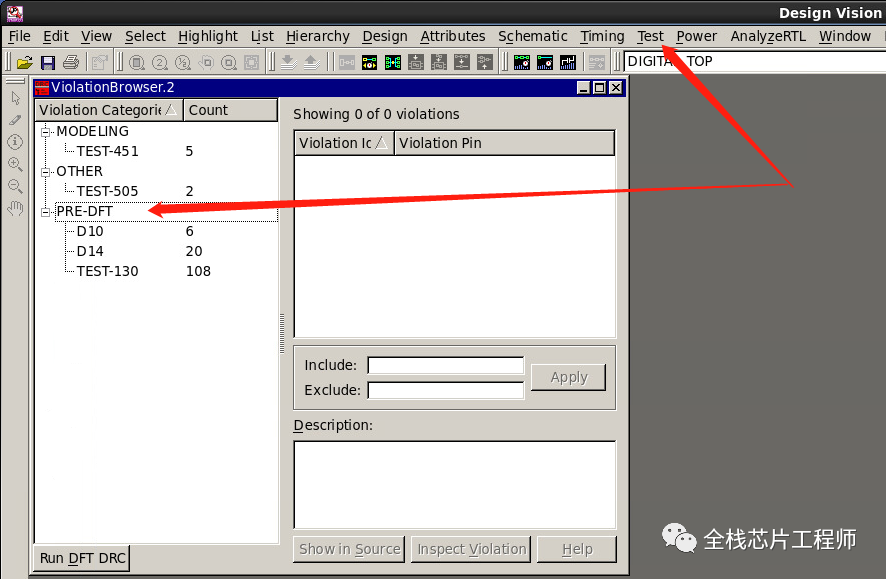

打开DC GUI界面进行DFT_DRC定位:

dc_shell> gui_start

点击Test -> Run DFT DRC

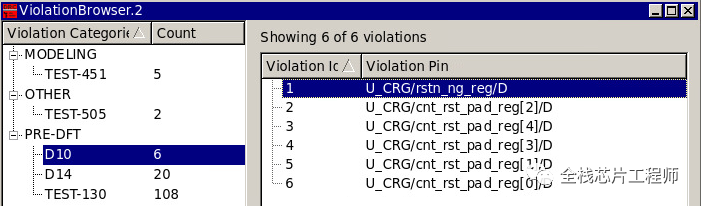

工具报错说D10有6个,挑选一个进行解释:

rst_n_pad ( Warning: Clock rst_n_pad connects to data input (D) of DFF U_CRG/cnt_rst_pad_reg[0]. (D10-6) )

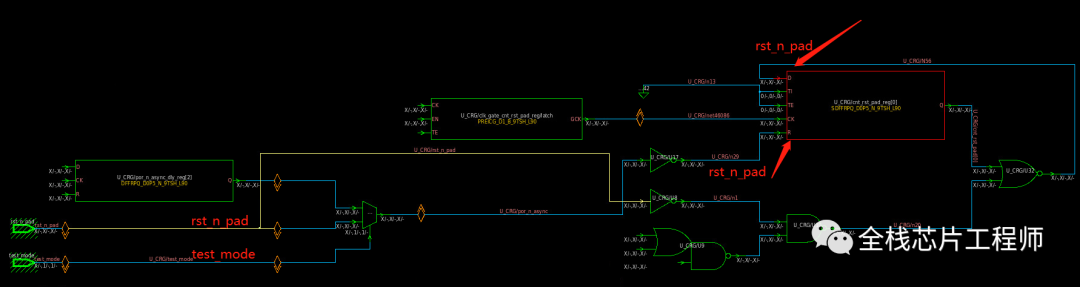

从如下电路看出,rst_n_pad作为DFT的复位信号,在test_mode=1有效时候对cnt_rst_pad_reg[0]进行复位,但是rst_n_pad也会传递到cnt_rst_pad_reg[0]的D端,从而造成什么问题呢?先思考下。

审核编辑 :李倩

-

芯片

+关注

关注

463文章

54601浏览量

470678 -

时钟

+关注

关注

11文章

2002浏览量

135384 -

DFT

+关注

关注

2文章

237浏览量

24131 -

复位信号

+关注

关注

0文章

71浏览量

6838

原文标题:DFT设计实战案例解读

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DFT设计实战案例解读

DFT设计实战案例解读

评论