随着电子产品的集成度越来越高,PCB板的尺寸越来越小,板级芯片散热的问题越来越成为电子工程师的一个重要挑战。 对于板级芯片散热,主要依靠工程师对 PCB自身的设计进行优化 ,同时要兼顾系统的尺寸和成本。 本文分别从芯片角度和PCB角度进行建模,芯片模型选用QFN封装,PCB模型采用走线导入模型,探讨了芯片结构,PCB铜厚,PCB叠层厚度对芯片散热的影响。

2、建模过程

为了最大程度的还原仿真对象,PCB模型采用Icepak自带PCB模型,通过导入真实的走线Trace真实模拟PCB的散热能力。 芯片也是采用Icepak自带的Package模型 对QFN封装进行详细建模。

2.1 PCB 板建模

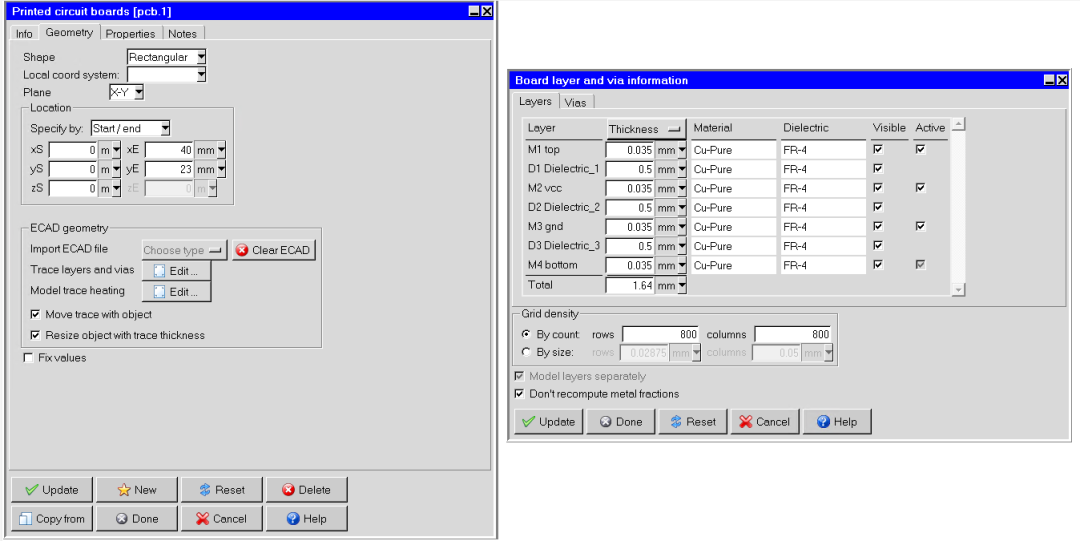

通过ODB模型导入PCB 走线信息,并编辑PCB的叠层及铜厚:

设置板子尺寸为23X40mm

PCB铜厚为1oz(0.035mm)

PCB总叠层厚度为1.64mm

不考虑走线电流发热影响( 可通过SIwave导入,关注我后续带你分析! )

图2.1 PCB 参数和走线导入设置

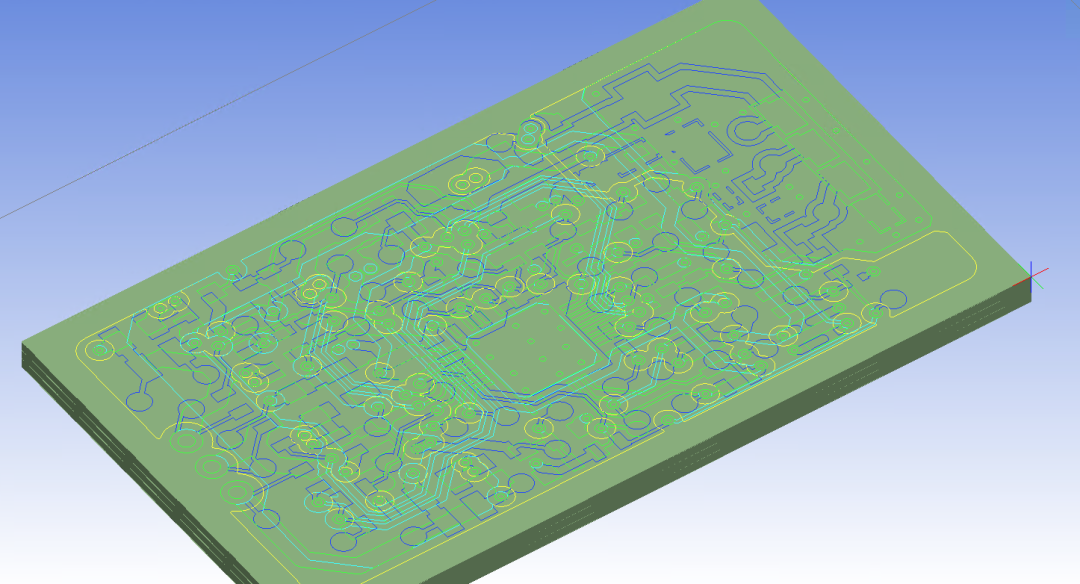

图2.2 PCB 导入走线后视图

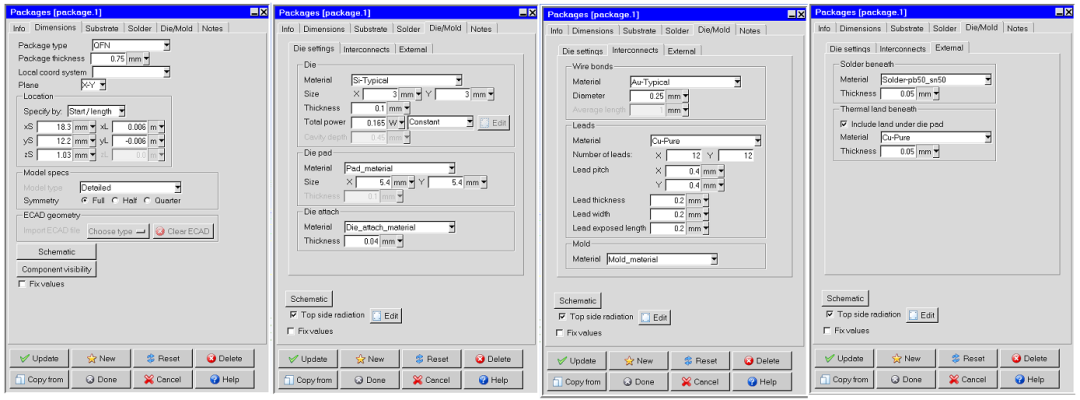

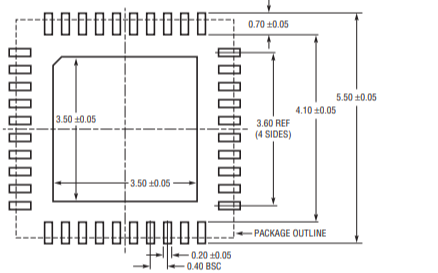

2.2 QFN 芯片封装建模

根据数据手册尺寸设置QFN 芯片尺寸:

芯片外尺寸6x6x0.75mm

芯片Die尺寸3x3mm

散热盘尺寸5.4x5.4mm

芯片损耗为0.165w

其他按照规格书设置

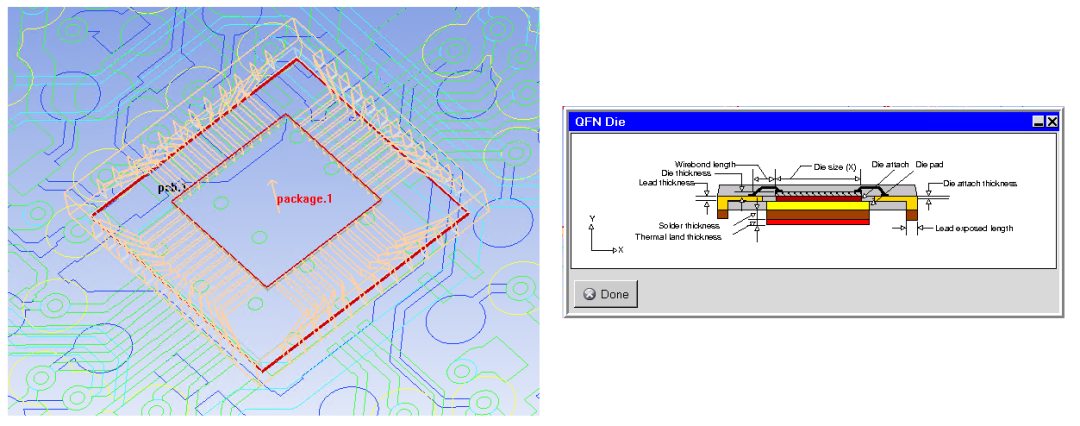

图2.3 QFN 芯片封装设置

图2.4 QFN 芯片参数说明

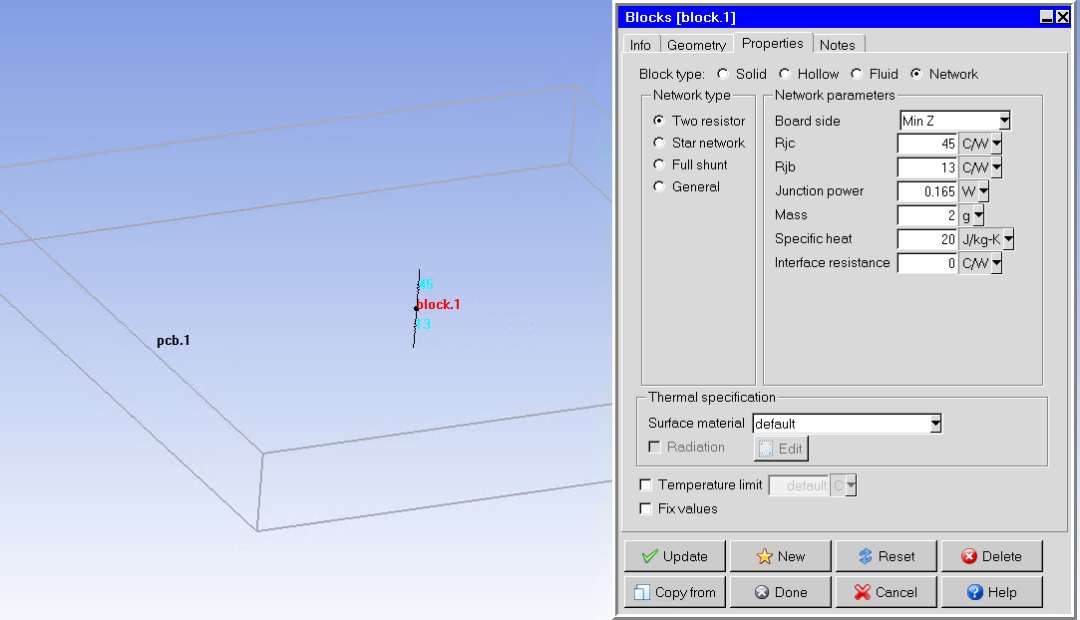

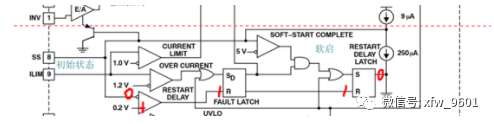

2.3 基于热阻模型的芯片建模

使用QFN的热阻参数,建立二维热阻模型:

MinZ 为紧贴PCB的面(Bottom)

Rjc为 Junction-Case 热阻

Rjb为 Junction-Bottom 热阻,为主要传热路径

芯片损耗为0.165w

图2.5 QFN的二维热阻模型

3、仿真结果

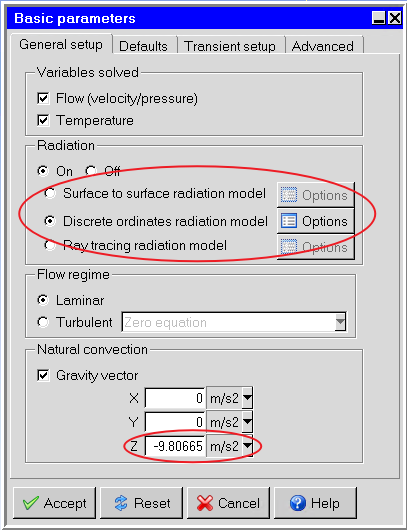

静态PCB散热主要形式为 自然对流和辐射散热 ,通过重力模拟,和DO辐射模型对PCB进行仿真,参数设置如下:

图3.1 仿真参数设置

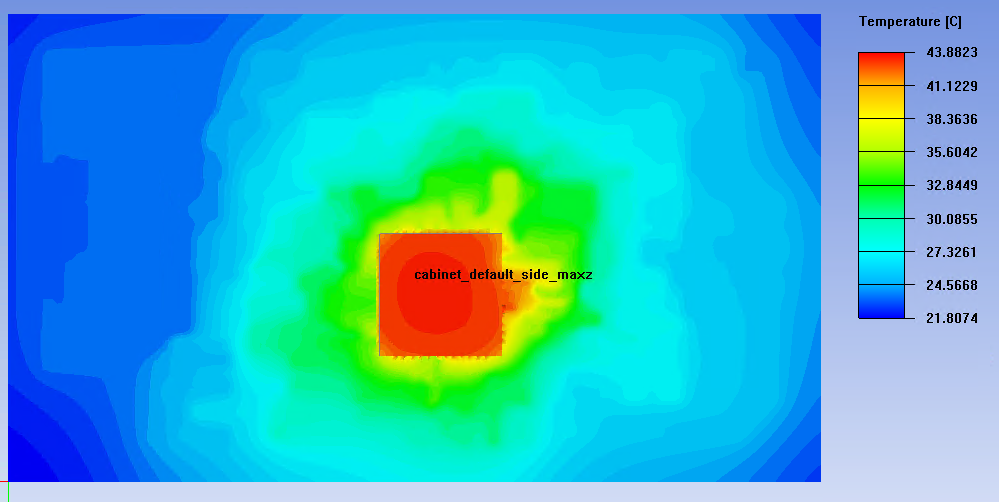

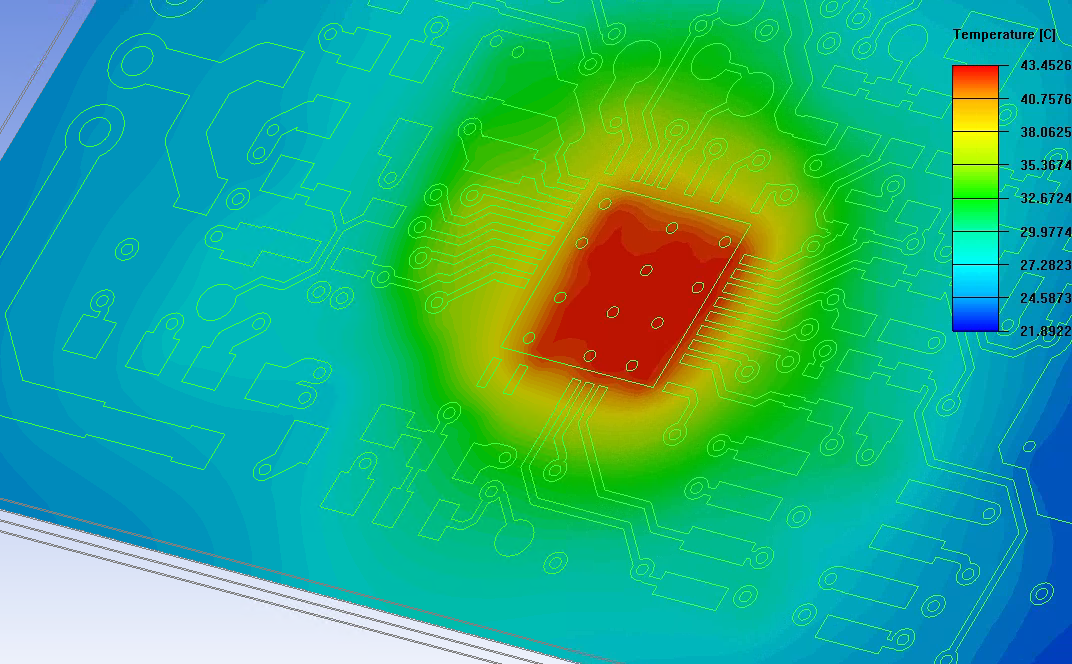

通过芯片和PCB的详细建模,可以获得散热模型的各种散热细节的仿真结果:

图3.2 PCB 表面散热云图

图3.3 PCB 内层散热云图

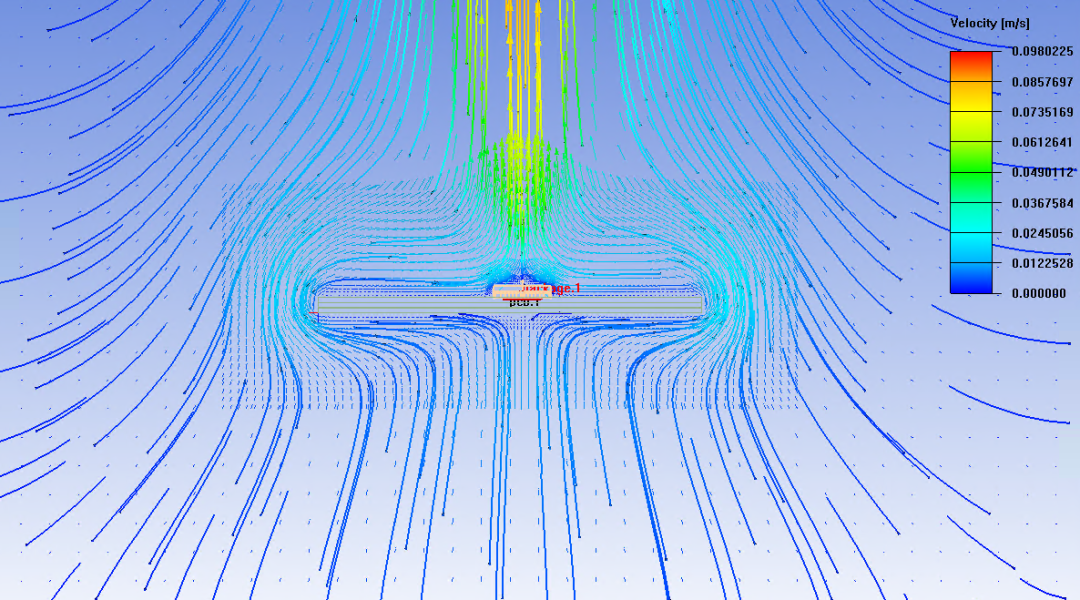

图3.4 PCB 周边自然对流情况

对仿真结果进行处理和分析:

| 仿真序号 | 仿真条件 | 仿真温度 | 温升 |

|---|---|---|---|

| --------------------------------------------------------------------------------- | |||

| 1,102 | 20C,Pdis=0.165W,真实QFN模型; 铜厚1oz,叠层绝缘层0.5mm | 56.8摄氏度 | 36.8摄氏度 |

| - | - | - | - |

| 2,104 | 20C,Pdis=0.165W, 热阻QFN模型 ; 铜厚1oz,叠层绝缘层0.5mm | 59.3摄氏度 | 39.3摄氏度 |

| 3,105 | 20C,Pdis=0.165W,真实QFN模型; 铜厚2oz ,叠层绝缘层0.5mm | 43.9摄氏度 | 23.9摄氏度 |

| 4,106 | 20C,Pdis=0.165W,真实QFN模型; 铜厚2oz ,叠层绝缘层0.25mm | 36.2摄氏度 | 16.2摄氏度 |

| 5,107 | 20C,Pdis=0.165W,真实QFN模型; 铜厚1oz,叠层绝缘层0.5mm,PCB倒立放置 | 57.0摄氏度 | 37.0摄氏度 |

| 6,108 | 20C,Pdis=0.165W,真实QFN模型; 铜厚1oz,叠层绝缘层0.5mm,侧面0.1m/s风冷 | 54.7摄氏度 | 34.7摄氏度 |

由上述仿真结果看出:

真实的QFN模型和热阻模型温度偏差不大,通过使用热阻模型可以简化建模过程

增加PCB 铜厚可以大幅度降低芯片温度,但是成本增加

减少PCB 叠层厚度能够降低芯片温度,成本几乎不变

PCB的摆放角度对芯片温度有一定影响,但是影响有限

微弱的空气对流,对芯片温度影响不大

小结

本文通过对PCB和QFN芯片建模,模拟的多种工况条件下的芯片散热,其中影响PCB散热最直接的因素为 PCB叠层厚度和走线铜厚 !

-

芯片

+关注

关注

455文章

50714浏览量

423159 -

封装

+关注

关注

126文章

7873浏览量

142896 -

建模

+关注

关注

1文章

304浏览量

60765 -

qfn

+关注

关注

3文章

190浏览量

56184 -

PCB

+关注

关注

1文章

1795浏览量

13204

发布评论请先 登录

相关推荐

QFN封装的组装和PCB布局指南

求各位高手相助 关于PCB设计中QFN封装芯片的问题

什么是小间距QFN封装PCB设计串扰抑制?

大家焊接QFN芯片有什么妙招吗?

基于PSO和SVM的发酵过程建模与优化控制

软件过程建模方法研究

如何在 QFN 封装芯片的 PCB 设计上得到尽可能好的串扰性能(中文讲解视频 + PPT下载)

过程系统建模与仿真.pdf

QFN封装是什么?有什么特点?

技术资讯 | 通过倒装芯片 QFN 封装改善散热

PCB和QFN芯片建模过程

PCB和QFN芯片建模过程

评论