PCB布局是优化高速板线性度性能的关键因素。 本系列的前几篇文章讨论了减少二次谐波失真的一些基本技术。 这篇文章,灵感来自TI文档”高速印刷电路板布局技术“,试图详细讨论如何在高速差分ADC驱动器中布置轨到轨和轨到地旁路电容,以实现最大可能的线性度性能。

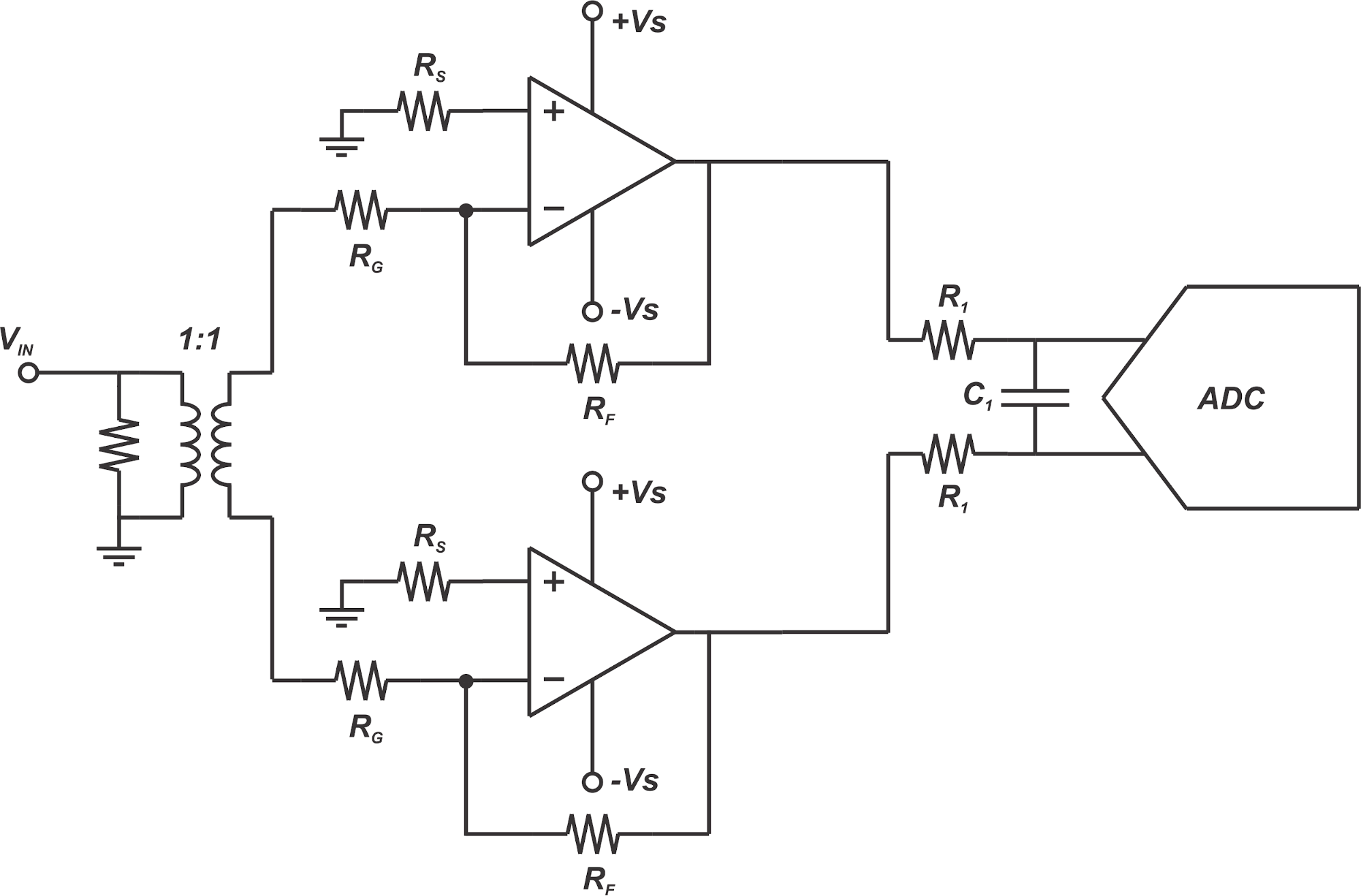

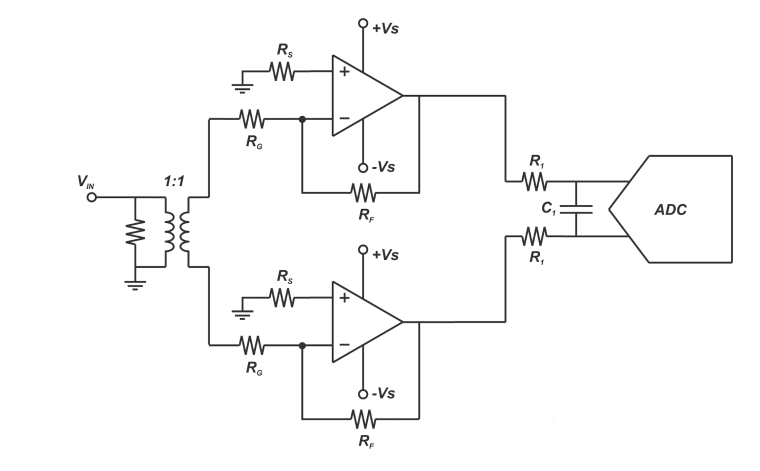

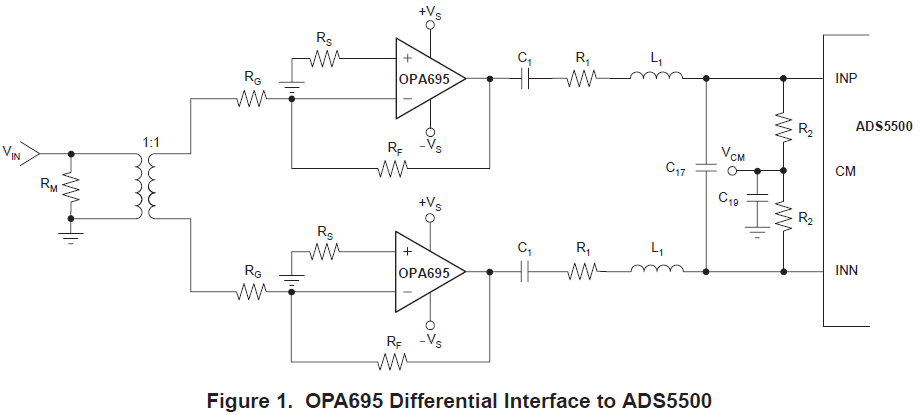

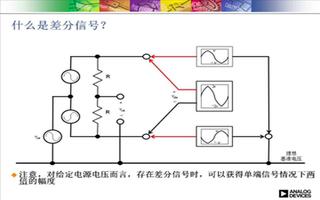

如图1所示,差分ADC驱动器可通过采用两个单端运算放大器来实现。

图1. 使用两个相同的单端运算放大器实现差分ADC驱动器

将差分信号施加到这些相同的路径上时,各个运算放大器将产生相同的二次谐波分量。 这些失真分量在ADC输入端显示为共模信号,与任何其他共模噪声和干扰信号一样,差分ADC将抑制这些失真分量。

在上一篇文章中,我们讨论了对称印刷电路板布局需要保持两条单端路径相同并衰减二次谐波。 在本文中,我们将讨论如何布置运算放大器的去耦电容,以实现最大可能的线性度性能。

我们知道 去耦电容器充当电荷源 并提供运算放大器应向负载提供的高频电流。 为了提供高频差分电流,我们可以使用轨对地和轨到轨去耦电容器。

轨到轨与轨到地面解耦结构

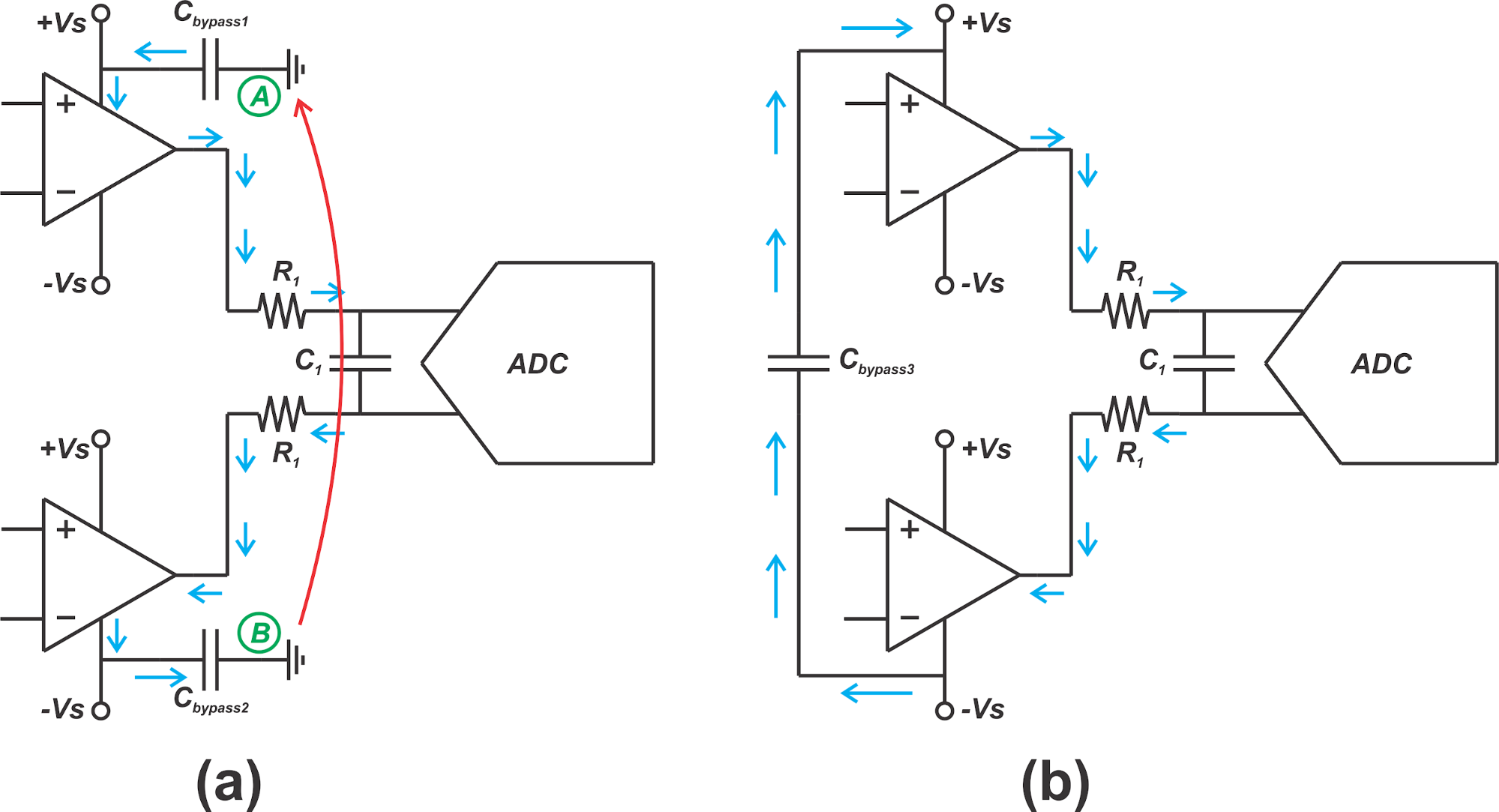

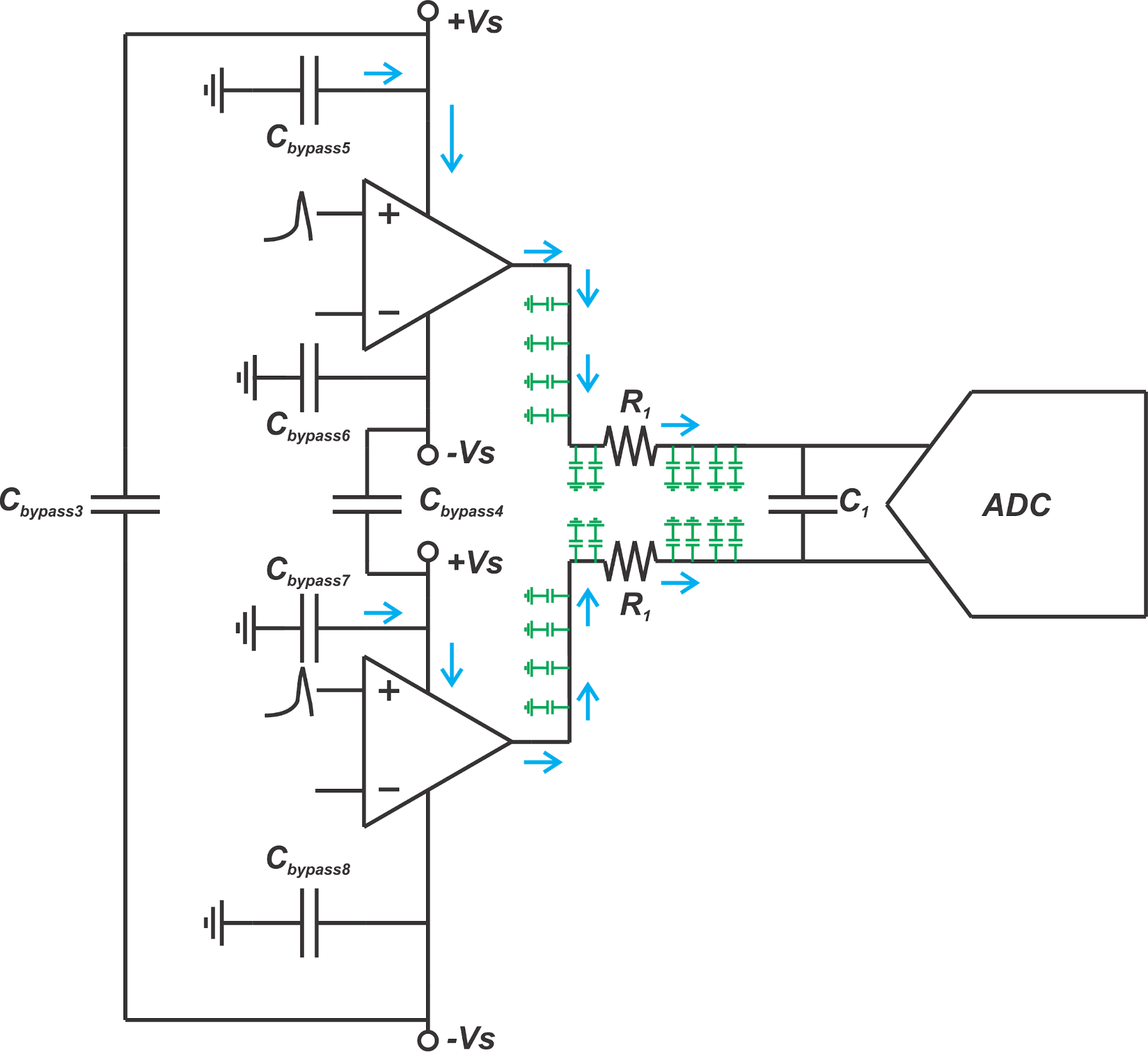

采用图1所示结构,输送到负载的电流是差分的,即当上部运算放大器向负载提供电流时,下部支路吸收电流,反之亦然。 让我们考虑一下上部运算放大器提供负载电流,而下部路径吸收负载电流的情况。 轨对地和轨到轨去耦选项以及电流路径如图2所示。 请注意,为简单起见,本图中未显示放大级的电阻。 此外,我们假设采用具有专用接地层的多层板。

图2. 轨对地 (a) 和轨到轨 (b) 去耦结构

采用轨对地去耦结构(图2(a)),高频电流将从正电源轨(C旁路1) 到负载,然后到负轨的旁路电容器 (C旁路2)如蓝色箭头所示。 电路原理图暗示节点A和B都位于地面,蓝色箭头所示的路径是电流的闭合路径。 然而,实际上,节点A和B是接地层上的两个不同节点,电流应该从节点B流向节点A,以获得闭合的电流路径。 因此,负载电流将通过接地层提供的阻抗最小的路径流回C的接地侧旁路1.

这种结构的挑战在于,在接地层中流动的任何足够接近负载电流返回路径的电流都可以与负载电流耦合并改变它。 此外,如果负载电流返回路径从节点B到A出现任何不对称,ADC驱动器的单端路径之间的对称性将受到影响,ADC输入端将出现更大的二次谐波。

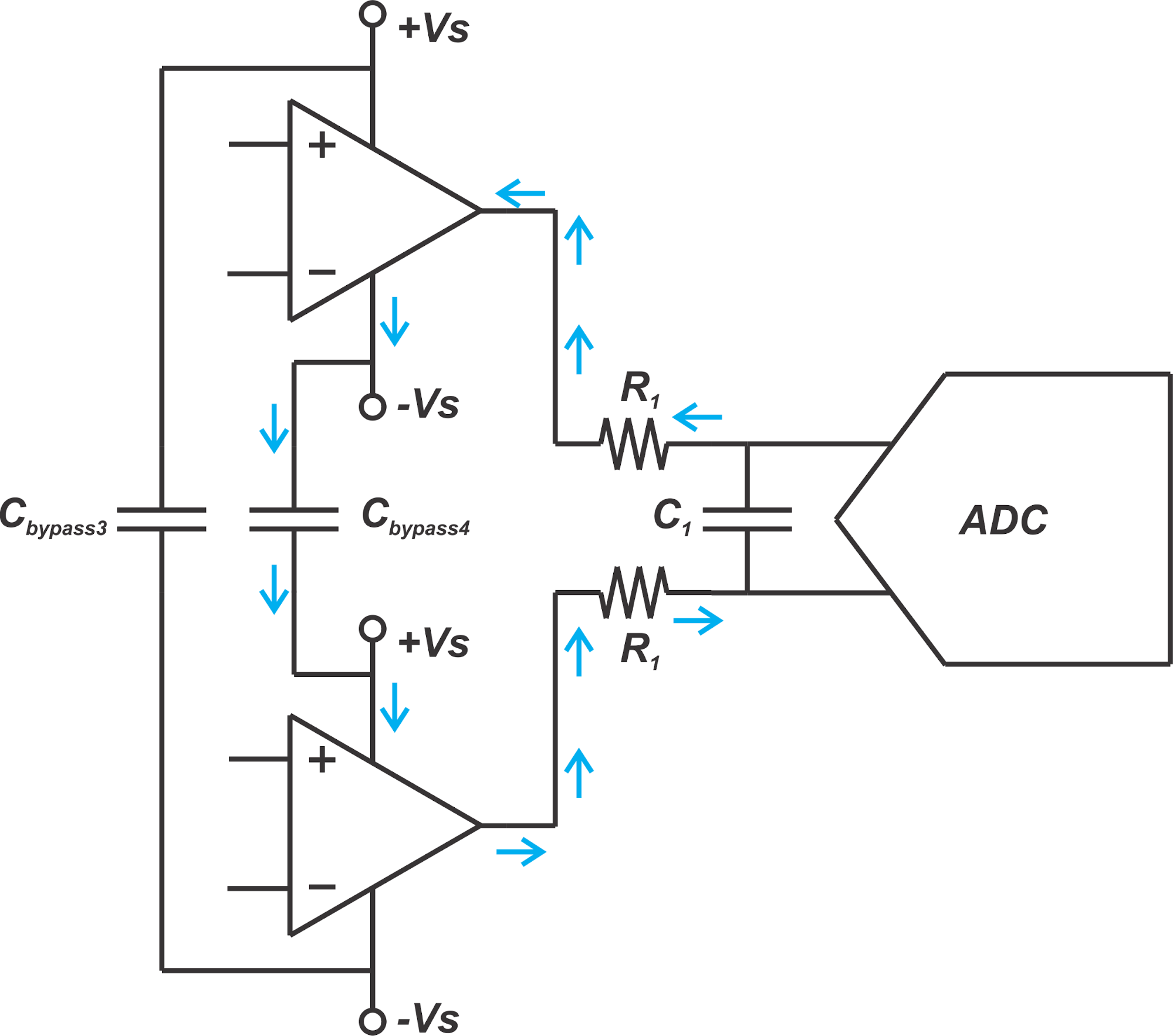

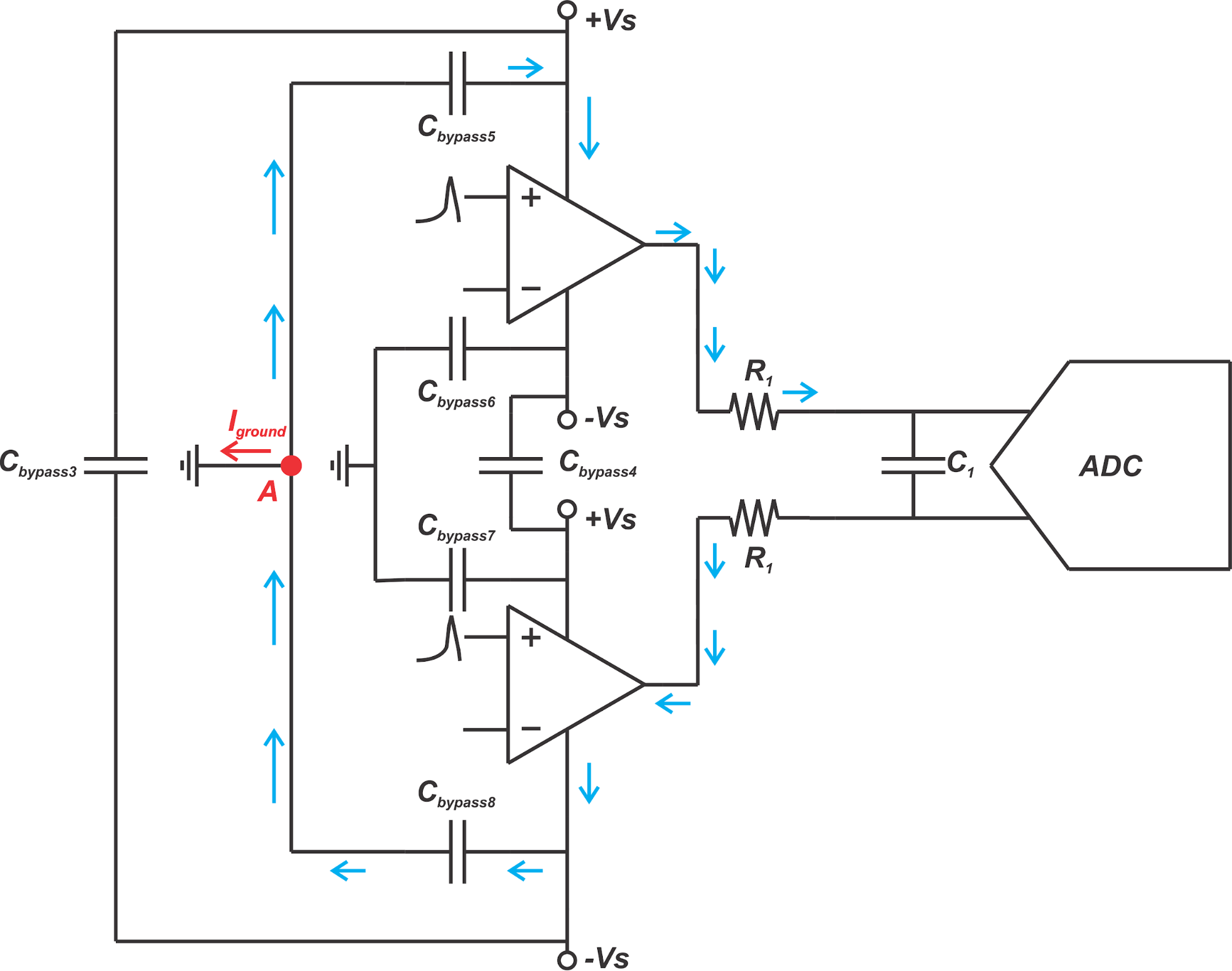

为了避免这些问题,可以采用图2(b)中的去耦结构,在两个电源轨之间放置一个旁路电容。 这样,差分负载电流将沿着蓝色箭头所示的路径流动,而不必流过接地层。 根据TI 文档,轨到轨旁路电容器可将二次谐波失真降低6至10dB。 请注意,为了提供相反方向的差分负载电流,我们需要包括另一个轨到轨旁路电容(C旁路4) 如下图 3

所示。

图3

C 提供的负载电流路径旁路4 由蓝色箭头显示。

共模电流呢?

采用图1所示结构,运算放大器提供的电流主要是差分电流,可由轨到轨去耦电容提供。 但是,我们仍然可以使用小的共模电流元件。 例如,假设噪声分量耦合到两个运算放大器的同相输入,并略微提高这些节点的电压。 这将产生从两个运算放大器流出的共模电流。 如图4所示,这样的共模电流将为PCB走线的杂散电容充电。

图4

请注意,轨到轨旁路电容无法提供这些共模电流。 在图4中,运算放大器必须直接通过电源和接地导体提供高频共模电流分量,这是不需要的。 因此,我们需要添加轨对地旁路电容,如图5所示。

图5

如您所见,从两个运算放大器流出的共模电流将由正电源轨和地之间的旁路电容提供(C旁路5 和C旁路7)。 该共模电流将为走线的寄生电容充电。 因此,返回电流将从寄生电容的接地侧流回C的接地侧旁路5 和 C旁路7在接地层中。 类似地,两个运算放大器吸收的共模电流将由放置在负电源轨和地之间的旁路电容提供(C旁路6 和 C旁路8)。

轨对地电容可提供共模和差分电流

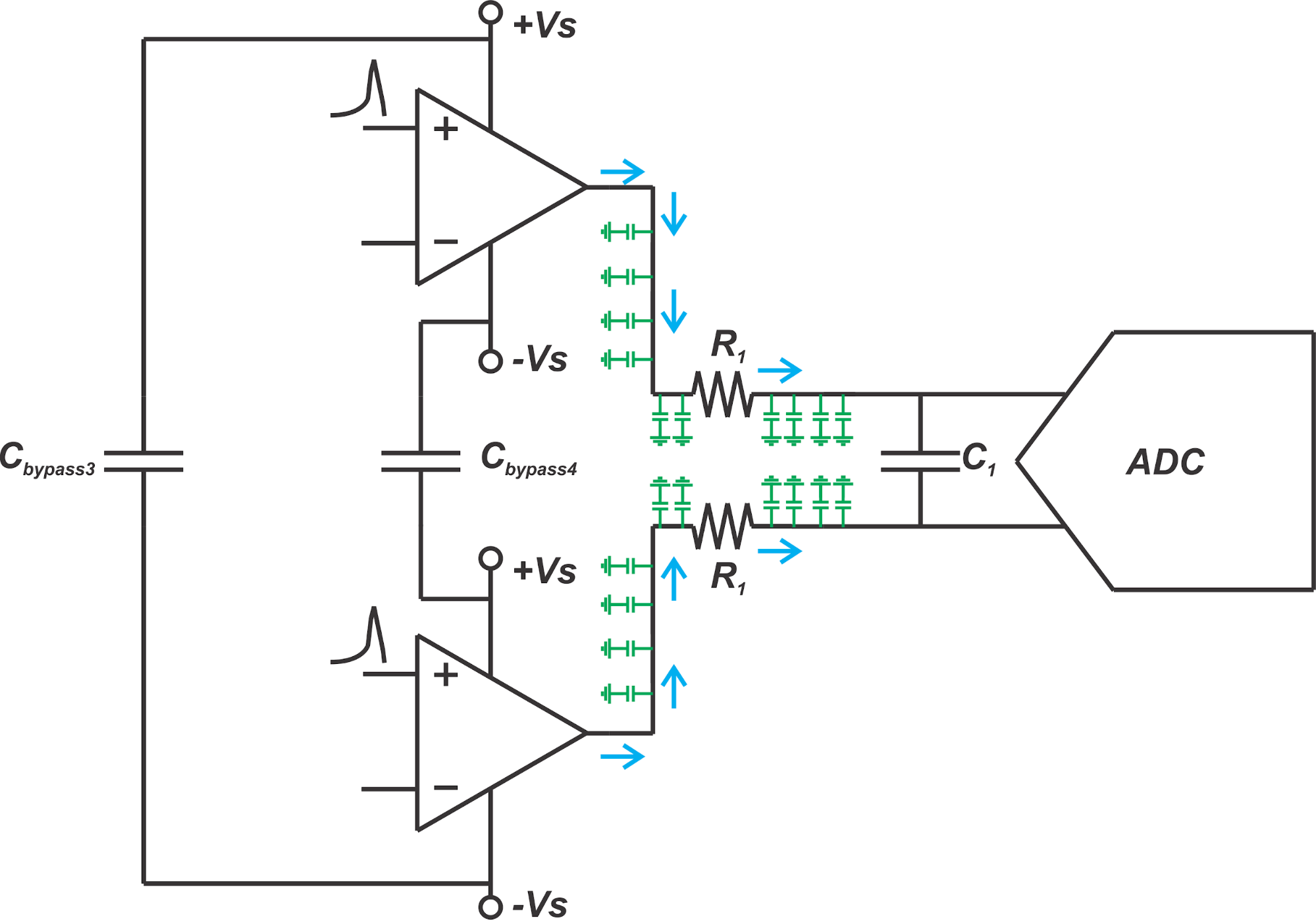

虽然我们添加了 C旁路5, C旁路6, C旁路7和 C旁路8为了提供共模电流,这些电容器还将提供负载的一部分高频差分电流。 如图2(a)所示,使用轨对地电容会不必要地使差分负载电流流过接地层,这是不需要的。 为了避免这种情况,我们可以放置能够以对称方式提供差分电流的轨对地旁路电容器,并在中点将它们之间的走线接地。 图6 以图形方式对此进行了最佳说明。

图6

上图显示了上部运算放大器提供负载电流,而下部路径吸收负载电流的情况。 在这种情况下,C旁路5 和 C旁路8可以提供部分负载差动电流。 为了防止差分电流流过接地层,我们连接C的接地侧旁路5 和 C旁路8通过电路板信号层上的PCB走线一起,并将该走线在中点(图中的节点A)接地。 对于差分信号,节点A理论上应该是虚拟地,差分电流不应流入接地层(I地=0对于差分负载电流)。 同样,我们放置 C旁路6 和 C旁路7 彼此对称,并在中点处将两个电容器之间的走线接地。 您可以在 中找到应用上述技术的示例布局 此 TI应用报告。

最后,值得一提的是,这些技术也适用于基于全差分运算放大器的ADC驱动器。 有关更多信息,请参阅我上面提到的 TI 文档。

结论

为了从差分ADC驱动器中提取最大线性度性能,我们需要对称的PCB布局。 采用轨到轨旁路电容器作为高频差分电流的主要电荷源可将二次谐波分量降低6至10dB。 我们仍然需要轨对地旁路电容来提供共模电流。 由于这些电容器还可以提供一部分负载差分电流,因此我们需要对称布置它们,以使差分负载电流无法流入接地层。

-

放大器

+关注

关注

146文章

14368浏览量

222709 -

驱动器

+关注

关注

54文章

9125浏览量

156870 -

adc

+关注

关注

100文章

7973浏览量

557327 -

谐波

+关注

关注

7文章

967浏览量

44731 -

PCB

+关注

关注

1文章

2369浏览量

13204

发布评论请先 登录

高速PCB布局:高速差分ADC驱动器轨至轨和轨至地旁路电容器布置方案

高速差分ADC驱动器设计指南(二)

减少差分ADC驱动器谐波失真的PCB布局技术

宽带运算放大器优化高速14位性能差分驱动器PCB布局技术的概述

用于降低差分ADC驱动器谐波失真的PCB布局技术

用于降低差分ADC驱动器谐波失真的PCB布局技术

评论