通过了解同步电路、时钟传输和时钟分配网络,了解时钟偏斜、它是什么及其对现代系统的影响。

现代数字电子产品设计的最大挑战之一是满足时序限制的能力。保持可预测且组织良好的逻辑操作流的一种方法是在数字电路中具有控制良好、定义明确的时序。

时钟偏斜 是这些电路中的一个设计考虑因素,如果不适当考虑,可能会成为重要的故障来源。事实上,在许多情况下,系统的时钟偏差可能是整体系统速度和

时钟频率。要了解时钟偏差,我们必须首先讨论 同步电路。

同步电路和时钟—最小时钟周期计算

大多数现代数字计算机的一个基本特征是同步电路。

同步电路需要一种计时机制来保持有序和周期性的顺序逻辑流。在数字电子产品中,这种计时机制被称为时钟,简单来说,它是一个 方波 频率恒定。

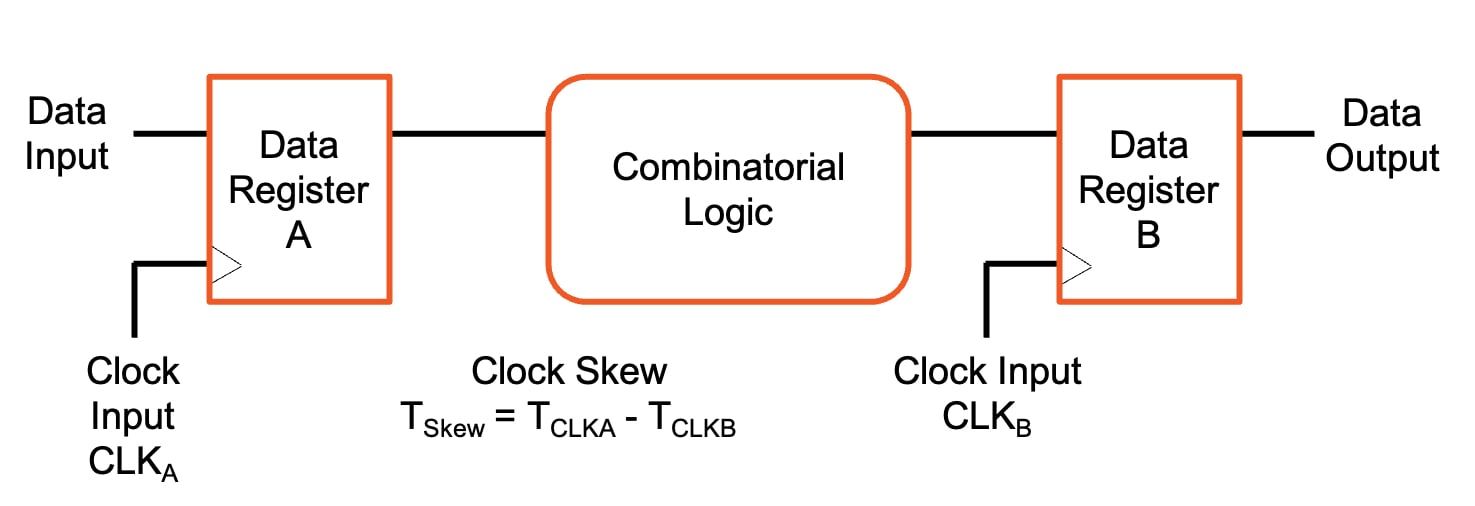

如图1所示,这些电路的工作原理是将静态数据存储在数据寄存器中,旨在锁存数据,直到寄存器遇到时钟的上升(或下降)沿。当时钟边沿发生时,数据从寄存器释放,通过组合逻辑块发送,然后存储在下一个寄存器上。

图1. 具有两个顺序寄存器的数据路径同步电路。

这些操作发生的频率由时钟频率设置,时钟频率由其他几个参数设置。一般方程 最小时钟周期 定义为:

因为 数字逻辑往往是同步电路,所有逻辑块的精确时序对于正确的系统行为至关重要。当您考虑将图1中的设置从一个数据路径扩展到数百万个数据路径(就像实际芯片设计中存在的那样)时,很快就会发现保持所有内容同步是一项不平凡的挑战。

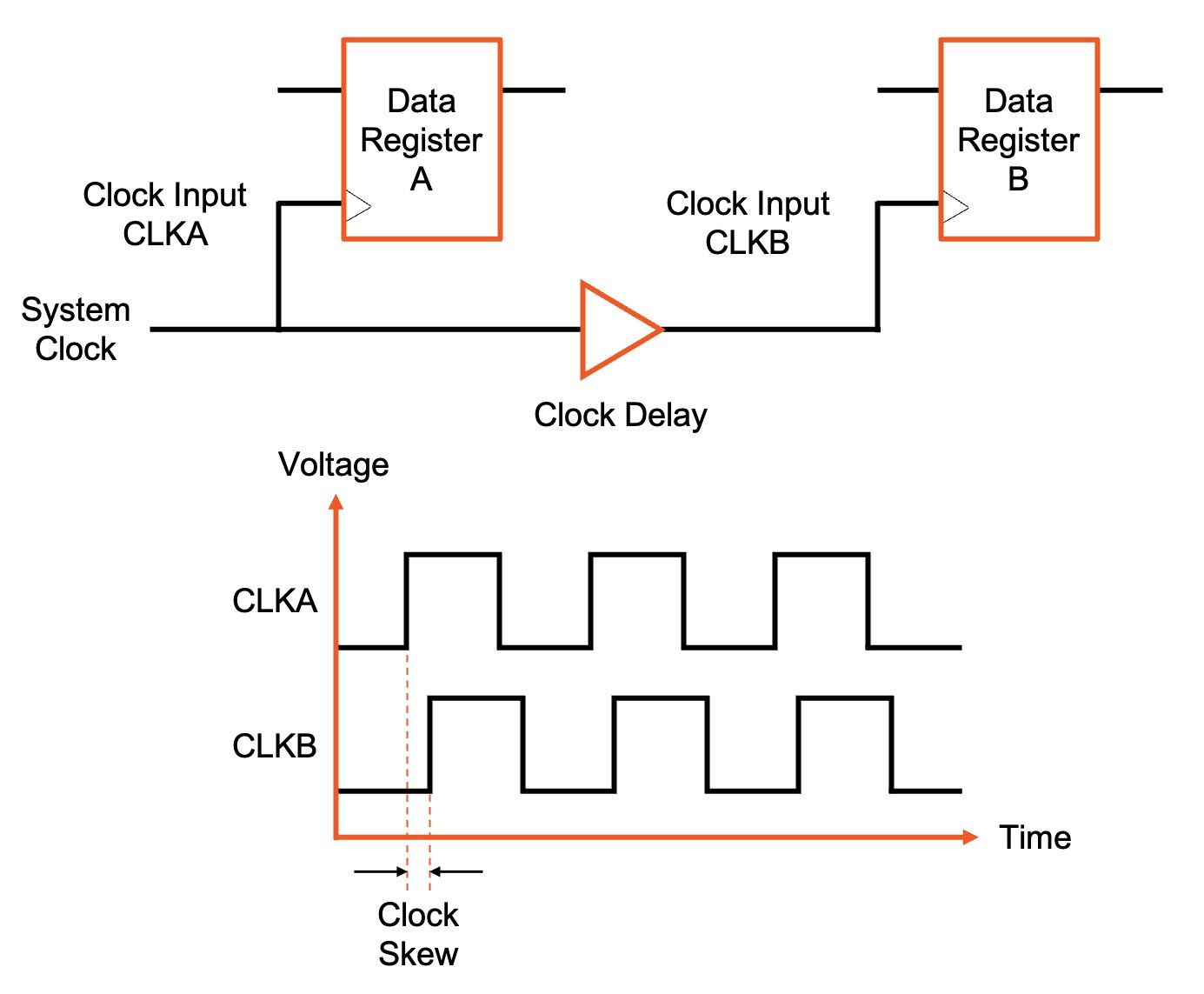

在实践中,时钟信号通常由晶体振荡器产生,馈入锁相环(PLL),并分布在整个IC到系统内的每个逻辑块和晶体管。这种追求中最大的挑战之一是时钟偏斜,它可以定义为顺序相邻寄存器的时钟信号到达时间之间的差异。

这种情况可以用数学定义为:

发生时钟偏斜的传统设置如图2所示,其中时钟分配网络中的延迟导致数据寄存器B比寄存器A晚接收其时钟信号。

图2. 时钟偏斜通过在时钟的传输网络中插入延迟来证明。

如果接收寄存器晚于发送寄存器接收时钟,则偏斜可以定义为正,在相反的情况下,偏斜可以定义为负。时钟偏斜成为数字设计中的一个严重问题,因为它可能违反同步电路所依赖的时序约束。

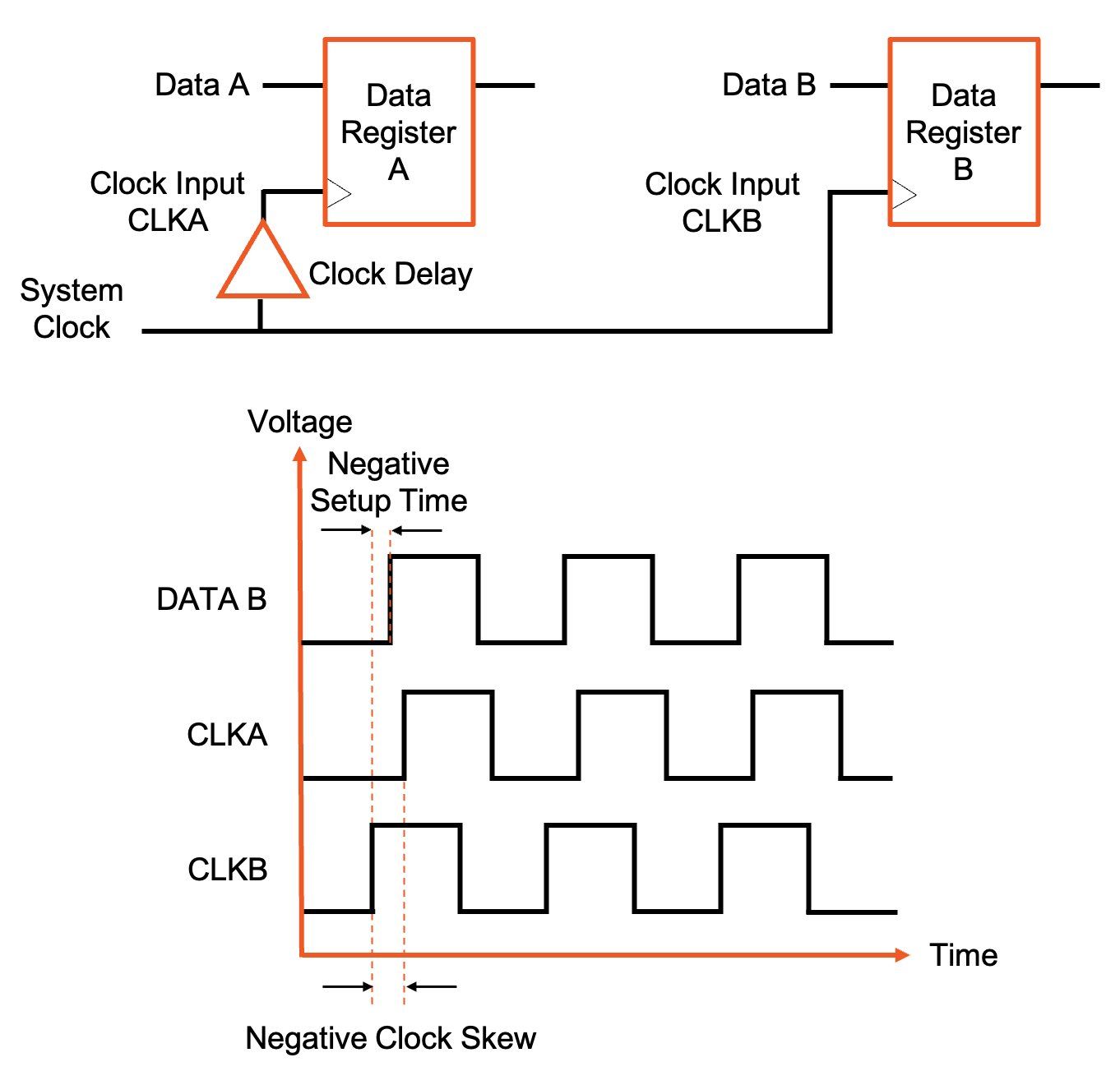

例如,给定恒定的时钟频率和负偏斜,如图3所示,时钟到达接收寄存器B的时间比发送寄存器A早得多。在这种情况下,从发送寄存器发送的数据将在时钟到达后到达接收寄存器。在这里,数据不符合接收寄存器的设置和保持要求(即,在时钟到达时,数据在接收寄存器上不容易获得)。因此,由于接收寄存器无法安全地锁存数据,因此数据将丢失。然后,这个概念将产生复合效应,因为依赖于丢失数据的未来逻辑操作也将失败。

图3. 负时钟偏斜导致数据在其时钟之后到达接收寄存器B。

正如我们在最大时钟频率方程中看到的,时钟偏斜的增加将增加最小时钟周期并降低系统的最大时钟频率。这是因为时钟偏斜有效地增加了排序开销,减少了组合逻辑中可用于有用工作的时间。还值得注意的是,时钟不需要同时交付,但时钟偏斜通常有一个可接受的误差范围。

时钟偏斜的原因

虽然有很多 时钟偏斜的原因,它们最终都归结为时钟分配网络中延迟的差异。

时钟偏斜的一个原因

是时钟分配网络中互连之间的不同长度。如果到两个顺序寄存器的时钟传送路径中的互连长度变化很大,则可能会出现时钟偏斜。沿较短互连行进的时钟将比沿较长互连行进的时钟更快地到达其寄存器。

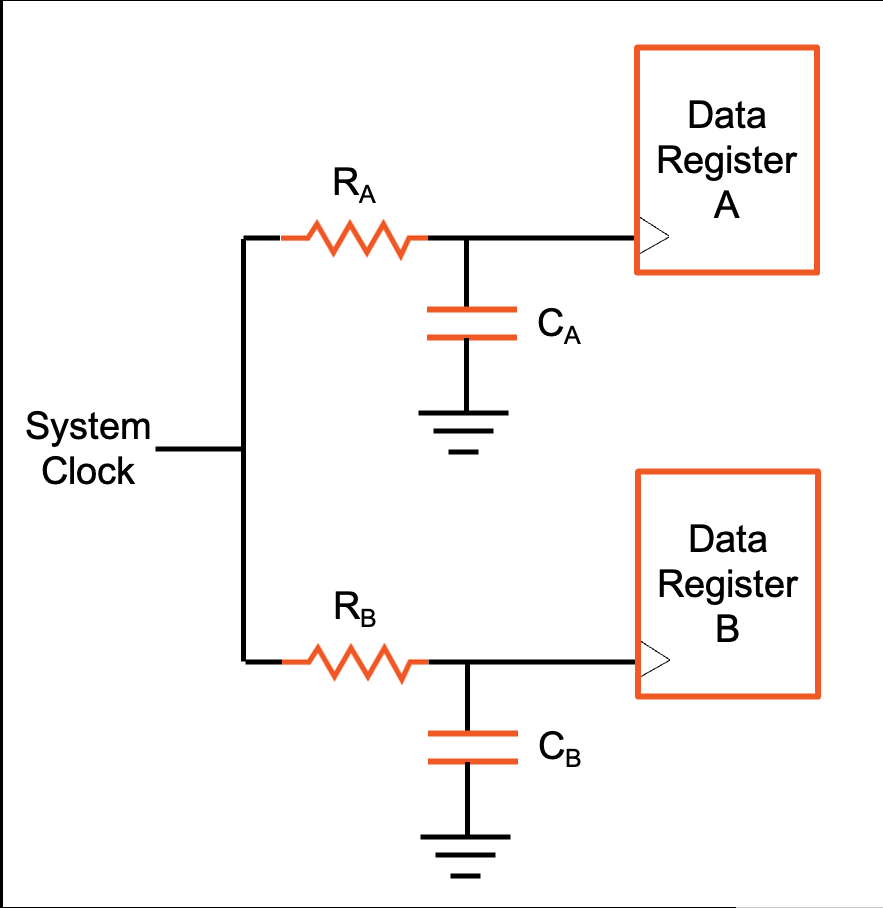

时钟偏差的另一个原因可能是时钟分配网络上互连延迟的差异。即使两条时钟传输路径的长度相同,它们也可能因电阻、电容或电感耦合等寄生效应而经历不同的延迟。在图4的示例中,RC寄生效应的任何差异都将导致寄存器A和B的时钟到达时间的不同延迟。延迟较大的线路上的时钟信号自然会比延迟较小的信号晚到达目的地。将互连设计为具有相同的延迟可能是一项极其困难的任务。

图4. RC寄生效应的变化会导致时钟偏差。

时钟偏斜也可能是由时钟信号的逻辑路径延迟差异引起的。例如,在包含时钟门控的设计中,时钟的传输路径中可能存在额外的门,每个门都有自己的负载电容和传播延迟。如果不均衡,逻辑路径的差异可能会导致时钟交付时间不相等。

其他原因可能包括温度变化、制造变化和材料缺陷。

通过时钟分配网络最大限度地减少时钟偏差

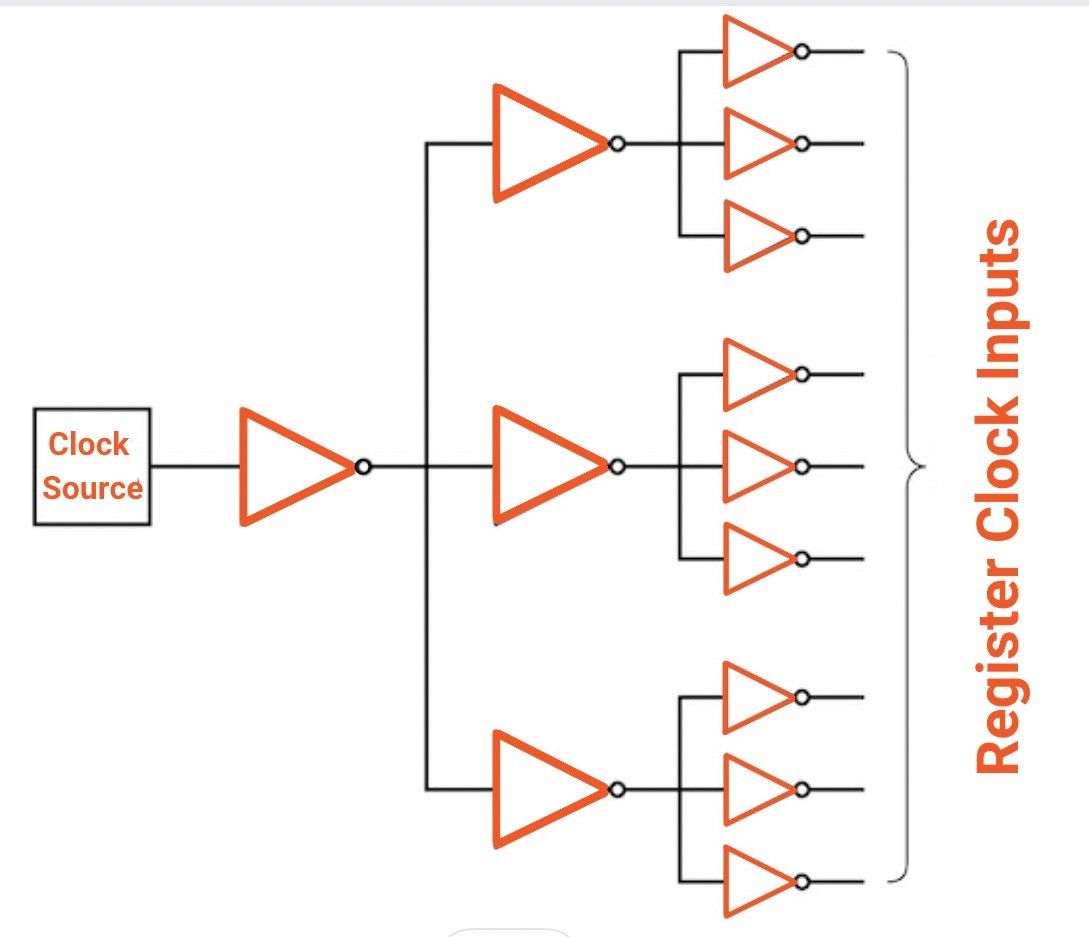

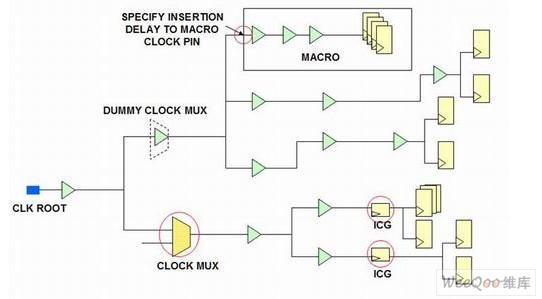

随着时钟频率的增加,时钟偏斜可能成为一个更具挑战性的问题,因为随着时钟频率的增加,误差幅度会显著降低。为了最大限度地减少时钟偏差,复杂的同步电路采用类似于图5所示的时钟分配网络。这些通常也称为时钟树。时钟树中的每个逆变器放大时钟信号以驱动时钟树的下一级。目标是使时钟信号同时到达所有寄存器输入。

图5. 具有并行时钟驱动器的时钟分配网络示例。

对于具有数百万甚至数十亿个晶体管的超大型IC,时钟分配网络可能比图4的简单示例复杂得多。这些网络的创建通常由电子设计自动化(EDA)软件自动处理。工程师输入目标频率、寄存器建立和保持时间限制以及最大时钟偏斜等关键参数。然后,软件生成时钟分配网络以满足目标时序约束。

结论

时钟偏斜是数字集成电路设计中需要考虑的一个重要主题。如果考虑不当,时钟偏差会对系统性能造成严重破坏,导致系统操作不当、数据丢失或成为系统时钟频率的限制因素。

-

电路

+关注

关注

172文章

5909浏览量

172231 -

网络

+关注

关注

14文章

7565浏览量

88765 -

时钟

+关注

关注

10文章

1733浏览量

131474

发布评论请先 登录

相关推荐

时钟向导中是否有一个功能可以指导两个PLL生成没有偏斜的时钟?

如何反转采样时钟信号使其没有任何偏斜?

Astro工具解决ASIC设计时钟偏斜和干扰分析

实现40纳米DSP核心500MHz的频率时钟设计

在PCB设计中如何避免时钟偏斜

测量4通道解串器上的偏斜裕量

时钟抖动和时钟偏斜讲解

CDCM7005-SP高性能、低相位噪声和低偏斜时钟同步器数据表

CDC509高性能、低偏斜、低抖动、锁相环(PLL)时钟驱动器数据表

什么是时钟偏斜?了解时钟分配网络中的时钟偏斜

什么是时钟偏斜?了解时钟分配网络中的时钟偏斜

评论