逻辑综合的含义是什么?

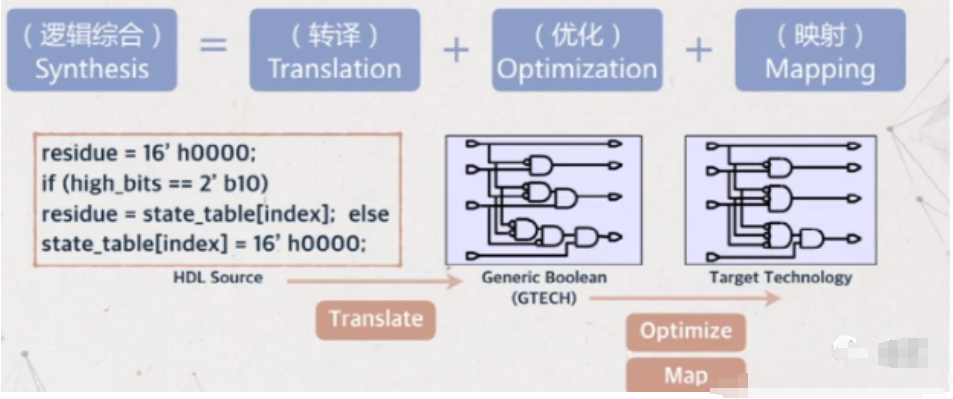

综合(Logic Synthesize)是指将HDL语言、原理图等设计输入翻译成由与、或、非门等基本逻辑单元组成的门级连接(网表),并根据设计目标与要求(约束条件)优化所生成的逻辑连接,输出门级网表文件。RTL级综合指将RTL级源代码翻译并优化为门级网表。

RTL级设计的基本要素和步骤是什么

时钟域描述:描述所使用的所有时钟,时钟之间的主从与派生关系,时钟域之间的转换。

时序逻辑描述(寄存器描述):根据时钟沿的变换,描述寄存器之间的数据传输方式。

组合逻辑描述:描述电平敏感信号的逻辑组合方式与逻辑功能。 书中推荐的设计步骤。

功能定义与模块划分:根据系统功能的定义和模块划分准则划分各个功能模块。

定义所有模块的接口:首先清晰定义每个模块的接口,完成每个模块的信号列表,这种思路与Modular Design(模块化设计方法)一致,利于模块重用、调试、修改。

设计时钟域:根据设计的时钟复杂程度定义时钟之间的派生关系,分析设计中有哪些时钟域,是否存在异步时钟域之间的数据交换;对于PLD器件设计,还需要确认全局时钟是否使用PLL/DLL完成时钟的分频、倍频、移相等功能,哪些时钟使用全局时钟资源布线,哪些时钟使用第二全局时钟资源布线;全局时钟的特点是:几乎没有Clock Skew(时钟倾斜),有一定的Clock Delay(时钟延迟),驱动能力最强;第二全局时钟的特点是:有较小的Clock Shew,较小的Clock Delay,时钟驱动能力较强。

考虑设计的关键路径:关键路径是指设计中时序要求最难以满足的路径,设计的时序要求主要体现在频率、建立时间、保持时间等时序指标上,;在设计初期,设计者可以根据系统的频率要求,粗略的分析出设计的时序难点(如最高频率路径、计数器的最低位、包含复杂组合逻辑的时序路径等),通过一些时序优化手段(如Pipeline、Retiming、逻辑复制等)从代码上缓解设计的时序压力,这种方法比依靠综合与布线工具的自动优化有效的多。

顶层设计:RTL设计推荐使用自顶而下的设计方法,因为这种设计方法与模块规划的顺序一致,而且更有利于进行Modular Design,可以并行开展设计工作,提高模块复用率。

FSM设计:FSM是逻辑设计最重要的内容之一。

时序逻辑设计:首先根据时钟域规划好寄存器组,然后描述各个寄存器组之间的数据传输方式。

组合逻辑设计:一般来说,大段的组合逻辑最好与时序逻辑分开描述,这样更有利于时序约束和时序分析,使综合器和布局布线器达到更好的优化效果。

常用的复位方式有哪些

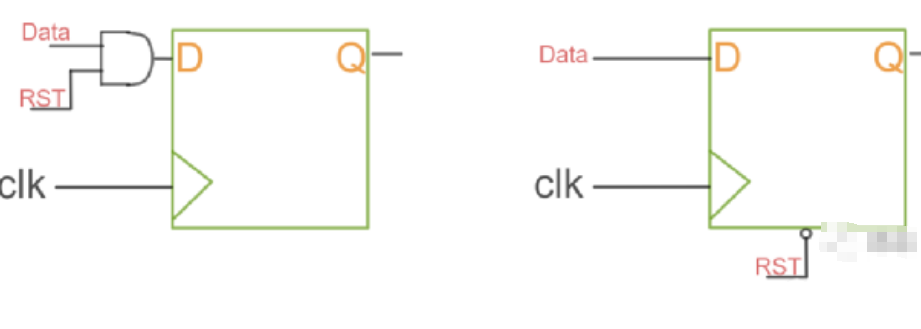

同步复位:当时钟上升沿检测到复位信号,执行复位操作(有效的时钟沿是前提)。always @ ( posedge clk )。优点:有利于仿真器的仿真;可以使所设计的系统成为 100% 的同步时序电路,有利于时序分析,而且可综合出较高的 Fmax;由于只在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的复位毛刺。缺点:复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑诸如 clk skew 、组合逻辑路径延时 、复位延时等因素(所以复位信号有时需要脉冲展宽,用以保证时钟有效期间有足够的复位宽度);由于大多数的逻辑器件的目标库内的 DFF 都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会一方面额外增加FPGA内部的逻辑资源,另一方面也增加了相应的组合逻辑门时延。

异步复位它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。always @ ( posedge clk or negedge rst_n );优点:大多数目标器件库的 DFF 都有异步复位端口,那么该触发器的复位端口就不需要额外的组合逻辑,这样就可以节省资源;设计相对简单;异步复位信号识别方便(电路在任何情况下都能复位而不管是否有时钟出现)。缺点:最大的问题在于它属于异步逻辑,问题出现在复位释放时,而不是有效时,如果复位释放接近时钟有效沿,则触发器的输出可能进入亚稳态(此时 clk 检测到的 rst_n 的状态就会是一个亚稳态,即是0是1是不确定的),从而导致复位失败。可能因为噪声或者毛刺造成虚假复位信号(比如以前的游戏机玩到一半突然复位)(注意:时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题);静态时序分析比较困难。对于 DFT设计,如果复位信号不是直接来自于 I/O 引脚,在 DFT 扫描和测试时,复位信号必须被禁止,因此需要额外的同步电路。

为什么推荐使用异步复位同步释放

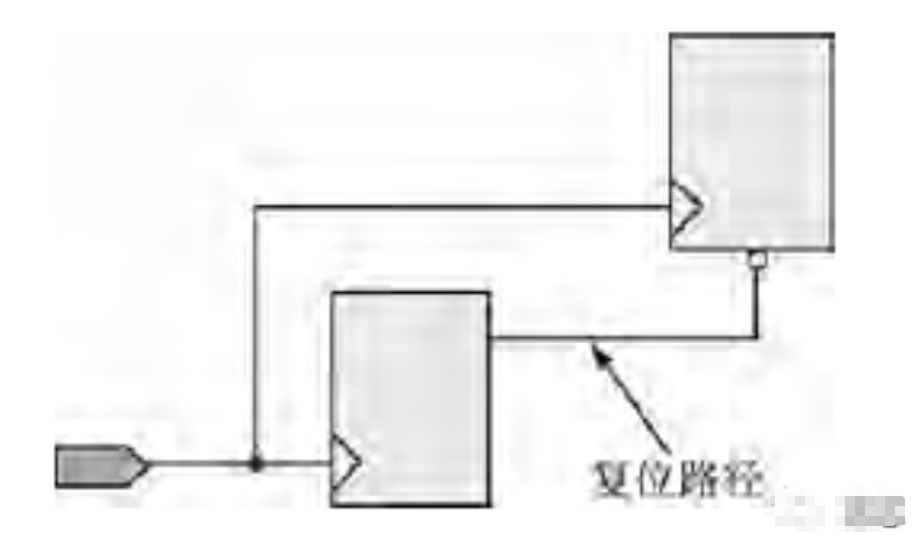

推荐的复位电路设计方式是异步复位,同步释放。同步释放的意思就是在正式进入func模式时在寄存器前面多打一拍,这样可以规避亚稳态风险。异步复位就是复位信号可以直接不受时钟信号影响,在任意时刻只要是低电平就能复位,即复位信号不需要和时钟同步。同步释放让复位信号取消的时候,必须跟时钟信号同步,即刚好跟时钟同沿。

复位的主要目的是使芯片电路进入一个已知的,确定的状态。主要是触发器进入确定的状态。在一般情况下,芯片中的每个触发器都应该是可复位的。

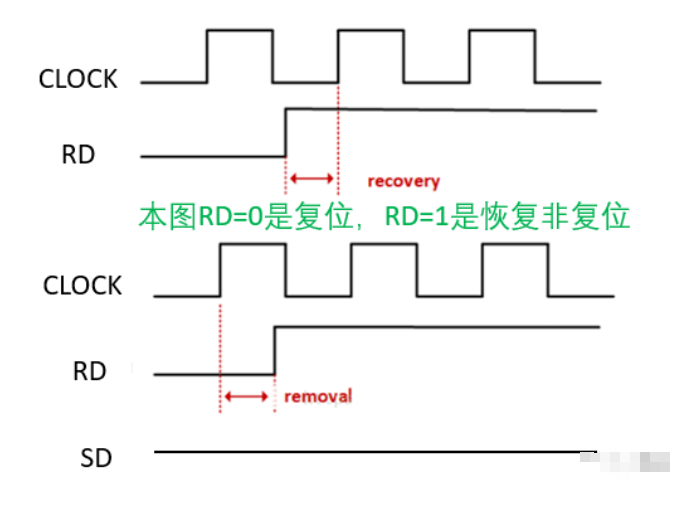

recovery time即恢复时间,撤销复位时,恢复到非复位状态的电平必须在时钟有效沿来临之前的一段时间到来,才能保证时钟能有效恢复到非复位状态,此段时间为recovery time。类似于同步时钟的setup time。这个针对是本周期的RD的“恢复到非复位状态的电平”。

什么是RTL建模

此级别的建模使用编程语句和运算符表示数字功能。RTL模型是功能模型,不包含有关如何在硅中实现该功能的详细信息。由于这种抽象,复杂的数字功能可以比在详细的门级更快速、更简洁地建模。RTL模型的仿真速度也大大快于门级和开关级模型,这使得验证更大、更复杂的设计成为可能。

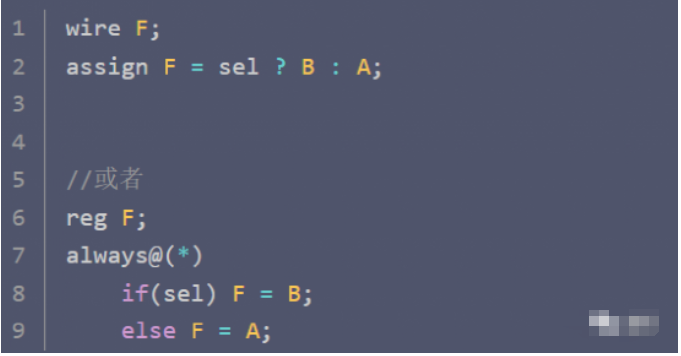

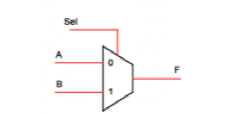

例如二选一选择器的RTL模型:

对应的门级电路是:

-

寄存器

+关注

关注

31文章

5343浏览量

120349 -

HDL

+关注

关注

8文章

327浏览量

47383 -

RTL

+关注

关注

1文章

385浏览量

59784 -

复位电路

+关注

关注

13文章

322浏览量

44594 -

时序逻辑

+关注

关注

0文章

39浏览量

9163

发布评论请先 登录

相关推荐

RTL级设计的基本要素和步骤是什么

RTL级设计的基本要素和步骤是什么

评论