作者:Colm Slattery and Mick McCarthy

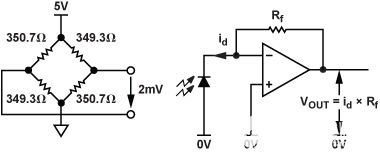

在电子工业中,测量具有宽动态范围的信号的需求非常普遍,但当前的技术通常难以满足实际的系统要求。称重系统通常使用称重传感器桥式传感器,其最大满量程输出为1 mV至2 mV。此类系统可能需要1,000,000:1的分辨率,当以2 mV输入为参考时,需要高性能、低噪声、高增益放大器和Σ-∆调制器。同样,医疗应用的化学和血液分析通常使用光电二极管传感器,产生非常小的电流,需要精确测量(见图1)。通常使用低噪声跨阻放大器,具有多级增益和后处理。

图1.称重传感器和光电二极管应用的输入。

虽然实际传感器数据通常只占输入信号范围的一小部分,但系统通常必须设计为处理故障条件。因此,宽动态范围、小输入的高性能以及对快速变化信号的快速响应是关键要求。一些应用,如振动监测系统,同时包含交流和直流信息,因此精确监测小信号和大信号的能力变得越来越重要。

这些要求要求灵活的信号调理模块具有低噪声输入、相对较高的增益,并且能够在不影响性能的情况下动态改变增益以响应输入电平变化,同时仍保持宽动态范围。现有的Σ-∆技术可以提供许多应用所需的动态范围,但代价是更新速率。本文介绍一种替代方法,该方法使用高速逐次逼近采样ADC,并结合自动量程可编程增益放大器(PGA)前端。增益根据模拟输入值自动变化,它使用过采样将系统的动态范围增加到126 dB以上。

科技

在ADC应用中,动态范围是满量程均方根值与均方根噪声之比,通常在模拟输入短路时测量。通常以分贝表示(dBV = 20 × log10电压比),它表示ADC可以解析的信号幅度范围;动态范围为60 dB的ADC可以分辨1000:1范围的信号幅度。对于N位ADC,动态范围(DR)的计算公式为:

DR = 6.021N + 1.763 dB

Σ-∆ADC(如AD7767)通过将Σ-∆调制器与数字后置处理器相结合,可实现出色的动态范围。转换器之后的数字滤波可消除带外量化噪声,但也降低了fMCLK,在过滤器的输入处,到fMCLK/8,fMCLK/16,或fMCLK/32,在数字输出端 — 取决于所使用的设备型号。为了增加动态范围,可以添加低噪声PGA来调节输入信号以达到满量程。系统的本底噪声将主要由前端PGA的输入噪声主导,具体取决于增益设置。如果信号太大,则会超出ADC输入的量程。如果信号太小,它会在转换器的量化噪声中丢失。Σ-∆ADC通常用于需要较低系统更新速率的应用。

过采样逐次逼近型ADC,改善动态范围

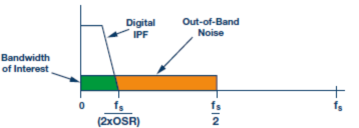

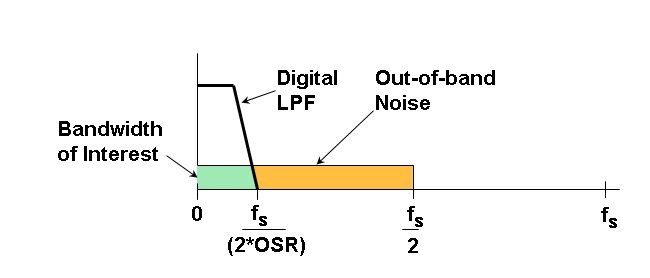

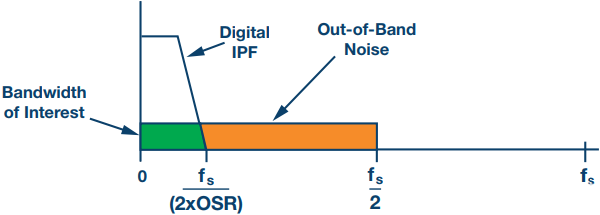

增加逐次逼近型ADC动态范围的一种方法是实现过采样:以远高于奈奎斯特频率的速率对输入信号进行采样的过程。一般来说,采样频率每增加一倍,噪声性能就会提高约3 dB(见图2)。过采样可以使用后处理技术以数字方式实现。AD7606等部分ADC具有可编程过采样速率,使最终用户能够选择合适的过采样比。

图2.过采样可降低噪声。

将 PGA 功能与过采样相结合

为了实现最大动态范围,可以添加前端PGA级,以提高非常小信号输入的有效信噪比(SNR)。考虑>126 dB的系统动态范围要求。首先,计算最小均方根噪声以实现此动态范围。例如,3 V输入范围(6 V p-p)的满量程均方根值为2.12 V(6/2√2)。最大允许系统噪声计算公式为

126 dB = 20 对数(2.12 V/rms 噪声))

因此,均方根噪声≈1 μV rms。

现在,考虑系统更新速率,它将确定过采样率和最大噪声量,参考输入(RTI),这是系统中可以容忍的。例如,当AD7985 16位、2.5 MSPS PulSAR ADC以600 kSPS(11 mW耗散)和72的过采样比运行时,输入信号的带宽限制为约4 kHz。总均方根噪声只是噪声密度(ND)乘以√f),因此最大允许输入频谱噪声密度(ND)可以计算为:®

1 μV rms = ND × √4 kHz

或者,ND = 15.5 nV/√Hz

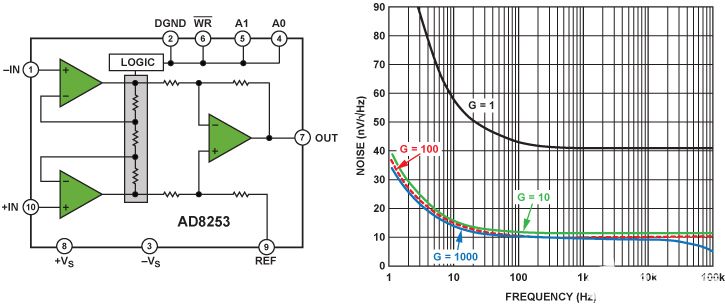

根据RTI系统输入噪声的品质因数,可以选择合适的仪表放大器,该仪表放大器将提供足够的模拟前端增益(与ADC的SNR相加时,并伴有相关的过采样),以实现所需的126 dB。对于AD7985,典型SNR值为89 dB,过采样72可再提高~18 dB(72约为26,每加倍增加 3 dB)。实现126 dB DR仍需要20 dB以上的改进,这可来自模拟PGA级提供的增益。仪表放大器必须提供≥20的增益(或不超过15.5 nV/√Hz噪声密度规格)。AD8253是一款10 MHz、20 V/μs、G = 1、10、100、1000 iCMOS可编程增益仪表放大器,是一款不错的产品;它具有一个低噪声、10 nV/√Hz输入级,增益为100,适用于所需带宽,如图3所示。®

图3.AD8253仪表放大器:框图和噪声频谱密度。

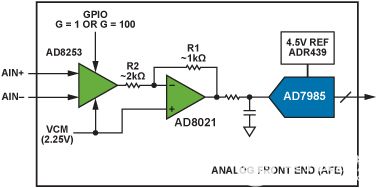

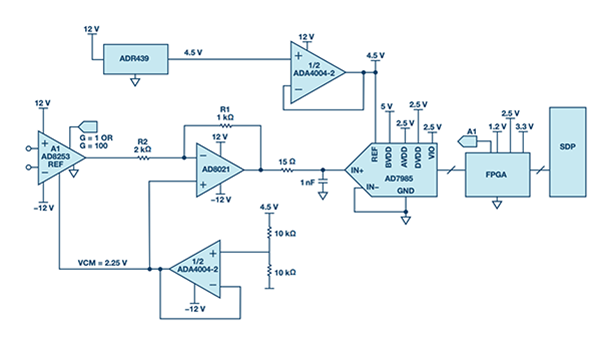

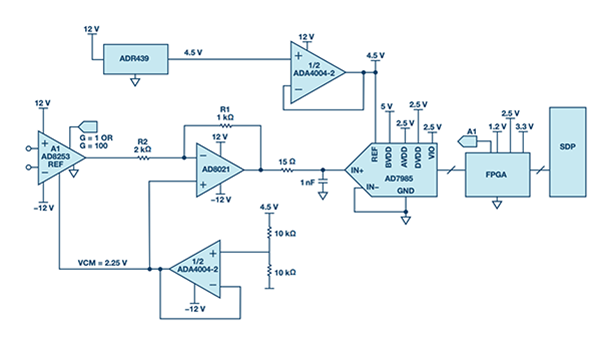

实现前端PGA增益和ADC过采样的系统级解决方案如图4所示。AD8021是一款2.1 nV/√Hz低噪声、高速放大器,能够驱动AD7985。它还对AD8253输出进行失调和衰减。AD8253和AD8021均采用外部共模偏置电压工作,这些电压结合在一起可在ADC输入端保持相同的共模电压。

图4.低噪声宽带模拟前端。

由于整个系统的噪声预算最大为15 nV/√Hz(参考输入(RTI),因此计算每个模块的主要噪声源以确保不超过15 nV/√Hz硬限值非常有用。AD8021折合到输入端的噪声规格为<3 nV/√Hz,当折合到增益为100 AD8253级的输入端时,可以忽略不计。AD7985的额定SNR为89 dB,采用外部4.5 V基准电压源,噪声分辨率为<45 μV rms。考虑到ADC的奈奎斯特带宽为300 kHz,它将在该带宽上贡献~83 nV/√Hz。当参考AD7985的输入时,其<1 nV/√Hz在系统中可以忽略不计,其中RTI噪声源使用平方和根计算求和。

使用AD8253的另一个好处是它具有数字增益控制功能,允许系统增益根据输入变化动态变化。这是利用系统的数字信号处理能力智能实现的。

本应用中数字处理的主要功能是利用AD7985 16位转换结果产生更高分辨率的输出。这是通过抽取数据并根据输入幅度自动切换模拟输入增益来实现的。这种过采样导致输出数据速率低于ADC采样速率,但动态范围大大增加。

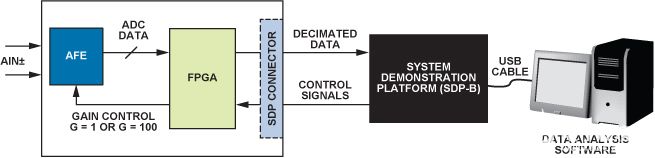

为了对该应用的数字端进行原型设计,使用了现场可编程门阵列(FPGA)作为数字内核。为了快速调试系统,模拟电路和FPGA被整合到一个电路板中,如图5所示,使用系统演示平台(SDP)连接器标准,允许USB轻松连接到PC。SDP 是可重复使用的硬件和软件的组合,允许通过最常用的组件接口轻松控制和捕获硬件。

图5.在具有 FPGA、SDP 和 PC 的系统中使用模拟前端 (AFE)。

基本控制流程如下:

上电后,执行零点校准操作。AD8253的差分模拟输入短路至地,AD7985在每个增益设置下执行转换。ADC 值被存储起来供以后使用。

校准后,FPGA以预设速率向AD7985提供周期性转换启动信号,在本例中约为600 kSPS。每个ADC结果被读入FPGA,并传递到抽取和增益模块。

增益模块查看当前ADC结果、上一个ADC结果和电流增益设置,并确定下一个ADC转换最合适的增益设置。此过程详述如下。

抽取模块接收每个ADC样本、该样本的当前PGA增益设置以及过程早期存储的校准值。收到72个ADC样本后,23位输出结果是72个样本的平均值,并考虑了失调和增益。

然后将此23位结果转换为二进制补码,并以与Blackfin串行端口(SPORT)兼容的格式从FPGA接收,并由SDP-B硬件捕获。然后每72个ADC采样后用一个新词重复该过程。

FPGA中实现的两个关键模块是抽取器和增益计算器。以下是每个块的详细说明。

抽取器

此块具有管理一些顺序数据处理步骤的内部状态机:

每个单独的AD7985样本都归一化为相同的尺度。例如:AD7985的4 mV输入,采用4.5 V基准电压源时,给出一个代码(4 mV/4.5 V × 65535)= 58,G = 1。G = 100时,ADC在输入端看到400 mV,输出代码为5825。对于模拟前端(AFE)增益为1的ADC样本,当AFE增益为100时,必须将样本乘以100以抵消缩放效应。这可确保无论AFE增益设置如何,都可以正确平均和抽取这些样本。

使用抽取器功能后,可以对模拟输入进行初始测试。

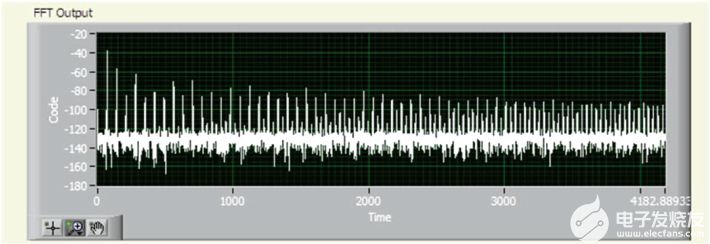

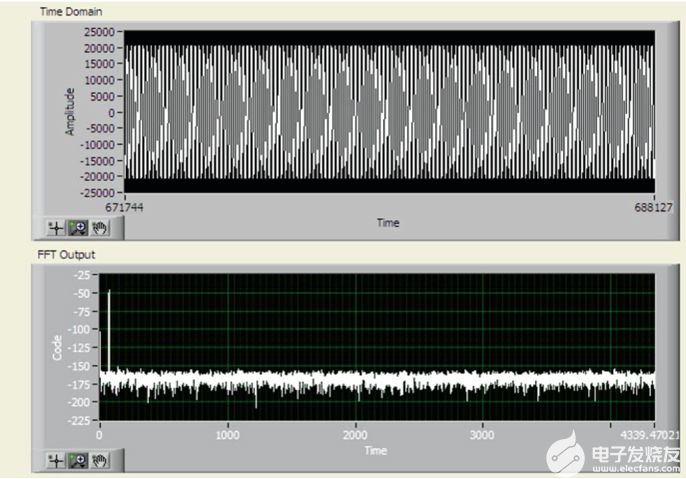

输入短路后,可以在高增益直流模式下测试系统(见图6)。

图6.输入短路时进行系统高增益直流模式噪声测试。

结果表明,峰峰值噪声为6位,均方根噪声为0.84 LSB @ 16位 = 0.654 μV rms。对于2.12 V rms满量程范围,动态范围可计算为

DR = 20 日志10(满量程/均方根噪声)= ~130 dB

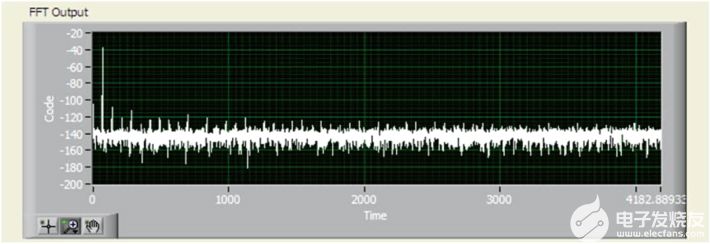

因此,系统可以轻松满足有关噪声的动态范围目标。使用50 mV p-p交流模拟输入进行测试时,在频域中观察到明显的失真(见图7)。此特定输入幅度突出了系统最坏情况 - 当交流输入幅度略大于增益 = 100 模式处理的范围时,系统定期在两种模式之间切换。增益门限的选择也会加剧这种范围切换效应,如下所述。每种增益模式下失调之间的不匹配将显示为粗谐波失真,因为计算出的输出代码会跳转每个范围内失调之间的差值。

图7.最差情况下的输入幅度,无需校准。

简单地校准每个增益范围内的零点偏移可以显著减少信号失真。事实上,仅校准就可以将谐波降低约50 dB,如图8所示。即使是最坏情况下的输入音,谐波也已降至–110 dB FS电平。

图8.带校准的最差情况输入幅度。

校准后的偏移从归一化样品中去除。由于校准是在两种增益设置下执行的,因此去除的失调取决于获取ADC采样时的增益。

归一化和失调校正的样本被添加到累加器寄存器中,该寄存器在上电时复位,每次接收到72个样本时。当收到 72 个样本并将其添加到累加器时,总和将传递到除法器,除法器将累加器中的值除以 72 以产生 23 位平均结果。设置输出标志以指示除法已完成并且新结果已准备就绪。

增益设置

该模块根据电流增益设置、两个原始ADC样本和一些硬编码阈值数字输出新的增益设置。系统中使用四个阈值;选择这些阈值对于最大化系统的模拟输入范围至关重要,确保G = 100模式用于尽可能多的信号范围,同时防止ADC输入超量程。请注意,此增益模块作用于每个原始ADC结果,而不是已归一化的数据。考虑到这一点,可以在这样的系统中使用的一些阈值的说明性示例(假设中间量程为零的双极系统)如下:

T1(正下限阈值):+162(中量程以上 162 个代码) T2(负下限阈值):–162(低于中量程 162 个代码) T3(正上限阈值):+32,507(低于正满量程 260 个代码) T4(负上限阈值):–32,508(负满量程以上 260 个代码)

在 G = 1 模式下,使用内部极限 T1 和 T2。当实际ADC结果介于T1和T2之间时,增益切换为G = 100模式。这可确保ADC接收的模拟输入电压尽快最大化。

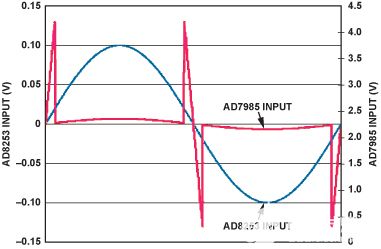

在G = 100模式下,使用外部极限T3和T4。如果预测ADC结果高于T3或低于T4,则增益切换到G = 1模式,以防止ADC输入超量程(见图9)。

图9.当预测ADC输入超出阈值限值时,从放大器输入到转换器输入的增益降低100。(蓝线:放大器输入;红线:转换器输入。

在G = 100模式下,如果算法预测下一个ADC样本将刚好超出外部阈值(使用非常基本的线性预测),给出+32,510的ADC结果,则增益切换到G = 1,而不是+32,510,下一个ADC结果是+325。

在这样的系统中,为了防止颤振(在阈值附近快速重复增益切换),迟滞(100:1和1至100开关电平的分离)对于确定正确的阈值限值非常重要。在本例中使用的实际限值的计算中,内置了显著的滞后。如果系统从高增益(G = 100)模式切换到低增益(G = 1)模式,系统的模拟输入电压必须降低近50%才能恢复到高增益模式。

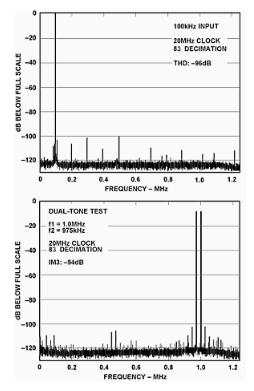

全系统性能

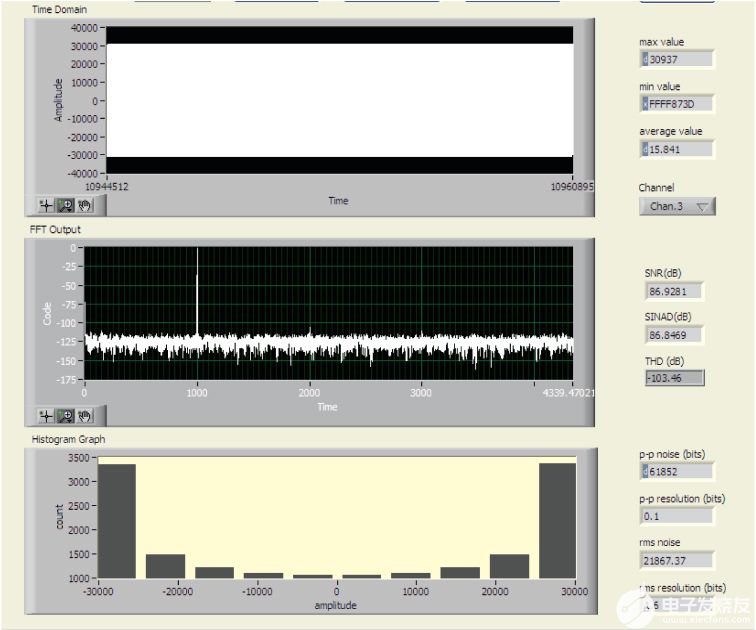

借助完全优化的增益和抽取算法,整个系统已准备就绪,可以进行测试。图10显示了系统对以1 kHz运行的–0.5 dBFS大信号输入音的响应。当考虑到100的PGA增益时,实现的动态范围为127 dB。

图 10.对大规模 1kHz 信号的响应。

同样,在图11中测试小信号输入时,在–46.5 dBFS时输入音为70 Hz,可实现高达129 dB的动态范围。在较小的输入音调下,性能有望得到改善,因为在此测量期间不会发生增益范围的有源切换。

图 11.对 70 Hz 时的小量程输入信号的响应。

结论

系统的性能依赖于动态切换增益以处理小信号和大信号输入的能力。虽然∑-∆技术提供了出色的动态范围,但基于SAR的解决方案提供了一种根据输入信号动态改变前端增益的方法,而不会影响系统性能。这允许实时测量小信号和大信号交流和直流输入,而无需等待系统建立时间或由于延迟增益变化而产生大毛刺。

该系统的关键是ADC过采样技术与预测增益设置算法相结合。增益算法的关键是如何处理输入信号的压摆率。对于更高的输入压摆率,可能需要自定义增益设置,以便更快地响应接近ADC输入可能超量程电平的信号。这可以通过收紧所使用的阈值或使用多个样本而不是本例中描述的两个样本对输入信号进行更复杂的预测分析来实现。相反,在输入压摆率非常低的系统中,可以加宽门限,以更好地利用高增益模式,而不会使ADC输入过量程。

虽然本文介绍AD7985 ADC,但所使用的技术也适用于ADI公司的其他高速转换器。使用更快的ADC采样速率,最终用户可以用增加的输入带宽和更快的输出数据速率换取更高的过采样率,从而实现更大的动态范围。

利用AD8253 VGA的额外增益范围,而不仅仅是G = 1和G = 100,可以进一步将增益变化的影响降至最低。在本例中,切换增益时会引入少量失真。但是,如果使用G = 10范围,对于带有额外校准点的三步增益,可以实现更好的系统THD规格。

-

放大器

+关注

关注

146文章

14362浏览量

222470 -

adc

+关注

关注

100文章

7946浏览量

556872 -

pga

+关注

关注

1文章

115浏览量

42455

发布评论请先 登录

过采样技术如何提高ADC的动态性能

基于Kinetis K系列16位ADC PGA的分析与应用

采用Δ-Σ和SAR ADC的过采样模式提升ADC动态范围

16位SAR转换器应用能否在600 kSPS时达到125 dB的动态范围

采用PGA的SAR转换器可实现125 dB的动态范围

CN0260 采用PGA的过采样SAR ADC,可实现125 dB以上的动态范围

用于高动态范围的ADC,逐次逼近还是Σ-Δ

过采样ADC和PGA相结合提供127dB动态范围

过采样ADC和PGA相结合提供127dB动态范围

评论