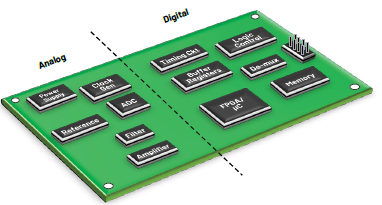

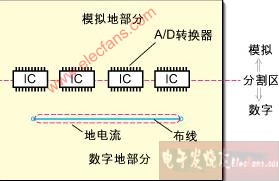

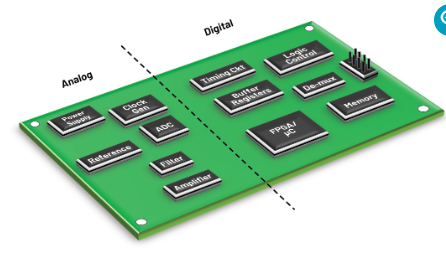

本应用笔记提供了RF印刷电路板(PCB)设计和布局的指南和建议,包括对混合信号应用的一些讨论,例如同一PCB上的数字、模拟和RF元件。该材料按主题领域排列,并提供“最佳实践”指导。它应与可能适用于特定组件的所有其他设计和制造指南结合使用, PCB 制造商, 和材料组(如适用)。

射频传输线

ADI公司的许多RF元件都需要受控阻抗传输线,该传输线将RF功率传输到PCB上的IC引脚(或从PCB引脚传输)。这些传输线可以在外层(顶部或底部)上实现,也可以埋在内层中。这些传输线的指南包括与微带、悬挂带状线、共面波导(接地)和特性阻抗相关的讨论。它还描述了传输线弯曲和拐角补偿,以及传输线的层变化。

微带

这种类型的传输线由固定宽度的金属布线(导体)以及位于正下方(相邻层)的坚固不间断接地层组成。例如,第 1 层(顶部金属)上的微带需要第 2 层上的实心接地层(图 1)。布线宽度、介电层厚度和电介质类型决定了特性阻抗(通常为50Ω或75Ω)。

图1.微带示例(等轴测视图)。

悬挂带状线

该线路由内层上的固定宽度布线组成,中心导体上方和下方具有实心接地层。导体可以位于接地层之间的中间(图 2),也可以偏移(图 3)。这是在内层上进行射频路由的适当方法。

图2.悬挂带状线(端视图)。

图3.偏移悬挂带状线。带状线的一种变体,用于层厚度不等的 PCB(端视图)。

共面波导(接地)

共面波导可在附近的RF线以及其他信号线(端视图)之间提供更好的隔离。该介质由中心导体组成,其两侧和下方都有接地层(图 4)。

图4.共面波导可在附近的RF线和其他信号线之间提供更好的隔离。

建议在共面波导的两侧设置过孔“围栏”,如图5所示。此顶视图提供了中心导体两侧每个顶部金属平面上的一排接地过孔的示例。顶层感应的返回电流短路至底层接地层。

图5.建议在共面波导的两侧使用过孔围栏。

特性阻抗

有几种计算器可用于正确设置信号导体线宽以实现目标阻抗。但是,在输入层的介电常数时应小心。典型PCB的外层压层通常比电路板的芯含有更少的玻璃含量, 因此介电常数较低.例如,FR4 核心通常作为εR= 4.2,而外层压板(预浸料)层通常εR= 3.8。下面给出的示例仅供参考,假设金属厚度为1盎司铜(1.4密耳,0.036毫米)。

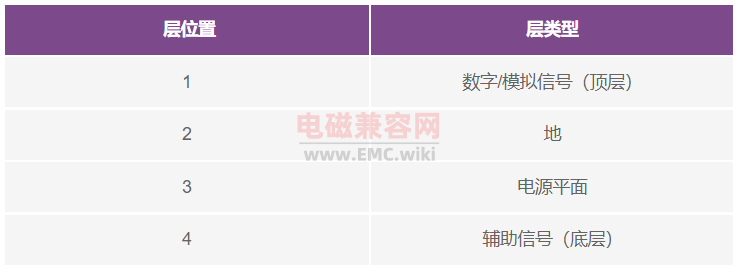

| 媒体 | 电介质 | 层厚(密耳) | 中心导体,单位为密耳(毫米) | 差距 | 特性阻抗 |

| 微带 | 预浸料 (3.8) | 6 (0.152) | 11.5 (0.292) | 不适用 | 50.3 |

| 10 (0.254) | 20 (0.508) | 50.0 | |||

| 差分对 | 预浸料 (3.8) | 6 (0.152) | 25 (0.635) | 6 (0.152) | 50.6 |

| 带状线 | FR4 (4.5) | 12 (0.305) | 3.7 (0.094) | 不适用 | 50.0 |

| 偏移带状线 |

预浸料 (3.9) |

6 (0.152) 上, |

4.8 (0.122) |

不适用 |

50.1 |

| 低 10 (0.254) | |||||

| 共面工作组 |

预浸料 (3.8) |

6 (0.152) | 14 (0.35) | 20 (0.50) | 49.7 |

传输线弯曲和拐角补偿

当传输线由于布线约束而需要弯曲(改变方向)时,请使用至少为中心导体宽度 3 倍的弯曲半径。换句话说:

弯曲半径≥ 3 ×(线宽)。

这将最大限度地减少通过弯曲的任何特性阻抗变化。

在无法逐渐弯曲的情况下,传输线可以进行直角弯曲(非弯曲)。参见图 6。但是,必须对此进行补偿,以减少由于通过弯曲的有效线宽的局部增加而导致的阻抗不连续性。标准补偿方法是斜接,如下图所示。最佳微带直角斜接由杜维尔和詹姆斯的公式给出:

其中 M 是斜接与未斜接折弯相比的分数 (%)。该公式与介电常数无关,并且受w/h≥0.25的约束。

其他传输线也可以采用类似的方法。如果正确补偿存在任何不确定性,如果设计需要高性能传输线,则应使用电磁模拟器对弯曲进行建模。

图6.当无法弯曲时,传输线可以进行直角弯曲。

传输线的层更改

当布局限制要求传输线移动到不同的层时,建议每个过渡至少使用两个通孔,以最小化过孔电感负载。一对过孔将有效降低50%的过渡电感,并且应使用与传输线宽度兼容的最大通孔直径。例如,在 15 密耳微带生产线上,将使用 15 密耳至 18 密耳的通孔直径(成品电镀直径)。如果空间不允许使用较大的过孔,则应使用三个直径较小的过渡过孔。

信号线隔离

必须注意防止信号线之间的意外耦合。一些潜在的耦合和预防措施的例子:

射频传输线:线路应尽可能保持距离,并且不应在近距离布线以延长距离。平行微带线之间的耦合将随着间距的减小和平行布线距离的增加而增加。在单独层上交叉的线应具有使它们分开的接地平面。承载高功率水平的信号线应尽可能远离所有其他线路。接地共面波导可在线路之间提供出色的隔离。在小型PCB上实现优于约-45dB的RF线路之间的隔离是不切实际的。

高速数字信号线:这些线应分别布线在与RF信号线不同的层上,以防止耦合。数字噪声(来自时钟、PLL等)可以耦合到RF信号线上,并且可以调制到RF载波上。或者,在某些情况下,数字噪声可以上/下变频。

V抄送/电源线:这些应在专用层上布线。应在主V处提供足够的去耦/旁路电容抄送分布节点,以及 V 处抄送分支。旁路电容的选择必须基于RF IC的整体频率响应,以及时钟和PLL的任何数字噪声的预期频率分布特性。这些线路还应与任何将传输大量RF功率的RF线路分开。

地面平面

建议的做法是在第 2 层使用实心(连续)接地层,假设第 1 层用于射频组件和传输线。对于带状线和偏移带状线,需要在中心导体上方和下方的接地层。这些平面不得共享或分配给信号或电源网络,但必须唯一地分配给地面。层上的部分接地层(有时由于设计约束而需要)必须位于所有RF组件和传输线的基础。接地层不得在传输线布线下断开。

层之间的接地通孔应在整个PCB的RF部分自由添加。这有助于防止由于接地电流返回路径而产生寄生接地电感。过孔还有助于防止来自PCB上的RF和其他信号线的交叉耦合。

偏置和地层的特殊考虑

分配给系统偏置(直流电源)和接地的层必须根据元件的返回电流来考虑。一般的指导是不要在偏置层和接地层之间的层上路由信号。

图7.层分配不正确:偏置层和接地层上的接地电流返回路径之间存在信号层。偏置线噪声可以耦合到信号层。

图8.更好的层分配:偏置层和接地返回层之间没有信号层。

电源(偏置)路由和电源去耦

一种常见的做法是,如果一个组件有多个电源连接,则对电源路由使用“星形”配置(图 9)。较大的去耦电容(数十μFds)安装在星形的“根部”,较小的电容安装在每个星形分支上。后一种电容器的值取决于RF IC的工作频率范围及其特定功能(即级间与主电源去耦)。下面显示了一个示例。

图9.如果一个组件有多个电源连接,则电源路径可以按星形配置排列。

“星形”配置避免了长接地返回路径,如果连接到同一偏置网络的所有引脚都串联,则会导致长接地返回路径。较长的接地返回路径会产生寄生电感,从而导致意外的反馈环路。电源去耦的关键考虑因素是,直流电源连接必须电气定义为交流接地。

去耦或旁路电容器的选择

实际电容器由于其自谐振频率(SRF)而具有有限的有效频率范围。SRF 可从制造商处获得,但有时必须通过直接测量来表征。在SRF上方,电容是电感性的,因此不会执行去耦或旁路功能。当需要宽带去耦时,标准做法是使用几个尺寸(电容)不断增加的电容器,所有电容器都并联连接。较小值的电容器通常具有较高的SRF(例如,SRF = 14GHz的0402 SMT封装中的0.2pF值),而较大的值具有较低的SRF(例如,SRF = 4GHz的同一封装中的2pF值)。典型排列如表2所示。

| 元件 | 电容 | 包 | 战略成果框架 | 有效频率范围* |

| 超高范围 | 20pF | 0402 | 2.5千兆赫 | 800兆赫至 2.5兆赫 |

| 非常高的范围 | 100pF | 0402 | 800兆赫 | 250兆赫至800兆赫 |

| 高范围 | 1000pF | 0402 | 250兆赫 | 50兆赫至 250兆赫 |

| 中档 | 1μF | 0402 | 60兆赫 | 100kHz 至 60MHz |

| 低范围 | 10μF | 0603 | 600千赫 | 10kHz 至 600kHz |

| *有用频率范围的低端定义为小于5Ω的容抗。 | ||||

旁路电容布局注意事项

由于电源线必须为交流接地,因此必须尽量减少添加到交流接地返回路径的寄生电感。这些寄生电感可能是由布局或元件方向选择引起的,例如去耦电容接地的方向。有两种基本方法,如图 10 和图 11 所示。

图 10.这种配置是旁路电容和相关过孔的最小总占位面积。

在这种配置中,连接V的过孔抄送顶层到内部电源层(层)的焊盘可能会阻碍交流接地电流返回,迫使返回路径更长,从而产生更高的寄生电感。流入 V 的任何交流电流抄送引脚穿过旁路电容到达其接地侧,然后返回内部接地层。这种配置是旁路电容和相关过孔的最小总占位面积。

图 11.这种配置需要更多的PCB面积。

在这种替代配置中,电源层过孔不会阻挡交流接地返回路径。通常,这种配置需要更多的PCB面积。

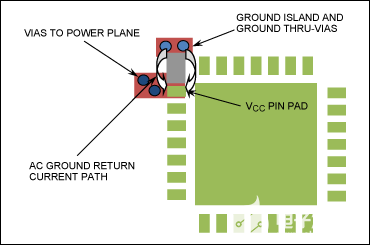

并联组件的接地

对于并联(接地)元件(如电源去耦电容器),建议的做法是每个元件至少使用两个接地过孔(图 12)。这降低了过孔寄生电感的影响。通孔接地“孤岛”可用于分流连接的组件组。

图 12.为每个元件使用至少两个接地过孔可降低过孔寄生电感的影响。

IC 接地层(“焊盘”)

大多数IC要求元件正下方的元件层(PCB的顶部或底部)具有坚实的接地层。该接地层将通过PCB将直流和RF返回电流传输到指定的接地层。该元件“接地焊盘”的次要功能是提供散热片,因此焊盘应包括PCB设计规则允许的最大直通孔数。下面的示例显示了嵌入在 RFIC 正下方中央接地层(组件层上)中的 5 × 5 通孔阵列(图 13)。应使用其他布局考虑因素可以容纳的最大过孔数。这些过孔是理想的直通孔(即,一直穿透PCB),并且必须电镀。如果可能,过孔应填充导热浆料以增强散热器(焊膏在通孔电镀后和最终电路板电镀之前涂覆)。

图 13.嵌入在RF IC正下方中央接地层中的5×5通孔阵列。

审核编辑:郭婷

-

pcb

+关注

关注

4322文章

23128浏览量

398651 -

射频

+关注

关注

104文章

5595浏览量

167939 -

RFIC

+关注

关注

1文章

60浏览量

24497

发布评论请先 登录

相关推荐

RF和混合信号PCB布局最佳指南(专家应用笔记)

混合信号PCB布局设计的基本准则

射频和混合信号的PCB布局指南

射频和混合信号的PCB布局指南

评论