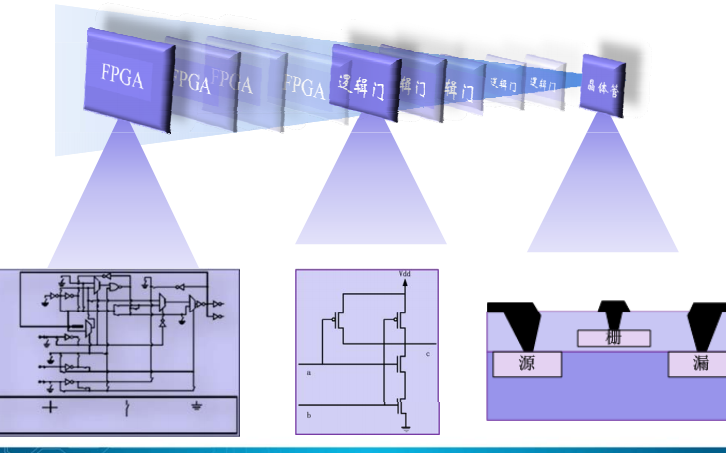

FPGA的本质是设计一颗芯片,其开发刘成是通过verilog等硬件描述语言通过EDA工具编译、综合、布局布线成为下载文件,最终加载到FPGA器件中去,完成所实现的功能。而硬件描述语言描述的就是组合逻辑和时序逻辑电路,度和逻辑就是与、非、或组成的电路,而时序电路就是触发器。在FPGA中,组合逻辑的变成了查找表的工作,于是所有的数字电路转化成为查找表和寄存器,这便是FPGA的基础,查找表负责逻辑实现,寄存器存储电路状态。现代FPGA内部除了查找表和寄存器之外,还有RAM块,用于存储大量的数据块,这样可以节省芯片实现的面积。FPGA内部的时序电路需要时钟的输入,通常FPGA内部需要的时钟种类较多,因此需要在片内产生相关的时钟,因此时钟管理单元DCM/PLL也是必不可少的内部部件。除此之外,FPGA内部还包括接口I/O,可分为普通I/O和高速I/O,次外还有各种各样的硬核。

FPGA的英文翻译过来是现场可编程门阵列,这是相对于ASIC来说的,ASIC硬件也可以可做是门阵列,但是它是非可编程的器件,流片完成之后功能就固化了。但是FPGA 的可编程性在于其能够重新下载配置文件,来改变其内在的功能。两者在前端开发流程上并无二致。FPGA作为一种器件,技术主要垄断在ALTERA和XILINX这两大公司手中。

(一)FPGA架构

一个完整的嵌入式系统中由单独一个FPGA组成的情况较少,通常由多个器件组合完成,例如CPU+FPGA。通常是由一个FPGA+ARM,ARM负责软件配置管理,界面输入外设操作,FPGA负责大数据量运算,可看做CPU的专用协处理器来使用,也常会用于扩展外部接口。常用的架构有ARM+FPGA,DSP+FPG A,或者网络处理器+FPGA等,这些架构形成构成整个高速嵌入式设备的处理形态。实现高速处理方面,CPU的发展趋势是多核。FPGA的热门应用有:

1)网络存储产片

2)高速网络设备

3)4G通信等设备:对于新一代通信基站的信号处理,FPGA+DSP阵列的架构就是绝配。

总之,没有完美的架构,只有合适的组合。

(二)器件互联

系统架构确定之后,下一步就是FPGA和各器件的互联问题。通常来说,CPU和FPGA的互联问题主要取决于两个要素:

1)CPU所支持的接口

2)交互的业务

通常FPGA一般支持与CPU连接的数字接口,其常用的有EMIF,PCI,网口,DDR等接口。作为总线类接口,FPGA通常作为从设备与CPU连接,CPU作为主设备通过访问直接映射的地址对FPGA进行访问。通常总线访问分为同步访问和异步访问。CPU手册中会对信号定义时序控制有着详细的说明,FPGA根据这些详细的说明来说实现相应的逻辑。同时CPU还会对访问时序进行设置,例如设置建立时间、保持时间、最快时钟。对于总线型的访问来说,数据信号通常为三态,用于输入输出,这种设计目的减少外部连线的总数。总线访问优势是直接映射到系统的地址区间,访问较为直观,但相对传输速率不高,主要原因如下:

1)受制总线访问间隔,即两次访问中间的空闲状态

2)不支持双向传输,并且FPGA主动对CPU发起操作是,只有中断处理一种方式。

这种总线型操作特点可以使其用作系统的管理操作,例如FPGA内部寄存器的配置,运行过程中所需参数配置,以及数据量较小的信息交互等操作。这些操作数据量和所需带宽合适,可应对普通的嵌入式系统的需求处理。而对于大数据流量的数据交互,一般采用专用的总线交互,其特点支持双向传输,总线传输速率较快。

(三)FPGA特点

FPGA最大的特点在于其灵活性:

1)I/O的灵活性,可以通过其I/O组成各种接口与各种器件连接,并且支持不同的电器特性。

2)内部存储器灵活,可以通过IP生成工具生成各种深度和宽度的RAM和FIFO

3)逻辑的灵活性,内部逻辑可生成各种类型IP

(四)架构设计

1)流驱动式

对于一个FPGA的架构设计,其首先需要考虑的就是性能,其次就是接口设计。一般架构设计是采用数据流驱动方式实现的,通常来说应用于IP领域、存储领域、数字处理领域等较大型FPGA设计都是数据流驱动式架构,主要包括输入接口单元,主处理单元,输出接口单元,还可能包括辅助处理单元、外部存储单元,这些单元之间一般采用流水式处理,即数据处理完之后数据打包发下一级处理。其中数据输入输出可能有多个,此时需要架构内部实现数据的交换。

2)稳定性:设计一定能够进行正常工作

3)时钟域复位:复位一般采用异步复位同步释放的方式。

4)并行与复用:并行可以提过处理速度,复用可以节省资源。最终的设计取决于对设计处理能力和逻辑数量的权衡。

5)流水线处理:简化设计;时序优化。但是流水设计对于带反馈的设计无能为力,强加流水设计的话有可能会浪费逻辑和设计。

(五)FPGA中一些常用内部资源

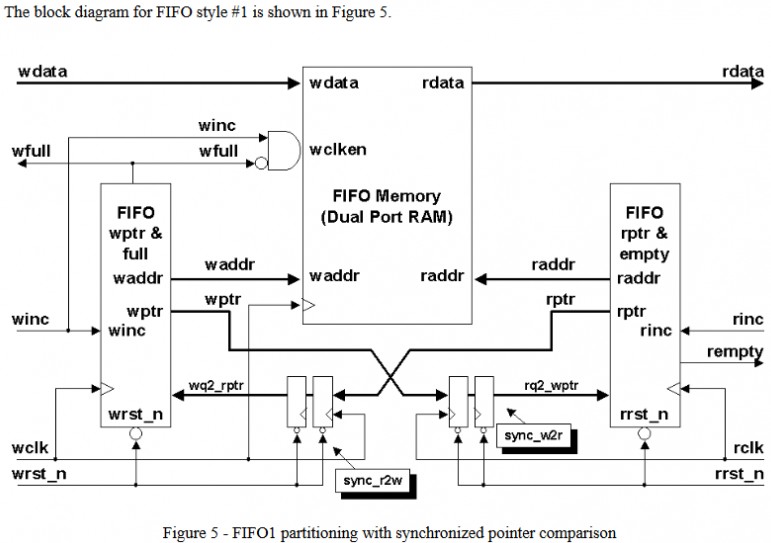

1)FIFO设计:作为FPGA中内部资源的一个常用器件,最常见与异步时钟域划分和缓冲数据,但不仅限于此。简化设计、减少耦合、输入输出接口固定,便于仿真和验证,都是使用FIFO的好处。

2)RAM:通常实例化RAM中,一种是BLOCK RAM,一种是分布式RAM,前者可以提供较大的存储空间,后者提供较小的存储空间。

(五)coding原则

1)注释:好的代码必须有注释,注释至少包括文件注释、端口注释和功能语句注释。好的注释,可以提高代码的可读性,可维护性。

2)语句:所写语句一定是可综合的,在FPGA设计中无外乎就是时序逻辑和组合逻辑。组合逻辑是即可生效的,时序逻辑是时钟的下一拍起效。

3)阻塞与非阻塞赋值:一般情况下,组合逻辑用的是阻塞赋值,时序逻辑用的是非阻塞赋值。

4)注意避免锁存器的生成:锁存器最容易产生在always(*)模块,所有的分支条件都要描述并且赋值,状态机中的default状态也不要忘记。

(六)接口设计

在进行设计的时候,需要一个接口模块,首先需要明确以下问题:

1)同步接口还是异步接口?

2)有哪些信号,功能是什么?

3)信号之间的时序关系是什么?

4)传递的效率什么?

这些问题的答案一般都会在datasheet中给出,一般设计一个接口模块,必然与其他硬件电路相连接。加入外部连接接口是总线接口,至少包括以下却不限于以下信号:

1)地址:能够支持的最大地址空间,数据和地址是否复用?

2)数据:一般读数据和写数据复用同一接口

3)读写命令

4)是否支持突发传输

5)同步还是异步

6)控制信号之间的相位关系以及建立时间和保持时间的要求

(6)学会总线设计

PC时代,垄断江湖的是微软和INTel,而在移动互联网时代,最具有潜质的就是谷歌的ANDROID系统和ARM芯片。因此作为ARM处理做片上互联的AMBA总线标准成为业界应用最广泛的标准。

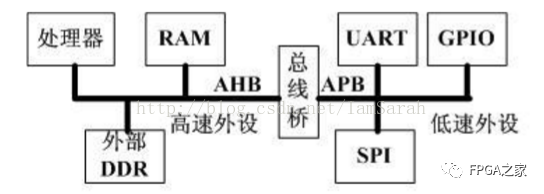

AMBA总线实际是三个标准的集合,分别为AHB,ASB,APB。ASB已经逐渐被AHB取代,现在使用最广泛的是AHB和APB总线,以及最新扩展的AXI总线。如图为AHB和APB在一个嵌入式系统中的应用场景。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21744浏览量

603576 -

cpu

+关注

关注

68文章

10870浏览量

211869 -

接口

+关注

关注

33文章

8611浏览量

151229 -

时序电路

+关注

关注

1文章

114浏览量

21703 -

触发器

+关注

关注

14文章

2000浏览量

61163

原文标题:FPGA相关知识系统介绍

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA入门知识介绍

CentOS系统的知识介绍

介绍UG编程的基本操作及相关加工工艺知识

手机电池相关知识介绍

FPGA基础知识培训教程免费下载

基于FPGA 以及数字电路设计相关高级技巧介绍

FPGA相关知识系统介绍

FPGA相关知识系统介绍

评论