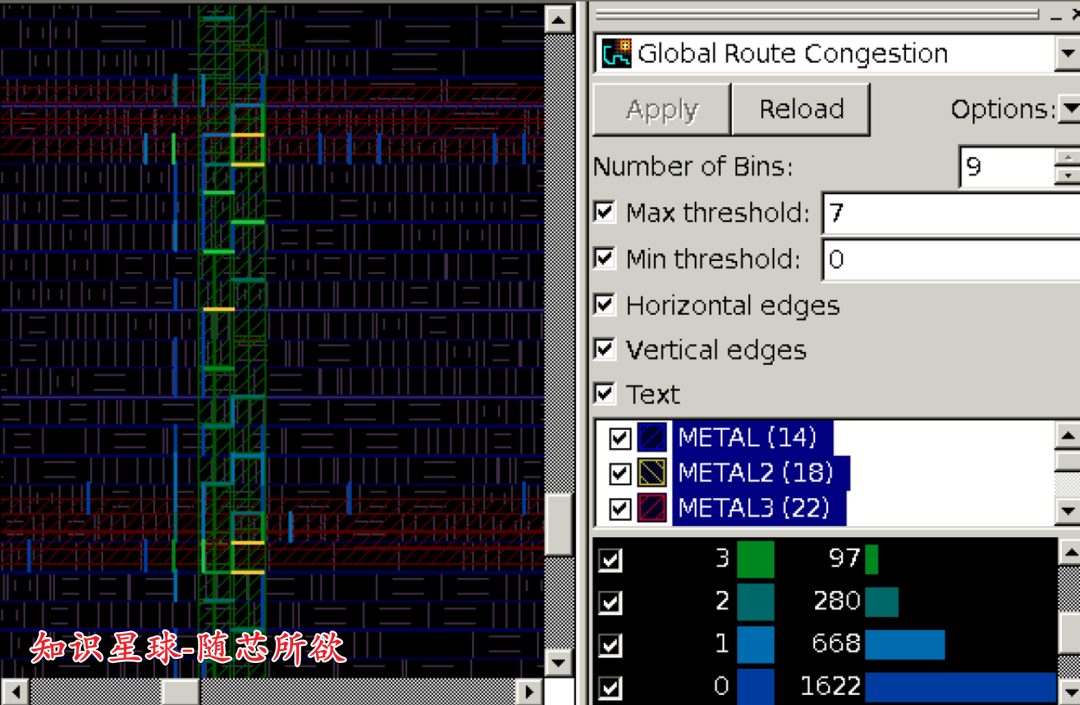

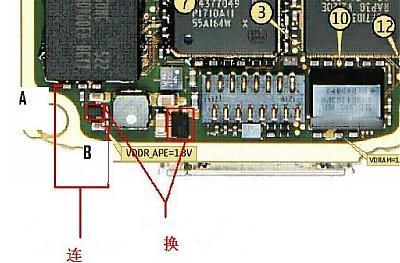

如果数字IC版图设计中Power Mesh打的太宽(尤其是VDD和VSS的Stripe靠近放置的情况),下方还放置的有标准单元,那么在出Pin的地方可能会存在Congestion,如下图所示,那么这种问题该如何解决呢?对于ICC、Innouvs、ICC2分别该如何解决呢?

解决方案:

1、调整PG structure,让电源地间隔放置。或者合理减少power,不要打太多、不要打太宽。根据以往经验和IR-drop分析的结果,可以在IR-drop满足的情况下,降低PG的宽度,不用占用太多布线资源。

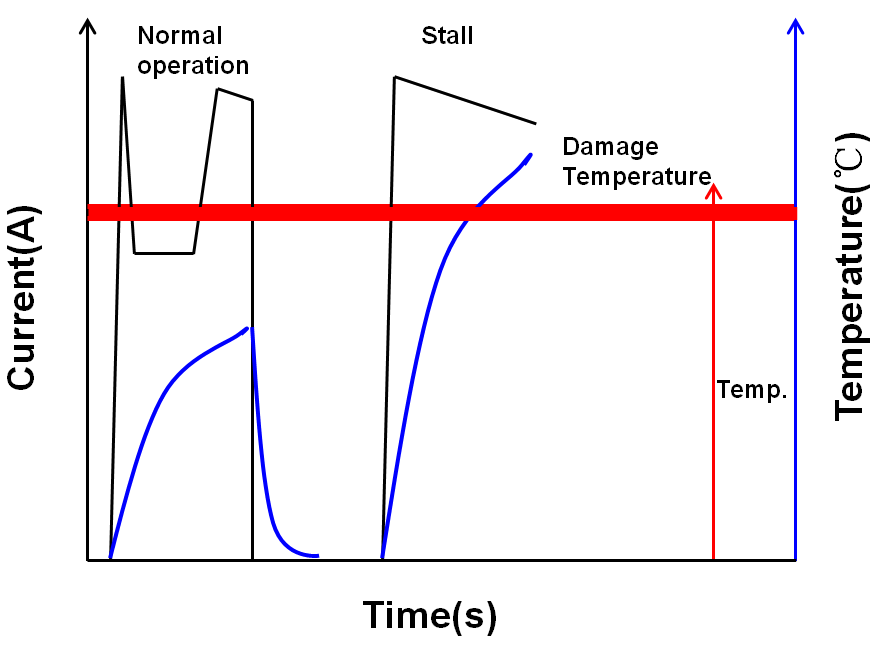

2、一般在电源地Strap下面放置标准单元时,可能会在Strap的地方存在Congestion。这时可以限制工具在电源地Strap下面少放或者不放置标准单元,设置hard blockage,partial blockage/partial density control。

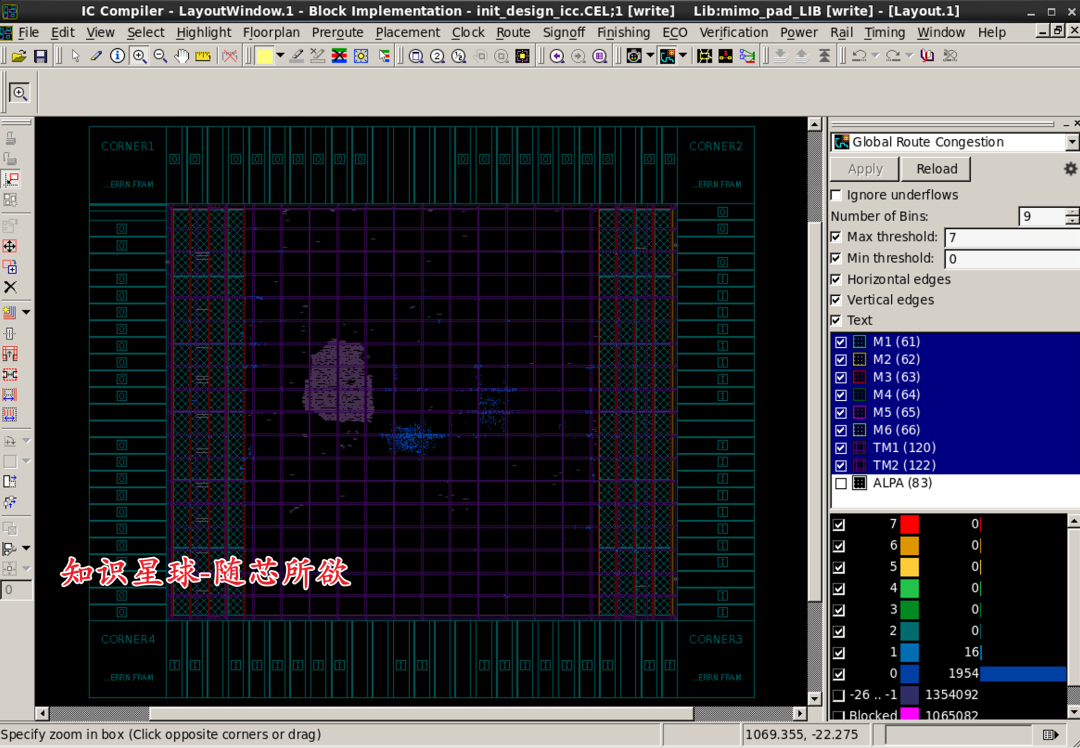

如下图所示,可以非常清晰的看到,大部分的拥塞都发生在PG Mesh附近,这可以通过对Power Mesh设置partial blockage来解决。

下面分别讲解一下在ICC/ICC2和Innovus该如何实现该需求。

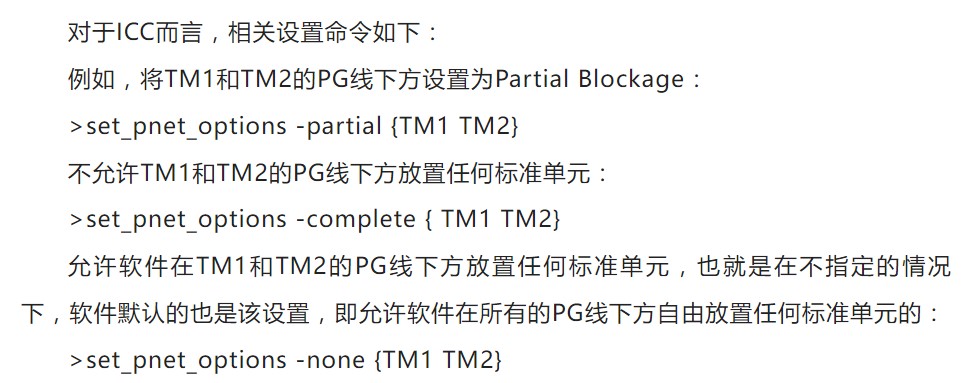

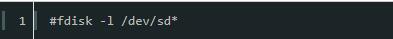

ICC设置:

ICC2设置

实例:

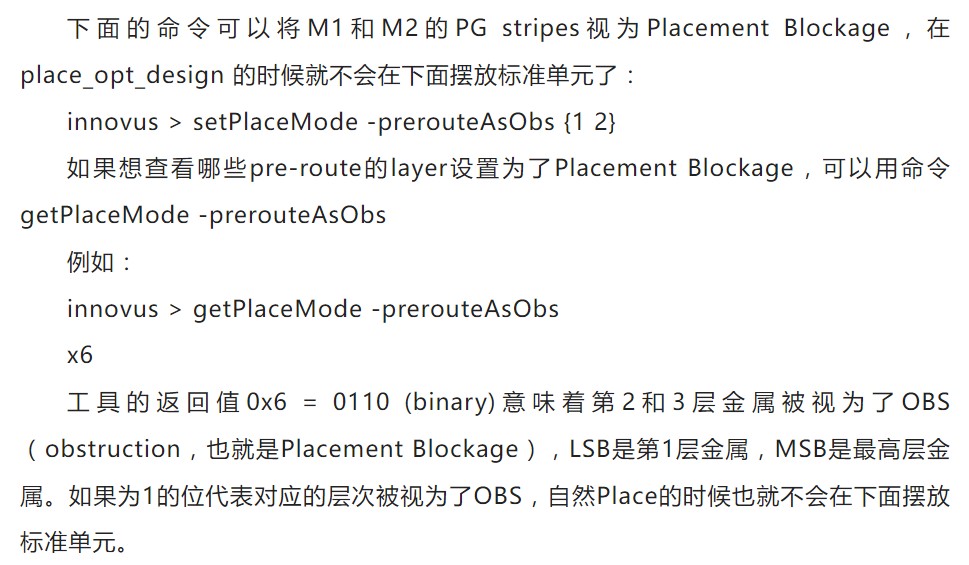

Innovus设置:

方法1:将指定Layer的preroute视为Placement Blockage

方法2:在PG stripes下方创建Partial Placement Blockage

审核编辑:刘清

-

数字IC

+关注

关注

1文章

38浏览量

12569 -

VDD

+关注

关注

1文章

312浏览量

33268 -

VSS

+关注

关注

1文章

35浏览量

21450 -

电源地

+关注

关注

0文章

36浏览量

9804 -

mesh技术

+关注

关注

0文章

14浏览量

8760

原文标题:Congestion修复实例及脚本分享 - 控制PG stripe下面少放甚至不放Cell

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字IC版图设计中Power Mesh打的太宽怎么办

数字IC版图设计中Power Mesh打的太宽怎么办

评论