作者:Paul Hendriks、Richard Schreier 和 Joe DiPilato

移动无线电用于公共安全和紧急服务(如警察、消防和救护车)以及私人服务,如车队管理。为了提供增强的服务,以及提高频谱效率和覆盖范围,这些无线电的设计已从传统的基于模拟的调制方案(如FM和PM)转向数字调制方法。

这些无线电的接收器必须能够在存在大干扰信号的情况下准确数字化低电平高频信号。在使用某些窄带移动标准的无线电中,干扰信号可能比所需信道大70 dB,频率偏移小至25 kHz。由于这些系统通常不是蜂窝系统,因此移动无线电的地理覆盖范围也是一个重要特征 - 它们必须具有出色的灵敏度,以恢复来自覆盖范围边缘用户的低电平信号。更复杂的是,这些无线电通常是便携式的,使用率很高;他们要求使用更小、寿命更长的电池来降低功耗。

为了帮助设备设计人员,ADI公司推出了AD9870 IF数字化子系统,该IC旨在满足移动无线电和类似窄带无线电应用的苛刻要求,采用超外差架构,采用模拟和/或数字调制方案。AD9870集成了整个IF条,外部元件极少。它可以接受频率高达300 MHz、带宽高达150 kHz的IF信号,并提供包含16位I和Q数据的串行数据输出,然后可以使用主机处理器对其进行解调。AD9870适用于基站和用户单元,兼具基站所需的动态范围和便携式无线电所需的低功耗。

所有接收器的最大问题是动态范围

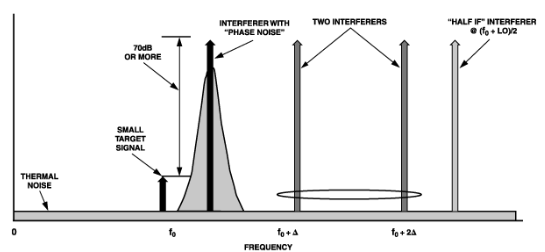

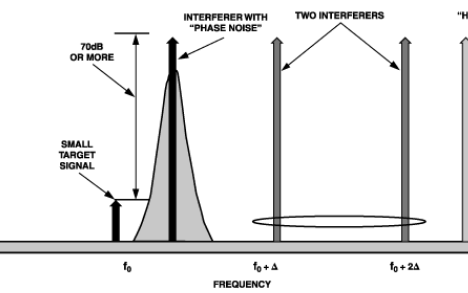

接收器的动态范围决定了其在存在较大信号(称为阻塞和干扰源)的情况下恢复低电平信号的能力。图1显示了可以降低任何无线电接收器有效动态范围的各种源。

图1.所有接收器的“大问题”是动态范围!

目前假设频谱中存在的唯一信号是“小目标信号”。最小可检测信号或灵敏度将由信号带宽(B)、接收器的检测阈值(SNR)决定最低)、接收器的噪声系数 (NF) 和固有热噪声限制 (kTB)。在290 K的温度下,灵敏度可以用以下公式估算:

敏感性 = 信 噪 比最低+ 10log(B)+NF+(-174 dBm/Hz)

以下是一些潜在的噪声源:

如果在下变频到低于工艺技术的1/f转折频率之前,对目标信号施加的增益不足,则低频1/f噪声就会成为一个问题。由失调和二阶失真引起的直流元件也可能是有问题的。

大干扰源可以通过接收器LO的相位噪声将其能量分布在很宽的频率范围内,通过称为“倒易混频”的过程。干扰源越大,离目标信号越近,目标信号就越有可能被这种噪声传递机制破坏。此外,如果该干扰源足够大,足以在接收器的前端电路中引起非线性,则杂散分量可能会混回目标信号的通带中。“半中频”问题是困扰二阶线性度差的接收器的特殊情况,其中落在LO和目标信号之间的干扰产生二阶分量,该分量与LO的二次谐波混合以产生落在目标信号上的杂散。接收器的IIP2规格允许接收器设计人员量化“半中频”杂散。干扰源电平之间的差异或Δ,P在,得到的二阶杂散为 IIP2 – P在.AD9870的IIP2为45 dBm,基本上不受这种“半中频”问题的影响。

两个等间距频率偏移的大干扰源(即f0+ δ 和 f0来自目标信号的+ 2Δ)将通过互调过程导致杂散分量落在目标信号的顶部。在这种情况下,接收器的线性度在其IIP3规范中得到体现,数字越大,表示对三阶交调的容差越高。两个相等干扰源之间的差值或Δ,P在,所得的三阶互调分量为 2 × (IIP3 – P在).AD9870具有–1 dBm的IIP3,因此在降低接收器灵敏度之前可承受高达–45 dBm的干扰。

超外差架构

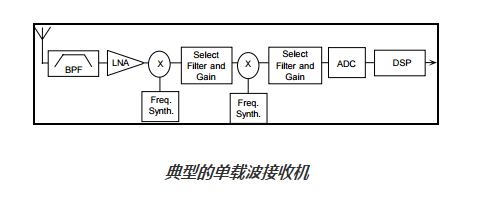

为了应对会降低接收器恢复目标低电平信号能力的大干扰源,使用超外差架构将RF信号转换为一个或多个中频(IF),其中对相邻干扰信号进行滤波以及目标信号的放大和增益控制更为实用。超外差方案自第一次世界大战以来一直被采用,迄今为止一直是最受欢迎的无线电接收器架构。采用这种架构的通用版本(窄带数字接收器中很常见)如图2所示。

图2.数字接收器的典型超外差架构。

在RF-IF下变频之前,带选择滤波器(双工器)和/或镜像抑制滤波器选择目标信号工作的整个RF频段。低噪声放大器(LNA)在下变频之前放大预期的RF频段,对于确定接收器的灵敏度至关重要。除目标信号外,RF混频器之后的下变频IF频谱通常还包含不同强度的信号阵列。通道选择和放大发生在IF:目标信号通过一个或多个晶体或SAW型无源滤波器从其他信号中选择。滤波后,目标信号经过进一步放大,其信号强度通过AGC环路稳定在预设水平,以优化正交解调过程。在许多数字接收器中,IF模拟正交调制器将IF信号分离成正交基带I和Q分量,然后由双通道ADC进行数字化处理。在这种情况下,解调信号的调制精度对正交调制器和双通道ADC中的模拟失调、正交LO失配和I/Q增益失配非常敏感。

AD9870架构

AD9870 IF数字化子系统集成了大部分IF、基带和一些数字后处理功能模块,降低了典型超外差接收器的复杂性,如图3所示。

图3.AD9870简化了数字接收器,同时提高了性能。

AD9870与典型的超外差架构不同,它采用宽动态范围带通Σ-Δ型ADC对第二中频信号以及任何相邻干扰源进行采样。目标中频信号的解调以数字精度和稳定性执行,而附近的侵入干扰源可以通过数字滤波进行抑制。

图4显示了AD9870的功能框图。LNA和混频器的作用类似于超外差架构的RF部分,用于放大和下变频以第一中频为中心的目标信号,使其下变频为适合带通ADC数字化的较低第二中频。

图4.AD9870的功能框图显示了集成度。

LNA和混频器提供约10.5 dB增益,同时保持系统动态范围,输入噪声系数为9 dB,三阶截调截点为0 dBm。高输入阻抗(360欧姆)简化了与晶体或SAW滤波器的接口。片内LO PLL频率合成器可与外部环路滤波器和VCO结合使用,以产生可调谐LO频率。

第二中频信号正好以带通ADC采样速率的1/8为中心(即如果2= ƒ佛罗里达州。/8) 以允许简单的 ƒs/8数字正交解调方案。下变频至第二中频后,信号由可调谐(和可编程)有源三阶抗混叠滤波器(AAF)处理,以抑制可能出现在采样ADC混叠频带内的信号(即N × ƒ佛罗里达州。/8 ± ƒ佛罗里达州。/8.AAF 调谐电路可以支持 13 至 18 MHz 之间的 ADC 采样速率,通常将 3dB 截止频率设置和调谐至略高于第二个 IF (即 ƒ-3分贝=ƒ佛罗里达州。/3.2).

AAF 中内置一个可变增益放大器 (VGA),可提供高达 26 dB 的增益范围(图 5)。VGA增益扩展了AD9870的动态范围,可以直接编程,也可以通过自动增益控制(AGC)环路进行控制。AGC环路通常在强信号条件下调用,通过在ADC输入端保持可编程固定信号电平来防止A/D转换器“过载”或削波。AD9870采用高效的混合方法实现AGC功能,如图5所示:模拟域和数字域协同工作,进行信号估计和控制。

图5.“混合”AGC控制环路扩展了AD9870的动态范围。

当强目标信号或干扰源落在第一级20倍数字滤波器的带宽内时,对信号进行数字估计,并与编程参考电平(AGCR)进行比较。两级之间的差值被馈送到数字积分器,数字积分器更新控制DAC以调整VGA的模拟电压。由于无法准确估计落在第一级数字滤波器通带之外的强干扰源,因此基于简单差分比较器的模拟环路监视ADC的输入,并在任何超量程条件下控制环路,以降低VGA增益。

外部电容器用于平滑DAC的转换,其时间常数由其电容和DAC的内部源电阻确定。R-C截止频率通常设置在控制系统的环路带宽之外,以确保对环路动态进行连续的数字控制。控制环路带宽可通过数字方式编程,攻击和衰减时间可在很宽的范围内变化,并能够对任何过载条件做出反应。

任何包含VGA的窄带接收器信号链的瞬时动态范围取决于VGA的特定增益设置,因为信号路径中每级贡献的噪声与“整体”输入参考噪声的比值随着前一级增益的增加而降低。这意味着由噪声系数NF描述的输入噪声通常由前几级(即LNA和混频器)主导,信号链末端的噪声源(即ADC)对系统噪声系数的影响最小,前提是这些模块之间有足够的增益。

图6.AD9870的动态范围取决于VGA设置。

对于AD9870,VGA的增益在25 dB范围内标称可调。图6显示了当目标信号(或干扰源)的输入功率从–85 dBm增加到–23 dBm时,VGA增益设置如何影响AD9870的噪声系数。在小信号条件下,VGA设置为最大增益;AD9870的噪声系数由LNA/混频器和VGA的输入噪声决定。但是,随着信号功率的增加,它会达到VGA增益开始降低的点(取决于AGC基准电平),以防止ADC削波。此时,随着信号功率的进一步增加,VGA增益降低,dB对dB。此外,在此区域中,ADC的输入信号电平保持不变,ADC的噪声开始占主导地位,因此系统的NF也会以每dB1 dB的速率下降。随着信号功率的持续增加,达到VGA增益设置为绝对最小值的点(即–26 dBm),ADC输入端的信号电平进一步增加,直到发生削波(即–24 dBm)。

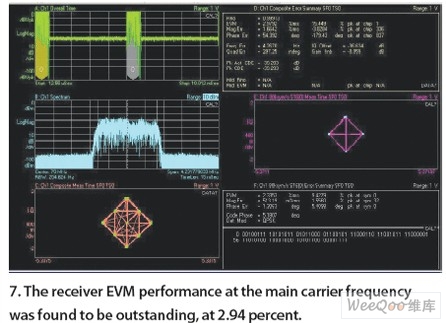

AD9870的“核心”是其带通Σ-Δ型ADC(图7),它使低中频数字化方法在IC中变得可行且实用,适用于需要高动态范围和最小功耗的无线电系统。该ADC与后端数字抽取滤波器一起,在10 kHz带宽内实现了近14.5 ENOB的性能,同时对频率高达2.25 MHz的信号进行采样。它实现了这些规格,同时从3.0 V电源仅消耗13 mA电流。

图7.多位四阶带通 E-Δ ADC 可在 ƒ 处产生深陷波佛罗里达州。/8.

Σ-Δ ADC基于一个四阶开关电容、多位调制器,由两个级联谐振器组成,在噪声传递函数(NTF)中提供两对复数零点,落在ƒ附近佛罗里达州。/8.这些复零点在2nd-IF频率的位置以及多位反馈路径有助于确保窄区域内的低本底噪声(ƒ的±3.3%佛罗里达州。/8) 在第二个中频频率附近。

来自ADC的数字输出数据馈入AD9870的数字信号处理部分(图8)。本节包括一个ƒ佛罗里达州。/8复数(或正交)解调器,后跟三个线性相位FIR滤波器。复数解调器分离目标二中频信号,中心位置为 ƒ佛罗里达州。/8,在滤波前放入其I/Q元件中。

图8.数字正交解调,后接可编程抽取滤波器,提供基带I/Q数据。

复数解调器的输出频谱由目标信号(现在以“dc”为中心)以及模拟域中未充分滤除的任何不需要的干扰源和/或噪声组成。一系列抽取滤波器去除了这些不需要的成分,同时根据目标通道的带宽降低了数据速率。根据调制方案,复数数据速率(因此抽取因子)设置为至少比通道带宽大两倍,以允许进一步的后处理。DEC1 和 DEC2 均使用级联四阶梳状滤波器拓扑;DEC2 的抽取因子可由用户编程,以适应不同的通道带宽。DEC3 是一个十进制乘 3 FIR 滤波器;它设置复合滤波器的近内在过渡带特性。DEC3的16位I和Q输出被馈入同步串行接口(SSI)功能,该功能将数据格式化为串行位流,并将其他可选信息(如AGC、信号强度和同步)嵌入到位流中。

审核编辑:郭婷

-

滤波器

+关注

关注

161文章

7826浏览量

178177 -

接收器

+关注

关注

14文章

2472浏览量

71928 -

RF

+关注

关注

65文章

3055浏览量

167052

发布评论请先 登录

相关推荐

图文详解数字接收机的应用设计

数字接收机对高性能ADC有什么要求?

模块化FPGA设计在某雷达接收机中有哪些应用?

通过LQFP中的IF数字化子系统简化高性能窄带接收机设计

通过LQFP中的IF数字化子系统简化高性能窄带接收机设计

通过LQFP中的IF数字化子系统简化高性能窄带接收机设计

评论