使用时钟分配设备时或时钟ADC和DAC的扇出缓冲器,需要处理信号衰减的两个主要来源 - 印刷电路板(PCB)走线实现和输出端接。

时钟走线和信号摆幅

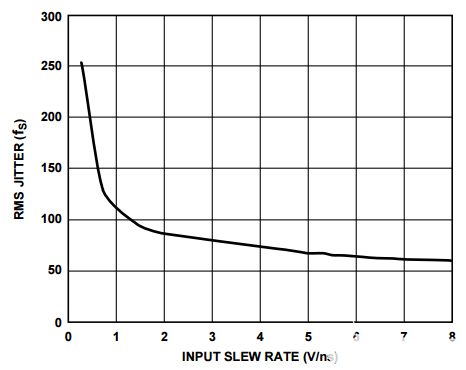

PCB走线的行为类似于低通滤波器,当时钟信号沿走线行进时会衰减,并随着走线长度的增加而增加脉冲边沿失真。较高频率的时钟信号会受到更大的衰减、失真和噪声的影响,但为了改善抖动(在低压摆率下最差)(图 1),通常使用具有高压摆率的时钟边沿。要正确实现高质量的时钟,请使用高摆幅时钟信号和短时钟PCB走线;将要时钟的设备放置在尽可能靠近时钟分配设备的位置。

图1.ADCLK925 均方根抖动与输入压摆率的关系

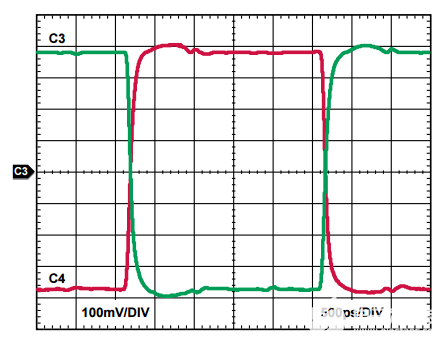

两种这样的时钟分配器件是ADCLK9542时钟扇出缓冲器和ADCLK9143超快时钟缓冲器。ADCLK954内置12个输出驱动器,可将800 mV全摆幅ECL(发射极耦合逻辑)或LVPECL(低压正ECL)信号驱动至50 Ω负载,总差分输出摆幅为1.6 V,如图2所示。它以 4.8 GHz 的切换速率运行。ADCLK914可以将1.9 V高压差分信号(HVDS)驱动至50 Ω负载,总差分输出摆幅为3.8 V。ADCLK914具有7.5 GHz切换速率。

驱动DAC时,时钟分配器件应尽可能靠近DAC的时钟输入,以便所需的高压摆率、高幅度时钟信号不会导致布线困难、产生EMI或因电介质和其他损耗而降级。注意,特性阻抗(Z0) 的跟踪将随跟踪维度(长度、宽度和深度)而变化;驱动器的输出阻抗必须与该特性阻抗相匹配。

图2.采用3.3 V电源供电的ADCLK954时钟缓冲器输出波形。

输出端接

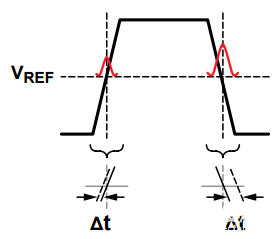

时钟信号衰减会导致抖动增加,因此端接驱动器输出以避免信号反射并在相对较大的带宽上最大化功率传输非常重要。实际上,反射可能会导致下冲和过冲,严重降低信号和整体时钟性能,或者在极端情况下,可能会损坏接收器或驱动器。当走线未正确端接时,会发生由阻抗不匹配引起的反射。由于反射系数的高通特性,它们对于具有快速上升和下降时间的高速信号更为重要。反射脉冲叠加在主时钟信号上,从而降低时钟脉冲的性能。它还通过在上升沿和下降沿增加延时不确定性或抖动(∆t)来影响时钟信号的边沿,如图3所示。

图3.由于端接不当导致反射信号的抖动影响。

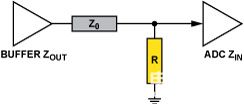

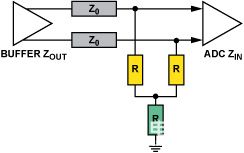

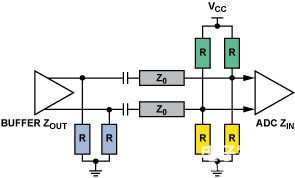

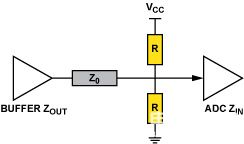

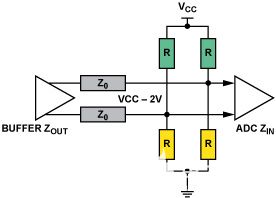

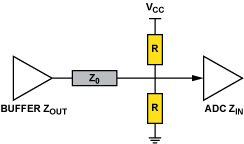

由于终止不当而导致的回波大小随时间变化,因此∆t也会随时间变化。终止时间常数也会影响回波脉冲的形状和宽度。由于这些原因,这种额外的反射引起的抖动形状(看起来是高斯的)增加了经典抖动。为避免这种抖动和时钟质量降低的不利影响,请使用适当的信号端接,如表1所示。Z0是线路的阻抗;Z外是驱动器的输出阻抗;和Z在 是接收器的输入阻抗。仅显示了CMOS和PECL/LVPECL电路。

表 1.时钟端接

| 方法 | 描述 | 强度 | 弱点 | 评论 |

|

串联端接 |

首席营销系统 |

|

实际上,缓冲器输出端省略了电阻(R),因为电阻(R)在整个频率上的动态行为很难匹配阻抗。 |

低功耗解决方案(无接地灌电流)。 易于计算 R (Z0– Z外). |

上升/下降时间受电路R和C的影响,增加抖动。 仅对低频信号有用。 |

CMOS 驱动程序。 不适用于高频时钟信号。 适用于低频时钟信号和非常短的走线。 |

|

下拉电阻 |

首席营销系统 |

| 非常简单(R = Z0) |

高功耗。 |

不推荐。 |

|

| 绿佩克利 |

|

简单的 3 电阻解决方案。 在节能方面略好,同时与 4 电阻端接相比节省了一个元件。 |

推荐。 将终端电阻放置在尽可能靠近 PECL 接收器的位置。 |

||

|

交流端接 |

首席营销系统 |

|

无直流功耗。 |

C应小以避免高功耗,但不要太小以允许灌电流。 |

||

| 绿佩克利 |

|

交流耦合允许偏置电压调整。避免电路两侧之间的功率流动。 |

交流耦合仅推荐用于平衡信号(50% 占空比时钟)。 | 交流耦合电容器应为低ESR、低电容。 | |

|

电阻桥 |

首席营销系统 |

|

合理的功率权衡。 |

单端时钟使用两部分。 |

||

| 绿佩克利 |

| 使用四个外部器件用于差分输出逻辑。 | 广泛用于 3.3V LVPECL 驱动器的端接。 |

-

滤波器

+关注

关注

162文章

8467浏览量

186248 -

adc

+关注

关注

100文章

7946浏览量

556878 -

PCB

+关注

关注

1文章

2352浏览量

13204

发布评论请先 登录

功率分配器

信号分配器

这是延长器还是分配器?

高速转换器时钟分配器件的端接

音视频/信号分配器,音视频/信号分配器是什么意思

VGA分配器,VGA分配器是什么意思

分配器,什么是分配器

高速转换器时钟分配器件的端接

高速转换器时钟分配器件的终止

高速转换器时钟分配器件的终止

评论