1 模电知识

在这里插入图片描述

- 电源符号含义

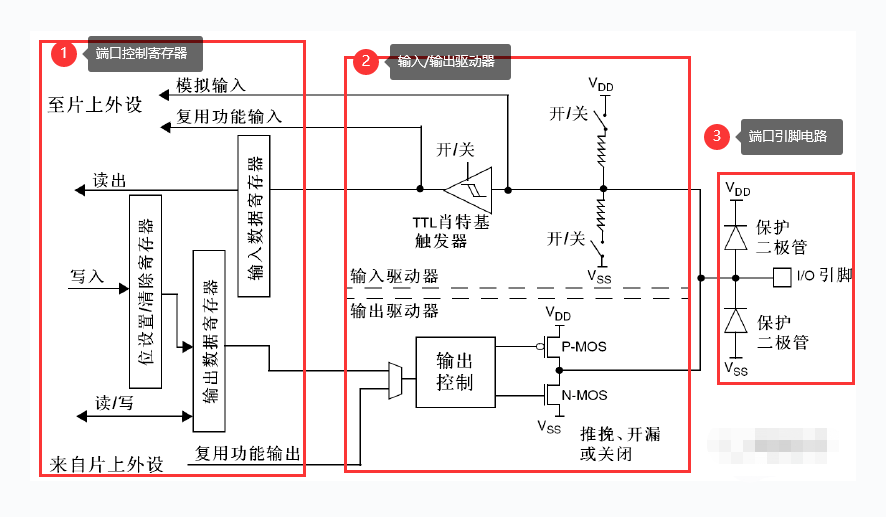

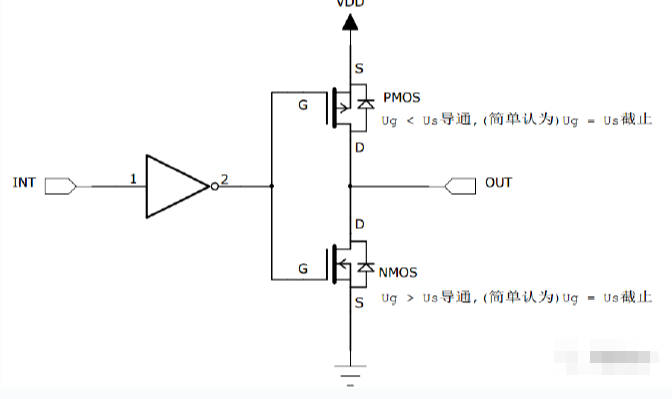

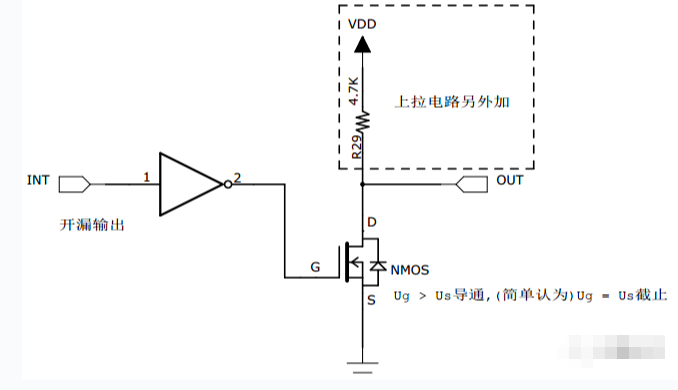

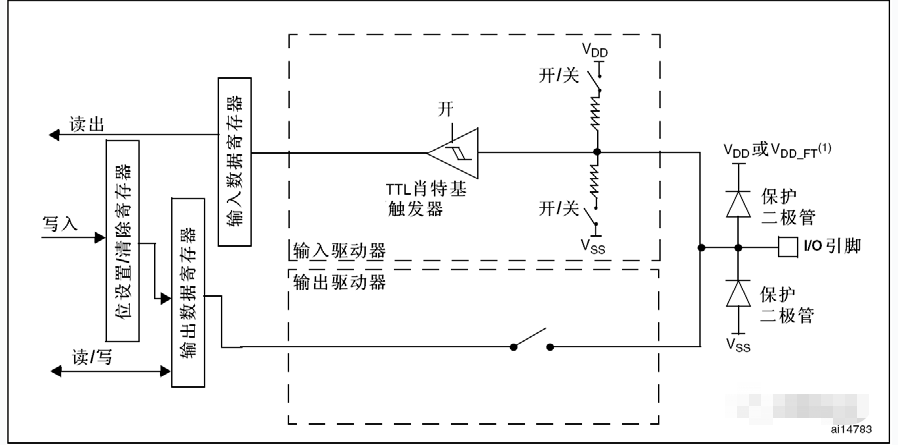

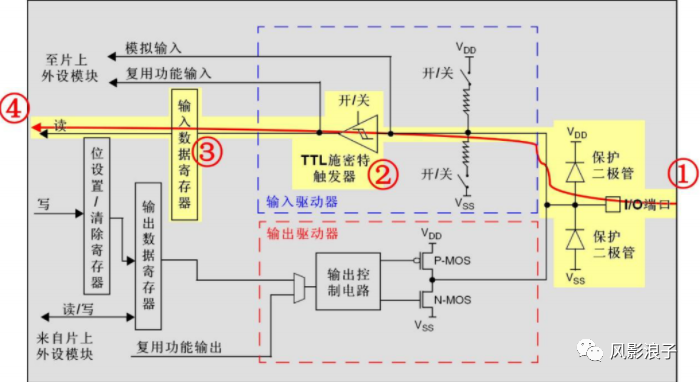

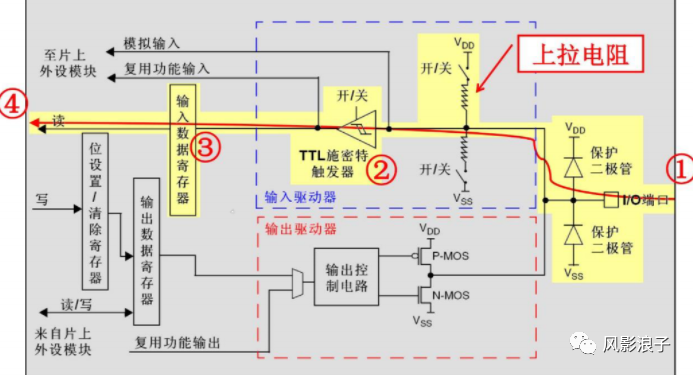

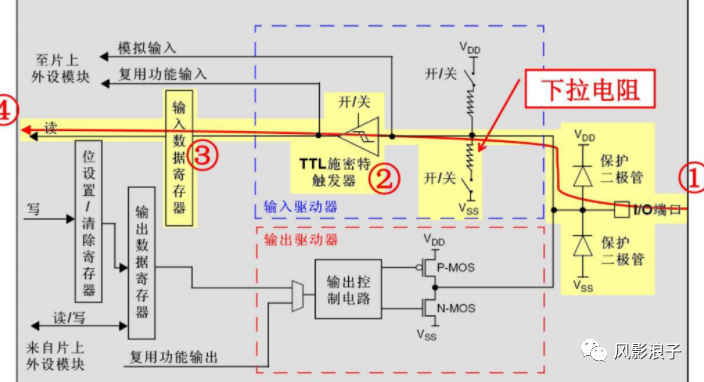

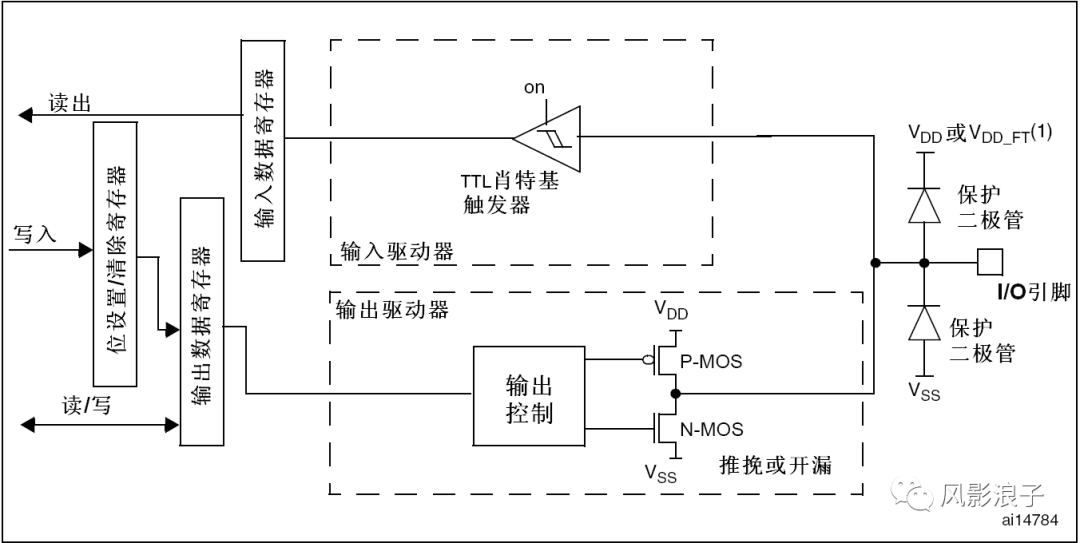

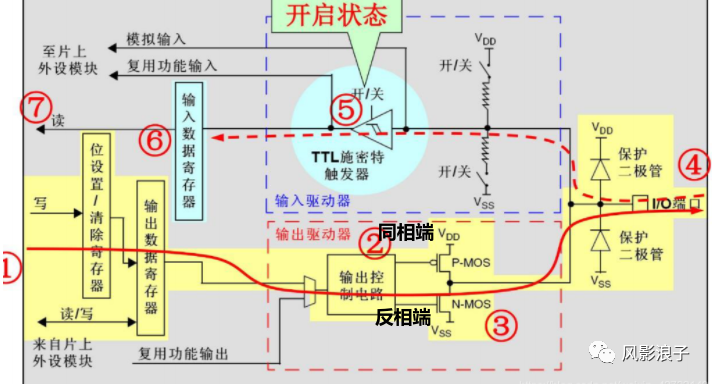

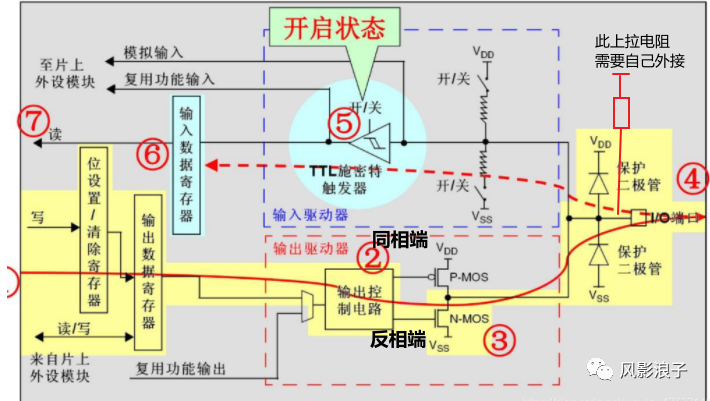

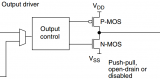

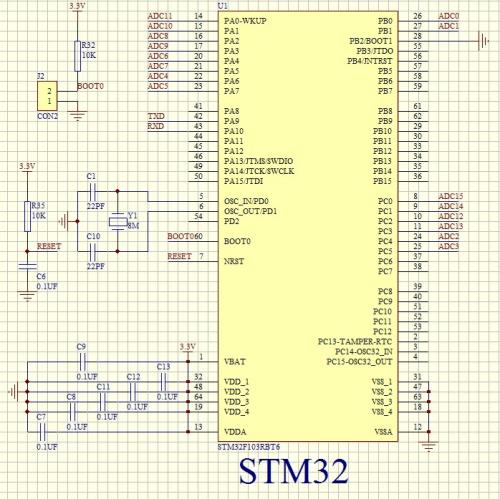

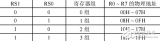

TTL肖特基触发器即为用肖特基管构成的施密特触发器,施密特触发器利用门阀电压将引脚模拟信号变成矩形信号,进行转化为0/1数字信号存入输入数据寄存器。 当引脚电压高于VDD 时,上方的二极管导通,当引脚电压低于VSS 时,下方的二极管导通,防止不正常电压引入芯片导致芯片烧毁。(虽有这样的保护,但不能驱动大功率器件,如直接驱动电机,电机堵转的反向电流会烧毁芯片) PMOS栅极低电平导通,NMOS栅极高电平导通。一般PMOS源极接VDD,NMOS源极接GND。 MOS管中寄生二极管作用是防止VDD过压的情况下,烧坏mos管。 推挽电路是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小、效率高。输出既可以向负载灌电流,也可以从负载拉取电流。下面分析电路: 当输入为高电平时,经过反向后输出到MOS管栅极为低电平,PMOS的SD导通,OUT输出为 线与:当在很多个开漏引脚连在一起时,外接一上拉电阻,如果有一个引脚输出为逻辑0,相当于短路接地,所以外电路逻辑电平便为0;只有当所有引脚均输出高阻态时,才由上拉电阻提供高电平,即为逻辑1。 在这里插入图片描述 在这里插入图片描述 注意 : 在这里插入图片描述 上图为加了上拉电阻的开漏输出(需用户外接):当输出数据寄存器相应位为1时,反相端输出0,此时NMOS截止,由外加的上拉电阻提供VDD:D=device 表示芯片内部工作电源(一般VDDVSS:S=series 表示公共连接,通常指电路公共接地端电压。

高电平VDD;当输如为低时,NMOS导通,OUT输出为低电平。当引脚高低电平切换时,两个管子轮流导通,P 管负责灌电流,N 管负责拉电流,使其负载能力和开关速度都比普通的方式有很大的提高。

2 GPIO模块电路结构

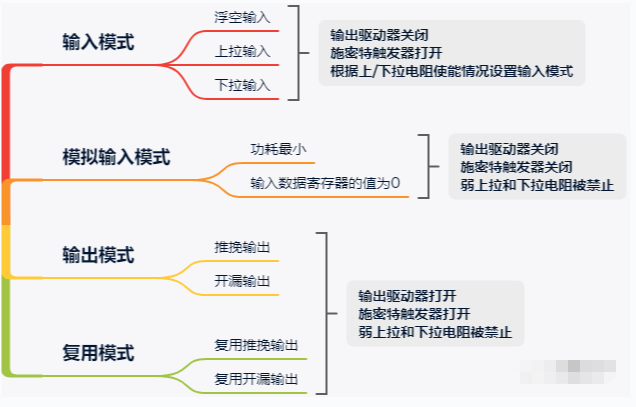

2.1 输入模式

浮空输入:上下拉电阻全断开

上拉输入:上拉电阻打开,下拉电阻关闭

下拉输入:下拉电阻打开,上拉电阻关闭

2.2 输出模式

通用推挽输出:

高电平。( 推-灌电流 )低电平。( 挽-拉电流 )通用开漏输出:

开漏输出时,PMOS关闭(输出数据寄存器的1将端口置于 高阻态 ),只有NMOS工作,但是此时只能输出低电平,要输出高电平必须外加上拉电阻。高电平。当输出数据寄存器相应位为0时,NMOS导通,引脚输出低电平。

-

电源

+关注

关注

184文章

17706浏览量

250004 -

寄存器

+关注

关注

31文章

5336浏览量

120262 -

GPIO

+关注

关注

16文章

1204浏览量

52060

发布评论请先 登录

相关推荐

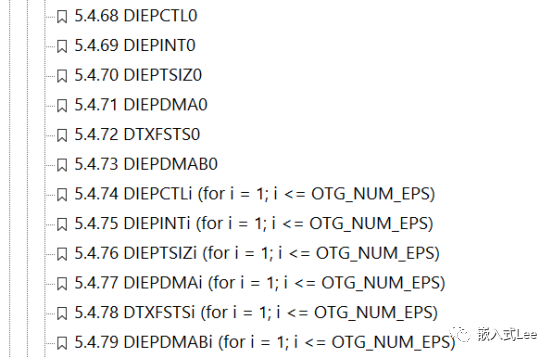

基于DWC2的USB驱动开发-发送相关的寄存器DMA寄存器详解

GPIO寄存器详解

STM32使用BSRR和BRR寄存器快速操作GPIO端口

基于stm32的GPIO寄存器学习解析

STM32单片机GPIO寄存器的功能解析

【嵌入式07】寄存器映射原理详解,GPIO端口的初始化设置步骤

STM32F103系列芯片的地址映射和寄存器映射原理,GPIO端口的初始化

GPIO寄存器

STM32寄存器点灯

STM32-GPIO_寄存器版(1)

STM32F103寄存器配置相关学习 —— GPIO

详解GPIO工作模式与寄存器1

详解GPIO工作模式与寄存器1

评论