具有高达18位分辨率和10 MSPS采样速率的逐次逼近型模数转换器(ADC)可满足许多数据采集应用的需求,包括便携式、工业、医疗和通信。本文介绍如何初始化逐次逼近型ADC以获得有效转换。

逐次逼近架构

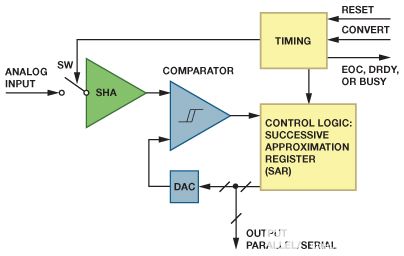

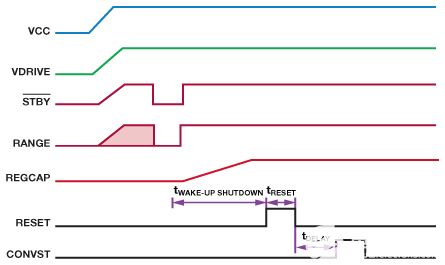

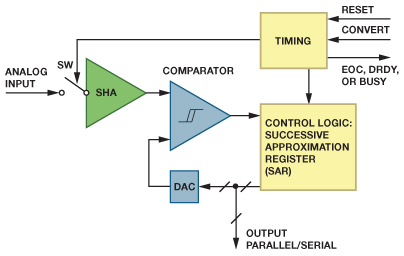

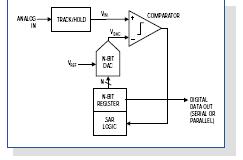

逐次逼近型ADC由四个主要子电路组成:采样保持放大器(SHA)、模拟比较器、基准数模转换器(DAC)和逐次逼近寄存器(SAR)。由于SAR控制转换器的运行,因此逐次逼近转换器通常称为SAR ADC。

图1.基本 SAR ADC 架构。

上电和初始化后,CONVERT 上的信号开始转换周期。开关闭合,将模拟输入连接到 SHA,SHA 获取输入电压。当开关断开时,比较器确定现在存储在保持电容上的模拟输入是大于还是小于DAC电压。首先,最高有效位(MSB)导通,将DAC输出电压设置为中间电平。比较器输出建立后,如果DAC输出大于模拟输入,则逐次逼近寄存器关断MSB,如果输出较小,则保持导通。该过程以下一个最高有效位重复,如果比较器确定DAC输出大于模拟输入,则将其关闭,如果输出较小,则保持导通。这种二分搜索一直持续到测试寄存器中的每个位为止。由此产生的DAC输入是采样输入电压的数字近似值,由ADC在转换结束时输出。

与SAR转换代码相关的因素

本文讨论与有效的首次转化相关的以下因素:

电源时序 (AD765x-1)

访问控制 (AD7367)

复位 (AD765x-1/AD7606)

精炼/重新输出 (AD765x-1)

模拟输入建立时间(AD7606)

模拟输入范围(AD7960)

省电/待机模式(AD760x)

延迟延迟(AD7682/AD7689、AD7766/AD7767)

数字接口时序

电源排序

一些采用多个电源工作的ADC具有明确定义的上电时序。AN-932应用笔记“电源排序”为设计这些ADC的电源提供了很好的参考。应特别注意模拟和基准输入,因为它们通常不应超过模拟电源电压0.3 V以上。因此,AGND – 0.3 V < VIN < VDD + 0.3 V,AGND – 0.3 V < VREF < VDD + 0.3 V。模拟电源应在模拟输入或基准电压之前导通,否则模拟内核可能会在闩锁状态下上电。以类似的方式,数字输入应介于DGND − 0.3 V和VIO + 0.3 V之间。I/O电源必须在接口电路之前(或同时)导通,否则这些引脚上的ESD二极管可能会正向偏置,并在未知状态下为数字内核上电。

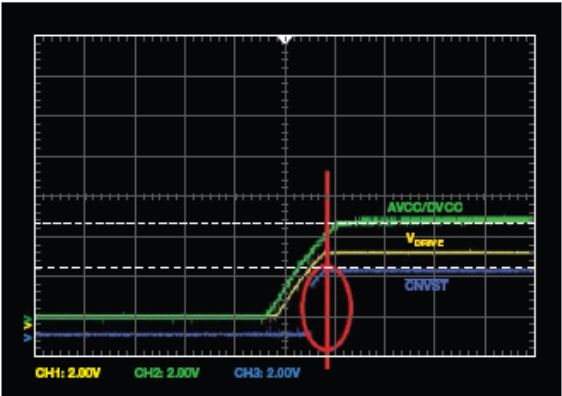

电源斜坡期间的数据访问

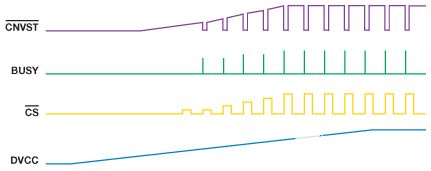

请勿在电源稳定之前访问ADC,因为这可能会使其处于未知状态。图2显示了一个示例,其中主机FPGA尝试从AD7367读取数据,同时DV抄送正在加速,这可能会使 ADC 进入未知状态。

图2.在DVCC上升期间读取数据。

SAR ADC 初始化与复位

许多SAR ADC,如AD760x和AD765x-1,上电后需要复位才能初始化。在所有电源稳定后,应施加指定的RESET脉冲,以确保ADC以预期状态启动,数字逻辑控制处于默认状态,转换数据寄存器清零。上电后,电压开始在 REF 上积聚在/裁判外引脚,ADC进入采集模式,并配置用户指定的模式。完全上电后,AD760x应看到上升沿复位,以将其配置为正常工作。RESET高脉冲通常应为50 ns宽。

建立基准电压

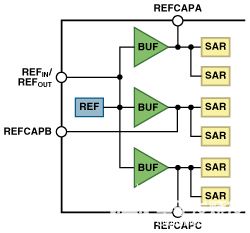

ADC将模拟输入电压转换为参考基准电压的数字代码,因此基准电压在首次转换之前必须稳定。许多SAR ADC具有参考电压在/裁判外引脚和 REF 或 REFCAP 引脚。外部基准可通过 REF 使内部基准过驱动在/裁判外引脚或内部基准可以直接驱动缓冲器。REFCAP引脚上的电容对内部缓冲器输出进行去耦,这是用于转换的基准电压。图3所示为AD765x-1数据手册中的基准电压源电路示例。

图3.基准电压源电路AD765x-1

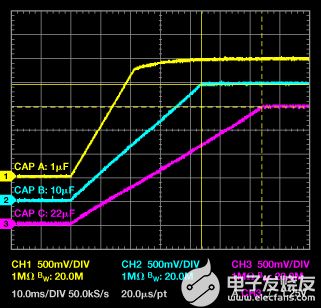

确保 REF 或 REFCAP 上的电压在第一次转换之前已经稳定。压摆率和建立时间因不同的储能电容而异,如图4所示。

图4.AD7656-1 REFCAPA/B/C引脚上的电压斜坡,采用不同的电容。

此外,设计不当的基准电压源电路会导致严重的转换误差。基准电压源问题的最常见表现是“卡住”代码,这可能是由储能电容的尺寸和位置、驱动强度不足或输入端噪声较大引起的。Alan Walsh 撰写的《精密逐次逼近型 ADC 的电压参考设计》(《模拟对话》第 47 卷,第 2 期,2013 年)提供了有关 SAR ADC 参考设计的详细信息。

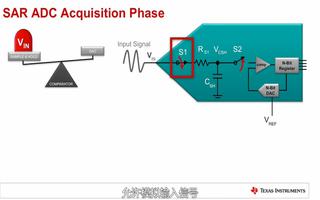

模拟输入建立时间

对于多通道、多路复用应用,驱动器放大器和ADC的模拟输入电路必须建立至16位电平(0.00076%),才能在内部电容阵列上进行满量程步进。遗憾的是,放大器数据手册通常规定建立至0.1%或0.01%电平。指定的建立时间可能与16位级别的建立时间有很大不同,因此在选择驱动器之前需要进行验证。

特别注意多路复用应用中的建立时间。多路复用器切换后,确保在转换开始之前留出足够的时间让模拟输入建立到指定的精度。将AD7606与多路复用器配合使用时,±10 V输入范围至少留出80 μs,±5 V输入范围至少留出88 μs,以使所选通道有足够的时间建立至16位分辨率。Alan Walsh 的《精密 SAR 模数转换器的前端放大器和 RC 滤波器设计》(《模拟对话》第 46 卷,第 4 期,2012 年)提供了有关放大器选择的更多详细信息。

模拟输入范围

确保模拟输入在指定的输入范围内,特别注意具有指定共模电压的差分输入范围,如图5所示。

图5.具有共模电压的全差分输入。

例如,AD7960 18位、5 MSPS SAR ADC的差分输入范围为–VREF至+VREF,但折合到地端的VIN+和VIN−均应在–0.1 V至VREF + 0.1 V范围内,共模电压应在VREF/2左右,如表1所示。

表 1.AD7960的模拟输入规格

| 参数 |

测试条件/ 注释 |

最小值 | 典型值 | Max | 单位 |

| 电压范围 | VIN+− VIN− | −V裁判 | +VREF | V | |

| 工作输入电压 | VIN+, VIN−到接地 | −0.1 | VREF + 0.1 | V | |

| 共模输入范围 | VREF/ 2 − 0.05 | VREF/2 | VREF/ 2 + 0.05 | V |

使SAR ADC退出省电或待机模式

为了节省功耗,一些SAR ADC在空闲时进入省电或待机模式。确保ADC在第一次转换开始之前退出此低功耗模式。例如,AD7606系列提供两种省电模式:完全关断和待机。这些模式由 GPIO 引脚 STBY 和 RANGE 控制。

图6显示,当STBY和RANGE恢复为高电平时,AD7606从完全关断模式进入正常模式,并配置为±10 V范围。此时,REGCAPA、REGCAPB 和 REGCAP 引脚将上电至数据手册中概述的正确电压。待机模式时,上电时间约为100 μs,但外部基准电压源模式下约为13 ms。当从关断模式上电时,必须在所需的上电时间过后施加RESET信号。数据手册规定了上电和复位上升沿之间所需的时间,如t唤醒关机.

图6.AD7606初始化时序

具有延迟延迟的SAR ADC

一种普遍的看法是,SAR ADC 没有延迟延迟,但某些 SAR ADC 具有配置更新的延迟延迟,因此在延迟延迟(可能是几个转换周期)过去之前,第一个有效的转换代码可能未定义。

例如,AD7985具有两种工作转换模式:睿频和正常。睿频模式可实现高达 2.5 MSPS 的最快转换速率,不会在两次转换之间掉电。涡轮模式下的第一次转换包含无意义的数据,应忽略。另一方面,在正常模式下,第一次转换是有意义的。

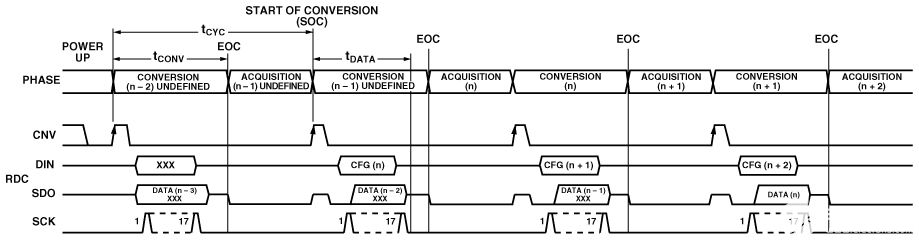

对于AD7682/AD7689,上电后的前三个转换结果尚未确定,因为直到第二个EOC之后才会进行有效配置。因此,需要两个虚拟转换,如图7所示。

图7.AD7682/AD7689的一般时序。

在硬件模式下使用AD765x-1时,RANGE引脚的逻辑状态在BUSY 信号的下降沿进行采样,以确定下一次同步转换的范围。经过有效的RESET脉冲后,AD765x-1默认工作在±4 × VREF范围内,没有延迟问题。但是,如果AD765x-1的工作电压范围为±2 × VREF范围,则必须使用一个虚拟转换周期来选择BUSY第一个下降沿的范围。

此外,一些SAR ADC(如过采样SAR ADC7766/AD7767)具有后数字滤波器,会导致额外的延迟延迟。当多路复用此类ADC的模拟输入时,主机必须等待完整的数字滤波器建立时间,才能获得有效的转换结果;在此建立时间之后,可以切换通道。

如表2所示,AD7766/AD7767的延迟为74除以输出数据速率(74/ODR)。以128 kHz的最大输出数据速率运行时,AD7766/AD7767支持1.729 kHz多路复用器开关速率。

表 2.AD7766/AD7767的数字滤波器延迟

| 参数 |

测试条件/ 注释 |

最小值 | 典型值 | 麦克斯 | 单位 |

| 组延迟 | 37/ODR | 微秒 | |||

| 建立时间(延迟) | 完全沉降 | 74/ODR | 微秒 |

数字接口时序

最后但并非最不重要的一点是,主机可以通过一些常见的接口选项访问SAR ADC的转换结果,例如菊花链模式下的并行、并行字节、IIC、SPI和SPI。要获得有效的转换数据,请确保遵循数据手册中的数字接口时序规格。

结论

要从SAR ADC获取第一个有效的转换代码,请遵循本文中讨论的建议。可能需要其他特定的配置支持;在第一个转换周期开始之前,请参阅目标SAR ADC数据手册或应用笔记进行初始化。

-

放大器

+关注

关注

143文章

13576浏览量

213341 -

滤波器

+关注

关注

161文章

7784浏览量

177955 -

adc

+关注

关注

98文章

6484浏览量

544407

发布评论请先 登录

相关推荐

逐次逼近型ADC:确保首次转换有效

初始化逐次逼近型ADC的有效转换

请问如何初始化逐次逼近型ADC以实现有效转换?

求助,逐次逼近型AD芯片的输入问题

逐次逼近型 ADC如何确保首次转换有效

逐次逼近型ADC:确保有效的首次转换

逐次逼近型ADC:确保有效的首次转换

评论