追求更小的 DRAM 单元尺寸(cell size)仍然很活跃并且正在进行中。对于 D12 节点,DRAM 单元尺寸预计接近 0.0013 um²。无论考虑使用 DUV 还是 EUV 光刻,图案化挑战都是重大的。特别是,ASML 报告说,当中心到中心(center-to-center)值达到 40 nm 时,即使对于 EUV ,也不推荐使用单一图案化。在本文中,我们将展示对于 12 纳米及更高节点的 DRAM 节点,电容器中心到中心预计将低于 40 纳米,因此需要多重图案化。

存储电容器的 DRAM 单元布局

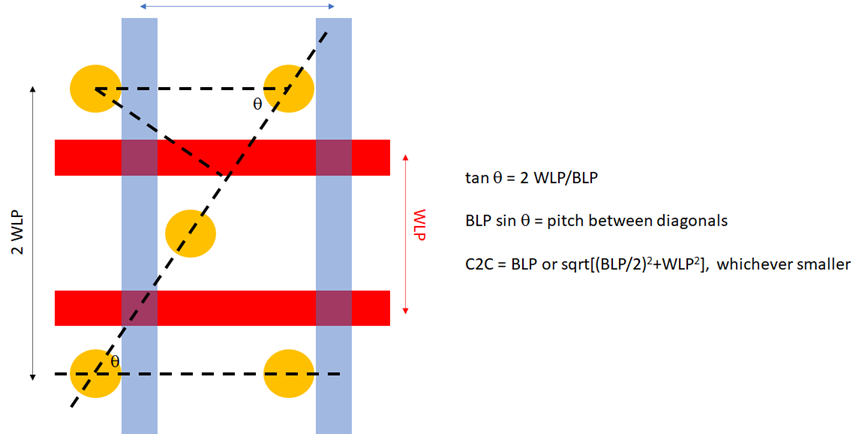

存储电容器排列成六边形阵列(图 1)。有源区设计规则由位线间距和字线间距决定。

图 1. DRAM 单元网格上的存储节点(黄色)。BLP=位线间距,WLP=字线间距。

对于 0.001254 um²的单元尺寸和略低于 12 nm 的有源区设计规则,38 nm 的位线间距和 33 nm 的字线间距将导致 38 nm 的中心到中心和 32.9 nm 的对角线间距。

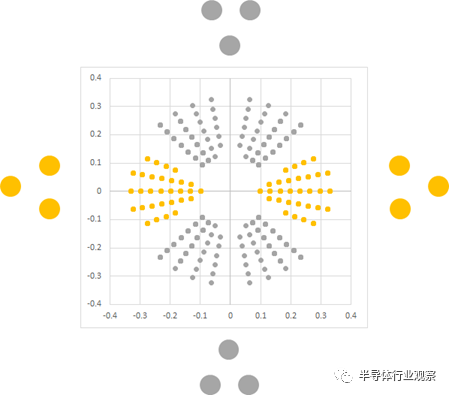

对于 0.33 NA EUV 系统,六边形阵列将使用六极照明(hexapole illumination),其中每个极产生三光束干涉图案(图 2)。四个象限极产生与其他两个水平极不同的模式。这导致具有独立随机性的两个独立剂量分量。这些被添加到最终的复合模式中。

图 2. DRAM 存储模式的六极照明由 4 个象限极(灰色)和两个水平极(黄色)组成。根据照明方向,生成的三光束干涉图案具有特定方向。

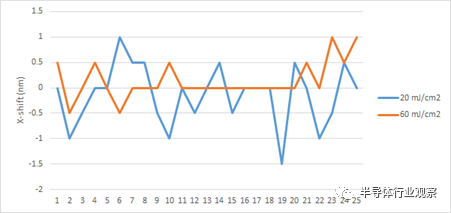

由于特征边缘处大量吸收的光子散粒噪声,图案放置误差的随机效应非常显着,正如参考文献中已经公开的那样。1,很容易超过 1 nm 的覆盖规格。较低的吸收剂量似乎明显更差(图 3)。

图 3. 38 nm x 66 nm cell(字线间距 = 33 nm)中中心柱的随机放置误差(仅 X),在 0.33 NA EUV 系统中具有预期的六极照明。这里显示了两个吸收剂量的一系列 25 个不同实例。

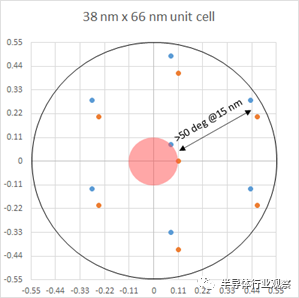

转到 0.55 NA 会增加焦点深度严重降低的问题。NA 为 0.55 会导致 15 nm 散焦,导致最内层和最外层衍射级之间的相移 >50 度(图 4),这会由于褪色严重降低图像对比度。

图 4. 0.55 NA EUV 系统上的 15 nm 散焦导致最内层和最外层衍射级之间的相移 >50 度。

因此,存储节点图案很可能需要由两个交叉线图案形成(图 5)。每个交叉线图案可以通过 EUV 单次曝光或 DUV SAQP(自对准四重图案)形成。两种选择都是单掩模工艺。SAQP 工艺更成熟(早于 EUV)并且没有 EUV 的二次电子随机问题,因此它应该是首选。尽管如此,对于 SAQP 情况,间隔线必须在布局和线宽粗糙度方面得到很好的控制。

图 5. 存储节点图案可以由两个交叉线图案的交叉点形成。

三星还展示了一种二维间隔蜂窝图案,而不是线型 SAQP,它使用具有起始蜂窝图案的单个掩膜,而不是具有起始线图案的两个掩膜。

虽然上述情况考虑了 38 nm 位线间距和 33 nm 字线间距,但由于六边形对称性,它也适用于交换间距的情况(33 nm 位线间距和 38 nm 字线间距)。

DRAM 技术,趋势和挑战

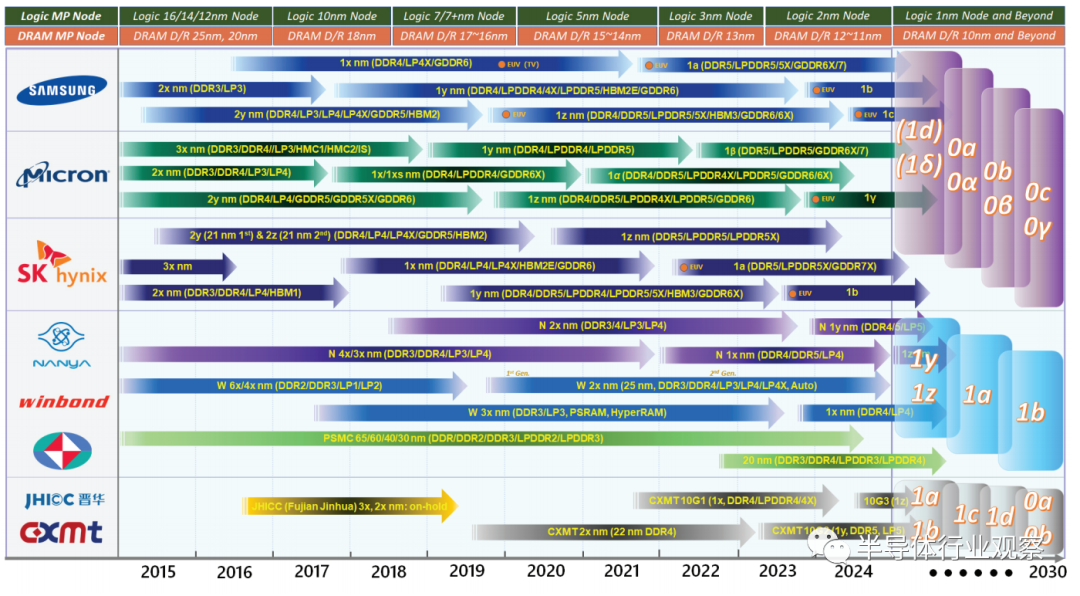

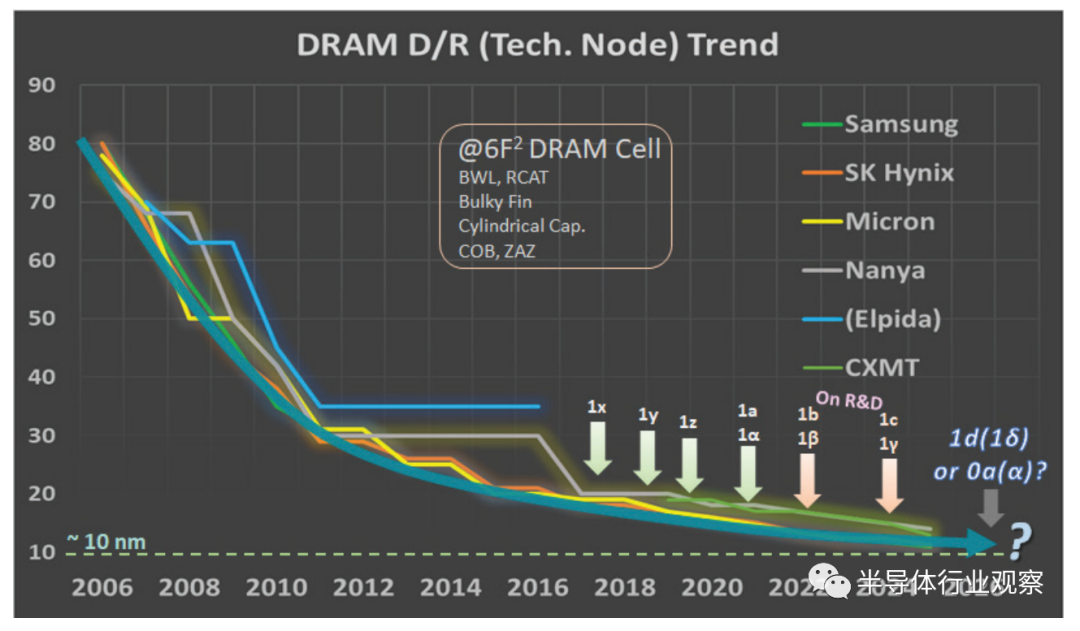

图 1 显示了来自三星, 美光, SK海力士,Nanya, PSMC, and CXMT厂商的 DRAM 路线图。三星、美光和 SK海力士三大厂商已经展示了适用于 DDR4、DDR5 和 LPDDR5 应用的具有 15nm 和 14nm 级单元设计规则 (D/R) 的 D1z 和 D1a 产品。三星已在 D1x DDR4 试用车(TV) 产品和 D1z LPDDR量产产品中采用 EUV 光刻技术,而美光和 SK 海力士则为 D1z 代保留了基于 ArF-i 的双图案化技术 (DPT) 工艺。到 2030 年,将生产出D1d(或 1δ)、D0a(或 0α)和 D0b(或 0β)等设计进一步缩小的几代 DRAM。

图 1.由TechInsights 提供的 DRAM 路线图,显示 2020 年至 2022 年市场上商业化的 D1z 和 D1a DRAM 产品。到 2030 年,将生产出D1d(或 1δ)、D0a(或 0α)和 D0b(或 0β)等几代产品。

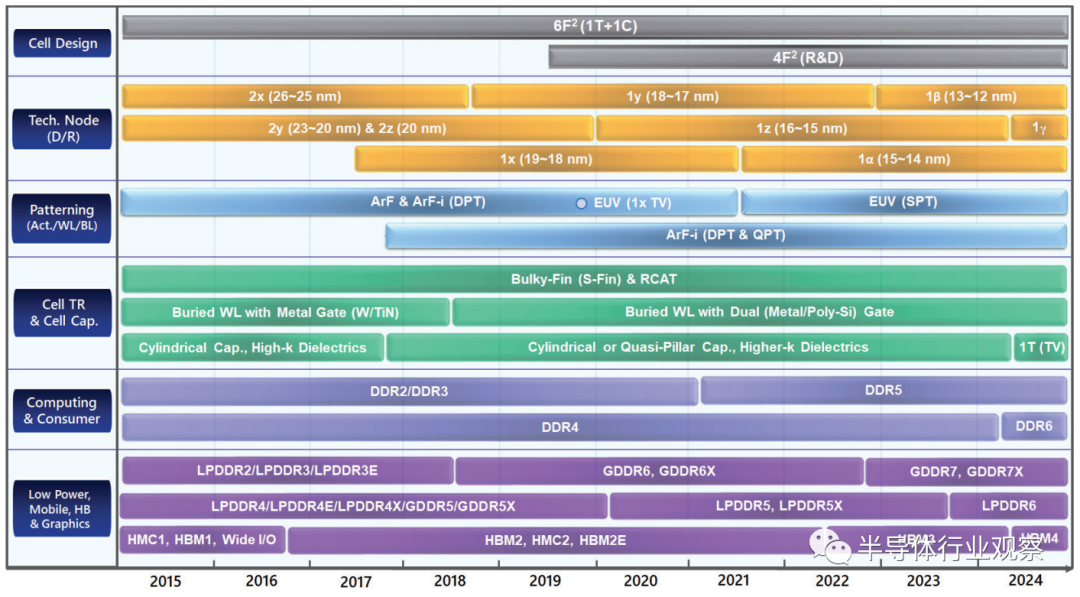

图 2. DRAM 设备的技术/应用路线图显示 6F2 1T+1C 单元设计扩展到更多下一代 DRAM,尽管 DRAM 厂商一直在开发 4F2 单元结构,例如 1T DRAM 或无电容器 DRAM 原型。

到目前为止,已经有了 8F2 和 6F2 DRAM 单元设计,其中单元包括 1T(晶体管)和 1C(电容器)。这种 1T+1C 单元设计将用于未来几代 DRAM 的 DRAM 单元设计。然而,由于工艺和布局的限制,DRAM 厂商一直在开发 4F2 单元结构,例如 1T DRAM 或无电容器 DRAM 原型,作为扩展 DRAM 技术的下一个候选者之一(图 2)。具有 B-RCAT 结构的大块鳍(或鞍鳍)用于单元存取晶体管,然而,掩埋字线栅极材料已经从单钨层变为多晶硅/钨双功函数层,以有效控制栅极泄漏。在这种情况下,具有较低功函数的多晶硅上栅极提高了 GIDL 电场 (30%) ,增大了扩散电阻。此外,美光使用纯 TiN 栅极进行 D1z 和 D1α 代单元集成。虽然圆柱型结构是DRAM单元电容器集成的主流,但SK海力士(D1y和D1z)和三星(D1z)采用了准柱状电容器(或单面柱状电容器)结构,其中单元电容器仅外表面呈圆柱状,这导致单元电容比上一代更小。几年后,DDR5、GDDR7、LPDDR6 和 HBM3 产品将在市场上普及。

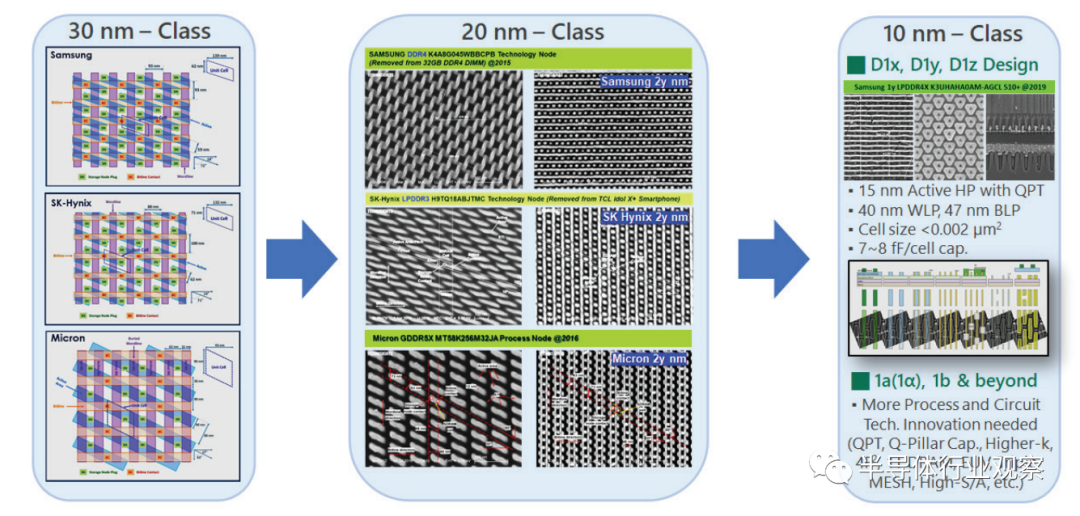

对于 10nm 级及以上的 DRAM 单元设计,应在其中加入更多创新的工艺、材料和电路技术,包括更高 NA EUV、4F2、1T DRAM、柱状电容器、超薄 high-k 电容器介质和低 -k ILD/IMD 材料(图 3)。

图 3. 从 30nm 级到 10nm 级的 DRAM 单元设计和技术趋势。需要更多创新技术来满足单元电容、尺寸缩小和提升速度的要求。

图 4 显示了主要厂商的 DRAM 设计规则 (D/R) 趋势。如果他们保持 6F2 DRAM 单元设计以及1T+1C 结构,2027 年或 2028 年 10nm D/R 将是DRAM 的最后一个节点。DRAM 单元微缩将面临若干挑战,例如 3D DRAM、减少row hammer(电路)、低功耗设计、刷新降低和管理刷新时间、低延迟、新功函数材料、HKMG 晶体管和片上 ECC。最受欢迎的功能将是“速度”和“感应裕量(sensing margin)”。三星用于 DDR5 和 GDDR6 的 HKMG 外围晶体管技术就是增加 BL 感应裕量和速度的一个例子。

图 4. DRAM D/R 趋势显示 6F2 单元设计的局限性。2027 年或 2028 年,10nm D/R 将是 6F2 DRAM 的最后一个节点。

-

电容器

+关注

关注

64文章

6308浏览量

100620 -

DRAM

+关注

关注

40文章

2337浏览量

184209 -

EUV

+关注

关注

8文章

609浏览量

86345

原文标题:DRAM制程

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是晶圆制程的CPK

DRAM与NAND闪存市场低迷,DRAM现货价格持续下滑

三星1c nm DRAM开发良率里程碑延期

三星重启1b nm DRAM设计,应对良率与性能挑战

DRAM的基本构造与工作原理

SRAM和DRAM有什么区别

DRAM存储器的基本单元

DRAM内存操作与时序解析

DRAM制程分享

DRAM制程分享

评论